## PEEL<sup>TM</sup> 18CV8Z-25 CMOS Programmable Electrically Erasable Logic Device

## **Features**

## **Ultra Low Power Operation**

- Vcc = 5 Volts  $\pm 10\%$

- Icc =  $10 \mu A$  (typical) at standby

- Icc = 2 mA (typical) at 1 MHz

#### **CMOS Electrically Erasable Technology**

- Superior factory testing

- Reprogrammable in plastic package

- Reduces retrofit and development costs

#### **Application Versatility**

- Replaces random logic

- Super set of standard PLDs

- Pin and JEDEC compatible with 16V8

- Ideal for use in power-sensitive systems

#### **Architectural Flexibility**

- Enhanced architecture fits in more logic

- 113 product terms x 36 input AND array

- 10 inputs and 8 I/O pins

- 12 possible macrocell configurations

- Asynchronous clear, Synchronous preset

- Independent output enables

- Programmable clock; pin 1 or p-term

- Programmable clock polarity

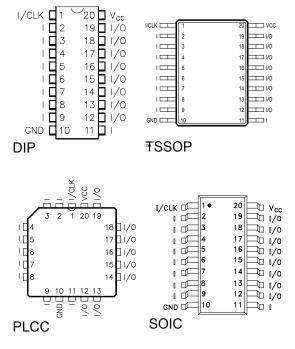

- 20 Pin DIP/SOIC/TSSOP and PLCC

## **General Description**

The PEEL<sup>TM</sup>18CV8Z is a Programmable Electrically Erasable Logic (PEEL<sup>TM</sup>) SPLD (Simple Programmable Logic Device) that features ultra-low, automatic "zero" power-down operation. The "zero power" (100 μA max. Icc) power-down mode makes the PEEL<sup>TM</sup>18CV8Z ideal for a broad range of battery-powered portable equipment applications, from hand-held meters to PCM-CIA modems. EE-reprogrammability provides both the convenience of fast reprogramming for product development and quick product personalization in manufacturing, including Engineering Change Orders.

Figure 7 Pin Configuration

The PEEL<sup>TM</sup>18CV8Z is logically and functionally similar to Anachip's 5 Volt PEEL<sup>TM</sup>18CV8 and 3 Volt PEEL<sup>TM</sup>18LV8Z. The differences between the PEEL<sup>TM</sup>18CV8Z and PEEL<sup>TM</sup>18CV8 include the addition of programmable clock polarity, a product term clock, and variable width product terms in the AND/OR Logic Array.

Like the PEEL<sup>TM</sup>18CV8, the PEEL<sup>TM</sup>18CV8Z is logical superset of the industry standard PAL16V8 SPLD. The PEEL<sup>TM</sup>18CV8Z provides additional architectural features that allow more logic to be incorporated into the design. Anachip's JEDEC file translator allows easy conversion of existing 20 pin PLD designs to the PEEL<sup>TM</sup>18CV8Z architecture without the need for redesign. The PEEL<sup>TM</sup>18CV8Z architecture allows it to replace over twenty standard 20-pin DIP, SOIC, TSSOP and PLCC packages.

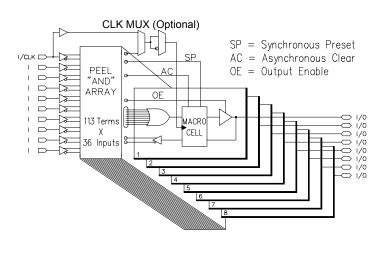

Figure 8 Block Diagram

This datasheet contains new product information. Anachip Corp. reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

Rev. 1.0 Dec 16, 2004

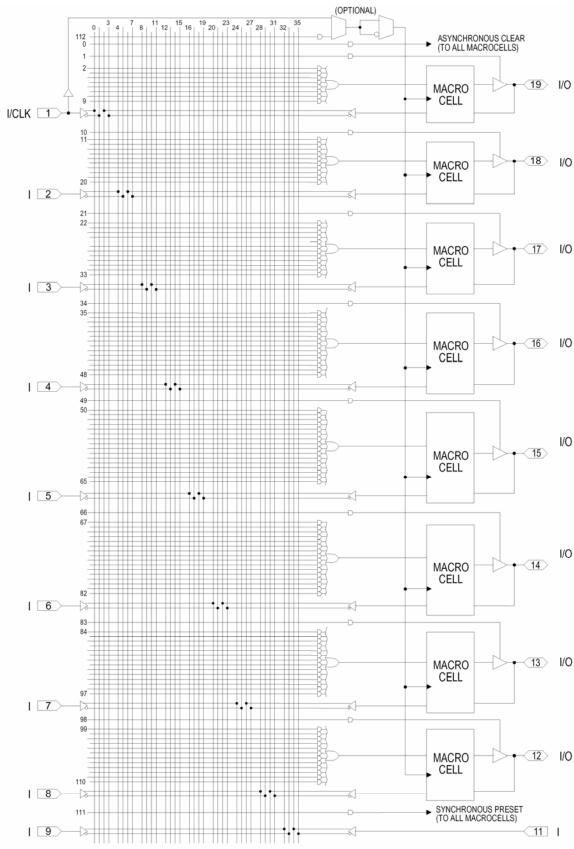

Figure 9 PEEL™18CV8Z Logic Array Diagram

## **Function Description**

The PEELTM18CV8Z implements logic functions as sum-of-products expressions in a programmable-AND/fixed-OR logic array. User-defined functions are created by programming the connections of input signals into the array. User-configurable output structures in the form of I/O macrocells further increase logic flexibility.

#### **Architecture Overview**

The PEEL<sup>TM</sup>18CV8Z architecture is illustrated in the block diagram of Figure 8. Ten dedicated inputs and 8 I/Os provide up to 18 inputs and 8 outputs for creation of logic functions. At the core of the device is a programmable electrically-erasable AND array that drives a fixed OR array. With this structure, the PEEL<sup>TM</sup>18CV8Z can implement up to eight sum-of-products logic expressions.

Associated with each of the eight OR functions is an I/O macrocell that can be independently programmed to one of 12 different configurations. The programmable macrocells allow each I/O to be used to create sequential or combinatorial logic functions of active-high or active-low polarity, while providing three different feedback paths into the AND array.

## **AND/OR Logic Array**

The programmable AND array of the PEEL<sup>TM</sup>18CV8Z (shown in Figure 9) is formed by input lines intersecting product terms. The input lines and product terms are used as follows:

## 36 Input Lines:

- 20 input lines carry the true and complement of the signals applied to the 10 input pins

- 16 additional lines carry the true and complement values of feedback or input signals from the 8 I/Os

#### 113 product terms:

- 102 product terms are used to form sum of product functions

- − 8 output enable terms (one for each I/O)

- 1 global synchronous preset term

- 1 global asynchronous clear term

- 1 programmable clock term

At each input-line/product-term intersection, there is an EEPROM memory cell that determines whether or not there is a logical connection at that intersection. Each product term is essentially a 36-input AND gate. A product term that is connected to both the true and complement of an input signal will always be FALSE and thus will not affect the OR function that it drives. When all the connections on a product term are opened, a "don't care" state exists and that term will always be TRUE. When programming the PEEL<sup>TM</sup>18CV8Z, the device program-mer first performs a bulk erase to remove the previous pattern. The erase cycle opens every logical connection in the array. The device is configured to perform the user-defined function by pro- gramming selected connections in the AND array. (Note that PEEL<sup>TM</sup> device programmers automatically program all of the connections on unused product terms so that they will have no

effect on the output function).

#### **Variable Product Term Distribution**

The PEEL<sup>TM</sup>18CV8Z provides 113 product terms to drive the eight OR functions. These product terms are distributed among the outputs in groups of 8, 10, 12, 14, and 16 to form logical sums (see Figure 9). This distribution allows optimum use of the device resources.

## Programmable I/O Macrocell

The unique twelve-configuration output macrocell provides complete control over the architecture of each output. The ability to configure each output independently lets you to tailor the configuration of the PEEL<sup>TM</sup>18CV8Z to the precise requirements of your design.

#### **Macrocell Architecture**

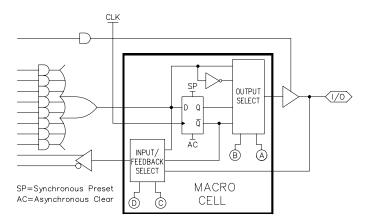

Each I/O macrocell, as shown in Figure 9, consists of a D-type flip-flop and two signal-select multiplexers. The configuration of each macrocell is determined by the four EEPROM bits controlling these multiplexers. These bits determine output polarity, output type (registered or non-registered) and input-feedback path (bidirectional I/O, combinatorial feedback). Refer to Table 1 for details.

Equivalent circuits for the twelve macrocell configurations are illustrated in Figure 11. In addition to emulating the four PAL-type output structures (configurations 3, 4, 9, and 10), the macrocell provides eight additional configurations. When creating a PEEL<sup>TM</sup> device design, the desired macrocell configuration is generally specified explicitly in the design file. When the design is assembled or compiled, the macrocell configuration bits are defined in the last lines of the JEDEC programming file.

#### **Output Type**

The signal from the OR array can be fed directly to the output pin (combinatorial function) or latched in the D-type flip-flop (registered function). The D-type flip-flop latches data on the rising edge of the clock and is controlled by the global preset and clear terms. When the synchronous preset term is satisfied, the Q output of the register is set HIGH at the next rising edge of the clock input. Satisfying the asynchronous clear sets Q LOW, regardless of the clock state. If both terms are satisfied simultaneously, the clear will override the preset.

#### **Output Polarity**

Each macrocell can be configured to implement active-high or active-low logic. Programmable polarity eliminates the need for external inverters.

#### **Output Enable**

The output of each I/O macrocell can be enabled or disabled under the control of its associated programmable output enable product term. When the logical conditions programmed on the output enable term are satisfied, the output signal is propagated to

the I/O pin. Otherwise, the output buffer is switched into the high-impedance state.

Under the control of the output enable term, the I/O pin can function as a dedicated input, a dedicated output, or a bi-directional I/O. Opening every connection on the output enable term will permanently enable the output buffer and yield a dedicated output. Conversely, if every connection is intact, the enable term will always be logically false and the I/O will function as a dedicated input.

## Input/Feedback Select

The PEEL<sup>TM</sup>18CV8Z macrocell also provides control over the feedback path. The input/feedback signal associated with each I/O macrocell can be obtained from three different locations; from the I/O input pin, from the Q output of the flip-flop (registered feedback), or directly from the OR gate (combinatorial feedback).

## Bi-directional I/O

The input/feedback signal is taken from the I/O pin when using the pin as a dedicated input or as a bi-directional I/O. (Note that it is possible to create a registered output function with a bi-directional I/O, refer to Figure 9).

#### **Combinatorial Feedback**

The signal-select multiplexer gives the macrocell the ability to feedback the output of the OR gate, bypassing the output buffer, regardless of whether the output function is registered or combinatorial. This feature allows the creation of asynchronous latches, even when the output must be disabled. (Refer to configurations 5, 6, 7, and 8 in Figure 11.)

# Figure 9 Block Diagram of the PEEL<sup>TM</sup>18CV8Z I/O Macrocell

#### **Registered Feedback**

Feedback also can be taken from the register, regardless of whether the output function is programmed to be combinatorial or registered. When implementing a combinatorial output func-

tion, registered feedback allows for the internal latching of states without giving up the use of the external output.

## **Programmable Clock Options**

A unique feature of the PEEL<sup>TM</sup>18CV8Z is a programmable clock multiplexer that allows the user to select true or complement forms of either input pin or product-term clock sources.

#### **Zero Power Feature**

The CMOS PEEL<sup>TM</sup>18CV8Z features "Zero-Power" standby operation for ultra-low power consumption. With the "Zero-Power" feature, transition-detection circuitry monitors the inputs, I/Os (including CLK) and feedbacks. If these signals do not change for a period of time greater than approximately two tpd's, the outputs are latched in their current state and the device automatically powers down. When the next signal transition is detected, the device will "wake up" for active operation until the signals stop switching long enough to trigger the next powerdown. (Note that the tPD is approximately 5 ns. slower on the first transition from sleep mode.)

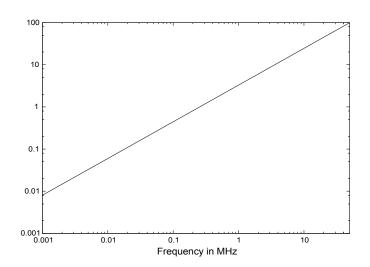

As a result of the "Zero-Power" feature, significant power savings can be realized for combinatorial or sequential operations when the inputs or clock change at a modest rate. See Figure 5.

Figure 10 Typical ICC vs. Input Clock Frequency for the 18CV8Z

|                | REGISTER OUTPUT                         | COMBINATORIAL OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | L           |

|----------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| ONAL 1/0       | 1 O O O O O O O O O O O O O O O O O O O | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ACTIVE LOW  |

| BI-DIRECTIONAL | 2                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ACTIVE HIGH |

| AL FEEDBACK    | 5                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ACTIVE LOW  |

| COMBINATORIAL  | 6 SP 1/0                                | 8 P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ACTIVE HIGH |

| FEEDBACK       | 9 SP 1/0                                | 111 - SP - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1/0 - 1 | ACTIVE LOW  |

| REGISTER       | 10 SP I/O                               | 12 SP 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ACTIVE HIGH |

| Configuration |   |   |   | Input/Feedback Select | Output Salaat          |                                 |             |

|---------------|---|---|---|-----------------------|------------------------|---------------------------------|-------------|

| #             | A | В | C | D                     | Input/reeuback Select  | Output Select                   |             |

| 1             | 0 | 0 | 1 | 0                     |                        | Register                        | Active Low  |

| 2             | 1 | 0 | 1 | 0                     | Bi-directional I/O     | Register                        | Active High |

| 3             | 0 | 1 | 0 | 0                     | Bi-directional I/O     | Combinatorial                   | Active Low  |

| 4             | 1 | 1 | 0 | 0                     |                        | Comomatoriai                    | Active High |

| 5             | 0 | 0 | 1 | 1                     |                        | Danistan                        | Active Low  |

| 6             | 1 | 0 | 1 | 1                     | Combinatorial Feedback | Register                        | Active High |

| 7             | 0 | 1 | 1 | 1                     | Combinatorial Feedback | Combinatorial                   | Active Low  |

| 8             | 1 | 1 | 1 | 1                     | Combinatorial          |                                 | Active High |

| 9             | 0 | 0 | 0 | 0                     |                        | Dagistar                        | Active Low  |

| 10            | 1 | 0 | 0 | 0                     | Register               |                                 | Active High |

| 11            | 0 | 1 | 1 | 0                     | Register reedback      | Register Feedback Combinatorial |             |

| 12            | 1 | 1 | 1 | 0                     |                        | Comomatoriai                    | Active High |

## **Design Security**

The PEELTM18CV8Z provides a special EEPROM security bit that prevents unauthorized reading or copying of designs programmed into the device. The security bit is set by the PLD programmer, either at the conclusion of the programming cycle or as a separate step, after the device has been programmed. Once the security bit is set it is impossible to verify (read) or program the PEELTM until the entire device has first been erased with the bulk-erase function.

## Signature Word

The signature word feature allows a 64-bit code to be programmed into the PEEL<sup>TM</sup>18CV8Z if the software option is used. The code can be read back even after the security bit has been set. The signature word can be used to identify the pattern programmed into the device or to record the design revision, etc.

## **Programming Support**

Anachip's JEDEC file translator allows easy conversion of existing 20 pin PLD designs to the PEEL<sup>TM</sup>18CV8Z, without the need for redesign. Anachip also offers (for free) its proprietary Win-PLACE software, an easy-to-use entry level PC-based software development system.

Programming support includes all the popular third party programmers such as BP Microsystems, System General, Logical Devices, and numerous others.

This device has been designed and tested for the specified operating ranges. Improper operation outside of these levels is not guaranteed. Exposure to absolute maximum ratings may cause permanent damage.

**Absolute Maximum Ratings**

| Symbol                 | Parameter                               | Conditions                                   | Rating                       | Unit |

|------------------------|-----------------------------------------|----------------------------------------------|------------------------------|------|

| $V_{\rm CC}$           | Supply Voltage                          | Relative to Ground                           | -0.5 to +7.0                 | V    |

| $V_{\rm I}, V_{\rm O}$ | Voltage Applied to Any Pin <sup>2</sup> | Relative to Ground <sup>1</sup>              | -0.5 to V <sub>CC</sub> +0.6 | V    |

| $I_{O}$                | Output Current                          | Per Pin (I <sub>OL</sub> , I <sub>OH</sub> ) | ±25                          | mA   |

| $T_{ST}$               | Storage Temperature                     |                                              | -65 to +150                  | °C   |

| $T_{LT}$               | Lead Temperature                        | Soldering 10 Seconds                         | +300                         | °C   |

**Operating Range**

| Symbol           | Parameter                 | Conditions  | Min  | Max  | Unit |

|------------------|---------------------------|-------------|------|------|------|

| V <sub>CC</sub>  | Supply Voltage            | Commercial  | 4.75 | 5.25 | V    |

| V CC             | Supply Voltage            | Industrial  | 4.5  | 5.5  | V    |

| $T_{A}$          | Ambient Temperature       | Commercial  | 0    | +70  | °C   |

| 1 A              |                           | Industrial  | -40  | +85  | °C   |

| $T_R$            | Clock Rise Time           | See Note 3. |      | 20   | ns   |

| $T_{\mathrm{F}}$ | Clock Fall Time           | See Note 3. |      | 20   | ns   |

| $T_{RVCC}$       | V <sub>CC</sub> Rise Time | See Note 3. |      | 250  | ms   |

**D.C. Electrical Characteristics** Over the operating range (Unless otherwise specified)

| Symbol            | Parameter                        | Conditions                                                    | Min                  | Max                  | Unit |

|-------------------|----------------------------------|---------------------------------------------------------------|----------------------|----------------------|------|

| $ m V_{OH}$       | Output HIGH Voltage – TTL        | $V_{CC} = Min$ , $I_{OH} = -4.0 \text{ mA}$                   | 2.4                  |                      | V    |

| $V_{ m OHC}$      | Output HIGH Voltage – CMOS       | $V_{CC} = Min, I_{OH} = -10.0 \mu A$                          | V <sub>CC</sub> -0.3 |                      | V    |

| $V_{ m OL}$       | Output LOW Voltage – TTL         | $V_{CC} = Min$ , $I_{OL} = 16.0 \text{ mA}$                   |                      | 0.5                  | V    |

| $V_{ m OLC}$      | Output LOW Voltage – CMOS        | $V_{CC} = Min$ , $I_{OL} = 10.0 \mu A$                        |                      | 0.15                 | V    |

| $V_{ m IH}$       | Input HIGH Voltage               |                                                               | 2.0                  | V <sub>CC</sub> +0.3 | V    |

| $V_{ m IL}$       | Input LOW Voltage                |                                                               | -0.3                 | 0.8                  | V    |

| ${ m I}_{ m IL}$  | Input and I/O Leakage Current    | $V_{CC}$ =Max, $GND \le V_{IN} \le V_{CC}$ , $I/O = High Z$   |                      | ±10                  | μΑ   |

| $I_{SC}^{9}$      | Output Short Circuit Current     | $V_{CC} = Max, V_O = 0.5V, T_A = 25^{\circ}C$                 | -30                  | -135                 | mA   |

| $I_{CCS}$         | V <sub>CC</sub> Current, Standby | $V_{IN} = 0V$ or $V_{CC}$ , All Outputs disabled <sup>4</sup> | 10 (typ)             | 100                  | μΑ   |

| $I_{\rm CC}^{10}$ | V <sub>CC</sub> Current, f=1MHz  | $V_{IN} = 0V$ or $V_{CC}$ , All Outputs disabled <sup>4</sup> | 2 (typ)              | 5                    | mA   |

| ${\rm C_{IN}}^7$  | Input Capacitance                | $T_A = 25^{\circ}C, V_{CC} = Max \ (20, f = 1 MHz)$           |                      | 6                    | pF   |

| $C_{OUT}^{7}$     | Output Capacitance               | $1_A - 25$ C, $v_{CC} - \text{Ividx}$ ( $w$ ) $1 - 1$ MITIZ   |                      | 12                   | pF   |

| Cymbol                  | Davamatav                                                      | -25  | -25 / I-25 |       |  |

|-------------------------|----------------------------------------------------------------|------|------------|-------|--|

| Symbol                  | Parameter                                                      | Min  | Max        | Units |  |

| $t_{ m PD}$             | Input <sup>5</sup> to non-registered output                    |      | 25         | ns    |  |

| $t_{ m OE}$             | Input <sup>5</sup> to output enable <sup>6</sup>               |      | 25         | ns    |  |

| $t_{\mathrm{OD}}$       | Input <sup>5</sup> to output disable <sup>6</sup>              |      | 25         | ns    |  |

| $t_{CO1}$               | Clock to Output                                                |      | 15         | ns    |  |

| $t_{\rm CO2}$           | Clock to comb. output delay via internal registered feedback   |      | 35         | ns    |  |

| $t_{\mathrm{CF}}$       | Clock to Feedback                                              |      | 9          | ns    |  |

| $t_{ m SC}$             | Input <sup>5</sup> or feedback setup to clock                  | 15   |            | ns    |  |

| $t_{ m HC}$             | Input <sup>5</sup> hold after clock                            | 0    |            | ns    |  |

| $t_{\rm CL},t_{\rm CH}$ | Clock low time, clock high time <sup>8</sup>                   | 13   |            | ns    |  |

| $t_{\mathrm{CP}}$       | Min clock period Ext $(t_{SC} + t_{CO1})$                      | 30   |            | ns    |  |

| $f_{MAX1}$              | Internal feedback $(1/t_{SC} + t_{CF})^{11}$                   | 41.6 |            | MHz   |  |

| $f_{MAX2}$              | External feedback $(1/t_{CP})^{11}$                            | 33.3 |            | MHz   |  |

| $f_{MAX3}$              | No feedback $(1/t_{CL} + t_{CH})^{11}$                         | 38.4 |            | MHz   |  |

| $t_{ m AW}$             | Asynchronous Reset Pulse Width                                 | 25   |            | ns    |  |

| $t_{AP}$                | Input <sup>5</sup> to Asynchronous Reset                       |      | 25         | ns    |  |

| $t_{AR}$                | Asynchronous Reset recovery time                               |      | 25         | ns    |  |

| $t_{ m RESET}$          | Power-on reset time for registers in clear state <sup>12</sup> |      | 5          | μs    |  |

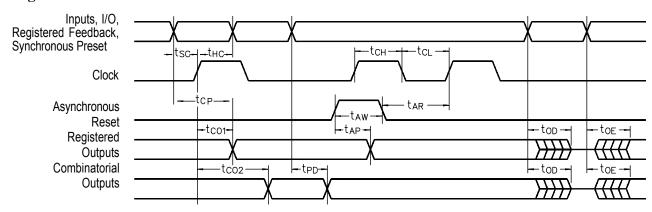

## **Switching Waveforms**

#### Notes:

- 1. Minimum DC input is -0.5V, however, inputs may undershoot to -2.0V for periods less than 20 ns.

- 2. VI and VO are not specified for program/verify operation.

- 3. Test Points for Clock and VCC in  $\ensuremath{\text{tr}}$  are referenced at the 10% and 90% levels.

- 4. I/O pins are 0V and VCC.

- 5. "Input" refers to an input pin signal.

- 6. tOE is measured from input transition to VREF±0.1V,

TOD is measured from input transition to VOH-0.1V or VOL+0.1V; VREF=VL.

7. Capacitances are tested on a sample basis.

- 8. Test conditions assume: signal transition times of 3ns or less from the 10% and 90% points, timing reference levels of 1.5V (Unless otherwise specified).

- 9. Test one output at a time for a duration of less than 1 second.

- 10. ICC for a typical application: This parameter is tested with the device programmed as an 8-bit Counter.

- 11. Parameters are not 100% tested. Specifications are based on initial characterization and are tested after any design process modification that might affect operational frequency.

- 12. All input at GND.

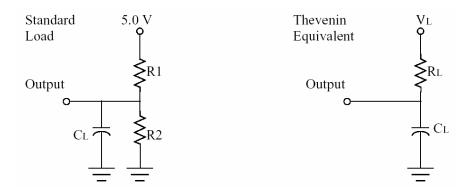

## PEEL<sup>TM</sup> Device and Array Test Loads

| Technology | R1    | R2    | $R_{ m L}$  | $ m V_L$ | $C_{\mathrm{L}}$ |

|------------|-------|-------|-------------|----------|------------------|

| CMOS       | 480kΩ | 480kΩ | $228\Omega$ | 2.375V   | 33 pF            |

| TTL        | 235Ω  | 159Ω  | 95Ω         | 2.02V    | 33 pF            |

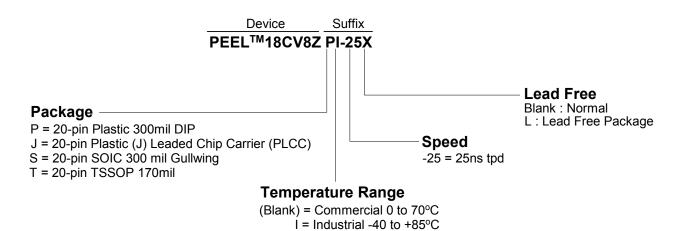

## **Ordering Information**

| Part Number         | Speed | Temperature | Package            |

|---------------------|-------|-------------|--------------------|

| PEEL18CV8ZP-25 (L)  | 25ns  | Commercial  | 20-pin Plastic DIP |

| PEEL18CV8ZJ-25 (L)  | 25ns  | Commercial  | 20-pin PLCC        |

| PEEL18CV8ZS-25 (L)  | 25ns  | Commercial  | 20-pin SOIC        |

| PEEL18CV8ZT-25 (L)  | 25ns  | Commercial  | 20-pin TSSOP       |

| PEEL18CV8ZPI-25 (L) | 25ns  | Industrial  | 20-pin Plastic DIP |

| PEEL18CV8ZJI-25 (L) | 25ns  | Industrial  | 20-pin PLCC        |

| PEEL18CV8ZSI-25 (L) | 25ns  | Industrial  | 20-pin SOIC        |

| PEEL18CV8ZTI-25 (L) | 25ns  | Industrial  | 20-pin TSSOP       |

## Part Number

Anachip Corp. Head Office, 2F, No. 24-2, Industry E. Rd. IV, Science-Based Industrial Park, Hsinchu, 300, Taiwan

Tel: +886-3-5678234 Fax: +886-3-5678368

Email: <a href="mailto:sales\_usa@anachip.com">sales\_usa@anachip.com</a>

Website: <a href="http://www.anachip.com">http://www.anachip.com</a>

©2004 Anachip Corp.

Anachip USA 780 Montague Expressway, #201 San Jose, CA 95131 Tel: (408) 321-9600

Fax: (408) 321-9696

Anachip reserves the right to make changes in specifications at any time and without notice. The information furnished by Anachip in this publication is believed to be accurate and reliable. However, there is no responsibility assumed by Anachip for its use nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Anachip. Anachip's products are not authorized for use as critical components in life support devices or systems.

Marks bearing © or TM are registered trademarks and trademarks of Anachip Corp.

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научно-исследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

**Телефон:** +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331