**Product Data Sheet**

**Industrial SDHC Memory Card**

S-40 Series

Industrial Card

# S-40 SERIES

## INDUSTRIAL SDHC MEMORY CARD - 4/8/16/32GBYTE

### Main Feature

- o Fully compliant with SD Memory Card specification 2.0 and 3.0 SD mode and SPI mode supported

- Speed class 6 according SD3.0 specification

- FAT32 preformatted

- High performance 3.0 specification

- o SD burst up to 25MB/s

- SD Normal speed o...25MHz clock rate

- o SD High speed 25...50MHz clock rate

- o Flash burst up to 90MB/s

- Up to 24MByte/sec sequential data rate

- Power Supply: (Low-power CMOS technology)

- o 2.7...3.6V normal operating voltage

- o 2.0...3.6V basic communication (CMDo, 15, 55 ACMD41) voltage

- Standard SD Memory card form factor

- o 32.0mm x 24.0mm x 2.1mm and Write Protect slider

- Optimized FW algorithms especially for high read access and long data retention applications

- Patented power-off reliability technology

- Wear Leveling technology

- Equal wear leveling of static and dynamic data. The wear leveling assures that dynamic data as well as static data is balanced evenly across the memory. With that the maximum write endurance of the device is guaranteed

- Write Endurance technology

- Due to intelligent wear leveling an even use of the entire flash is guaranteed, regardless how much "static" (OS) data is stored.

- o Read Disturb Management

- The read commands are monitored and the content is refreshed when critical levels have occurred

- Auto Refresh for Data Retention enhancement

- The interruptible background process maintain the user data for Read Disturb effects or Retention degradation due to high temperature effects

- Near miss ECC technology

- Minimize the risk of uncorrectable bit failure over the product life time. Each read command analyzes the ECC margin level and refresh data if necessarv

- o Diagnostic features with Life Time Monitoring tool support

- High reliability

- o Designed for industrial market especially read intensive application like navigation, infotainment, POS/POI, Medical and general boot medium use case:

- The product is optimized for long life cycle that require a good data retention because of high temperature mission profile.

- o Intensive write application should use the S-450 Series SLC cards

- Number of card insertions/removals up to 20,000

- Extended Temperature range -25° up to 85°C (optional -40° up to 85°C)

- o SIP (System In Package) process for extreme dust, water and ESD proof

- Controlled BOM & PCN process

- Customized options like CID registers, CPRM keys, firmware incl. settings and marking by projects

## 1 Order Information

### 1.1 Standard product list

Table 1: Standard Product List

| Density | Part Number                  | Temp. Range   | Flash Technology |

|---------|------------------------------|---------------|------------------|

| 4GB     | SFSD4096LgBM1TO-t-GE-1x1-STD | 25%C +0 05%C  |                  |

| 8GB     | SFSD8192LgBM1TO-t-GE-1x1-STD | -25°C to 85°C | MLC NAND Flash   |

| 16GB    | SFSD016GLgBM1TO-t-LF-1x1-STD | -40°C to 85°C | MIC NAND FIRST   |

| 32GB    | SFSD032GLgBM1TO-t-HG-1x1-STD | -40 C to 85 C |                  |

g defines the product generation

### 1.2 Current product generation

Table 2: Standard Product List

| Density | Part Number                  | Temp. Range   | Flash Technology |

|---------|------------------------------|---------------|------------------|

| 4GB     | SFSD4096L1BM1TO-E-GE-111-STD |               |                  |

| 8GB     | SFSD8192L1BM1TO-E-GE-111-STD | 25% to 85%    |                  |

| 16GB    | SFSD016GL1BM1TO-E-LF-111-STD | -25°C to 85°C | MLC NAND Flash   |

| 32GB    | SFSD032GL1BM1TO-E-HG-111-STD |               |                  |

| 4GB     | SFSD4096L1BM1TO-I-GE-111-STD |               | MIC NAND FIGST   |

| 8GB     | SFSD8192L1BM1TO-I-GE-111-STD | 1 00C to 050C |                  |

| 16GB    | SFSD016GL1BM1TO-I-LF-111-STD | -40°C to 85°C |                  |

| 32GB    | SFSD032GL1BM1TO-I-HG-111-STD |               |                  |

x defines the FW

t defines the temperature range (E=-25°C to +85°C, I=-40°C to +85°C)

# **2** Contents

| MAIN FEATURE                           | 2  |

|----------------------------------------|----|

| 1 ORDER INFORMATION                    | 3  |

| 1.1 Standard product list              | 3  |

| 1.2 Current product generation         | 3  |

| 2 CONTENTS                             | 4  |

| 3 PRODUCT SPECIFICATION                | 5  |

| 3.1 System Performance                 | 5  |

| 3.2 ENVIRONMENTAL SPECIFICATIONS       |    |

| 3.2.1 Recommended Operating Conditions |    |

| 3.2.2 Recommended Storage Conditions   |    |

| 3.2.4 Environmental Conditions         |    |

| 3.3 Physical Dimensions                |    |

| 3.4 RELIABILITY                        |    |

| 4 CAPACITY SPECIFICATION               | 7  |

| 5 CARD PHYSICAL                        | 7  |

| 5.1 Physical description               | 7  |

| 6 ELECTRICAL INTERFACE                 | 9  |

| 6.1 ELECTRICAL DESCRIPTION             | 9  |

| 6.2 DC CHARACTERISTICS                 |    |

| 6.3 Signal Loading                     |    |

| 6.4 AC CHARACTERISTICS                 |    |

| 6.4.2 High Speed mode (0 – 50MHz)      |    |

| 7 HOST ACCESS SPECIFICATION            |    |

| 7.1 SD AND SPI Bus Modes               |    |

| 7.1.1 SD Bus Mode Protocol             |    |

| 7.1.2 SPI Bus Mode Protocol            |    |

| 7.1.3 Mode Selection                   |    |

| 7.2 CARD REGISTERS                     | 16 |

| 8 ROHS AND WEEE UPDATE FROM SWISSBIT   | 20 |

| 9 PART NUMBER DECODER                  | 22 |

| 10 SWISSBIT LABEL SPECIFICATION        | 24 |

| 10.1 Front side label                  | 24 |

| 10.2 Back side marking                 | 24 |

| 44 DEVICION HICTORY                    | 25 |

## **3 Product Specification**

The SD Memory Card is a small form factor non-volatile memory card which provides high capacity data storage. Its aim is to capture, retain and transport data, audio and images, facilitating the transfer of all types of digital information between a large variety of digital systems.

The card operates in two basic modes:

- SD/SDHC card mode

- SPI mode

The SD Memory Card also supports SD High Speed mode with up to 50MHz clock frequency.

The cards are compliant with

- SD Memory card Specification Part 1, Physical layer Specification V3.01

- SD Memory card Specification Part 2, File System Specification V3.00

- SD Memory card Specification Part 3, Security Specification V3.00

- SD Memory Card Addendum V4.oo

Simplified specifications are available at <a href="https://www.sdcard.org/downloads/pls/simplified\_specs/">https://www.sdcard.org/downloads/pls/simplified\_specs/</a>

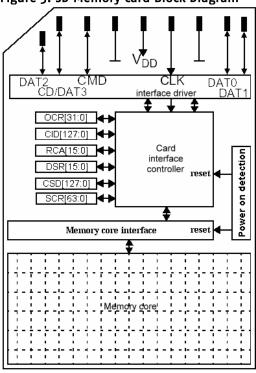

The Card has an internal **intelligent controller** which manages interface protocols, data storage and retrieval as well as hardware **BCH Error Correction Code (ECC)**, **defect handling**, **diagnostics and clock control**. The **advanced wear leveling** mechanism assures an equal usage of the Flash memory cells to extend the life

The hardware BCH-code ECC allows to detect and correct up to 40 defect bits per 1kByte.

The controller performs control read operations and checks the consistence of the data. If an error of some bits is detected, the card refresh all data in the flash cells to prevent data retention problems.

The card is optimized for applications

The card has a **power-loss management feature** to prevent data corruption after power-down.

The cards are RoHS compliant and lead-free.

#### 3.1 System Performance

#### Table 3: Performance

| System Performance                    | typ    | max                  | Unit                 |      |

|---------------------------------------|--------|----------------------|----------------------|------|

| Burst Data transfer Rate (max SD cloc |        | 25                   |                      |      |

| Sustained Sequential Read             | 48GB   | 23 (1)(2)            | 24 <sup>(1)(3)</sup> |      |

| Sustained Sequential Read             | 1632GB | 23 <sup>(1)(2)</sup> | 24 <sup>(1)(3)</sup> | MB/s |

| Sustained Sequential Write            | 48GB   | 11 <sup>(1)(2)</sup> | 14 <sup>(1)(3)</sup> |      |

| Sustained Sequential Write            | 1632GB | 11 <sup>(1)(2)</sup> | 14 <sup>(1)(3)</sup> |      |

- 1. All values refer to Toshiba Flash 32/64Gb

- 2. Sustained Speed measured with USB-SD Memory Card reader. It depends on burst speed, flash number, and file size.

- 3. Maximum values were measured with Testmetrix tester.

## 3.2 Environmental Specifications

## 3.2.1 Recommended Operating Conditions

**Table 4: SD Memory Card Recommended Operating Conditions**

| Parameter                        | min | typ | max  | unit |

|----------------------------------|-----|-----|------|------|

| Extended Operating Temperature   | -25 | 25  | 85*) | °C   |

| Industrial Operating Temperature | -40 | 25  | 85*) | °C   |

#### 3.2.2 Recommended Storage Conditions

Table 5: SD Memory Card Recommended Storage Conditions

| Parameter                        | min | typ | max   | unit |  |

|----------------------------------|-----|-----|-------|------|--|

| Extended Storage Temperature     | -25 | 25  | 100*) | °C   |  |

| Industrial Operating Temperature | -40 | 25  | 100*) | °C   |  |

<sup>\*)</sup> high temperature storage without operation reduces the data retention, in operation the data will be refreshed, if data error issues were detected

#### 3.2.3 Humidity & EMC

Table 6: Humidity & EMC

| Parameter                 | Operating Non Operating     |                                                              |  |  |

|---------------------------|-----------------------------|--------------------------------------------------------------|--|--|

| Humidity (non-condensing) | operation: 95% RH @25°C     |                                                              |  |  |

|                           | storage: 93% RH @40°C, 500h |                                                              |  |  |

|                           | Non Contact Pads area:      | Contact Pads:                                                |  |  |

|                           | ±15 kV (air discharge),     | ±6 kV, according to IEC61000-4-2                             |  |  |

|                           | according to IEC61000-4-2   | Non Contact Pads area:                                       |  |  |

| ESD                       |                             | ±8kV (indirect) contact discharge, according to IEC61000-4-2 |  |  |

| L30                       | Non Contact Pads area:      | Contact Pads:                                                |  |  |

|                           | ±15 kV (air discharge)      | ±6 kV, Human body model according to JESD22A114F             |  |  |

|                           | Human body model            | Non Contact Pads area:                                       |  |  |

|                           | according to JESD22A114F    | ±8kV (indirect) contact discharge, according to JESD22A114F  |  |  |

#### 3.2.4 Environmental Conditions

#### Table 7. Environmental Conditions

| Parameter         | Operating                                                | Non Operating                                                                                                |  |  |

|-------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| UV light exposure | ight exposure UV: 254nm, 15Ws/cm² according to ISO7816-1 |                                                                                                              |  |  |

| Durability        |                                                          | 20,000 mating cycles                                                                                         |  |  |

| Drop test         |                                                          | 1.5m free fall                                                                                               |  |  |

| Bending / Torque  |                                                          | 10N / 0.10Nm ±2.5° max                                                                                       |  |  |

|                   |                                                          | 5ms, half sine wave ±xyz-axis, five pulses each Non operating, JESD22B110 Condition B                        |  |  |

| Vibration         | 15G                                                      | , 1.5mm p-p, 202000Hz, sweep xyz-axis,<br>five pulses each, Non operating<br>MIL-STD-883 M2007.3 Condition B |  |  |

### 3.3 Physical Dimensions

Table 8: Physical Dimensions

| Table 6. Physical Difficults |            |      |  |  |  |

|------------------------------|------------|------|--|--|--|

| Outer Physical Dimensions    | Value      | Unit |  |  |  |

| Length                       | 32.00±0.10 |      |  |  |  |

| Width                        | 24.00±0.10 | mm   |  |  |  |

| Thickness                    | 2.10±0.15  |      |  |  |  |

| Weight (typ.)                | 2          | g    |  |  |  |

## 3.4 Reliability

Table 9: Reliability

| Parameter                                        | Value                  |

|--------------------------------------------------|------------------------|

| Data Retention at beginning @ 40°C               | 10 years (JEDEC47G) *) |

| Data Retention at life end (2k PE cycles) @ 40°C | 1 year *)              |

<sup>\*)</sup> After every power on the card reads the whole flash and performs a data refresh, if necessary. So the data retention can be much longer in most use cases.

# **4** Capacity specification

Table 10: SD Memory Card capacity specification

| Capacity | Sectors    | Total addressable capacity (Byte) |

|----------|------------|-----------------------------------|

| 4GB      | 7'774'208  | 3'980'394'496                     |

| 8GB      | 15'802'368 | 8'090'812'416                     |

| 16GB     | 31'834'112 | 16'299'065'344                    |

| 32GB     | 63'930'368 | 32'732'348'416                    |

# **5** Card physical

## 5.1 Physical description

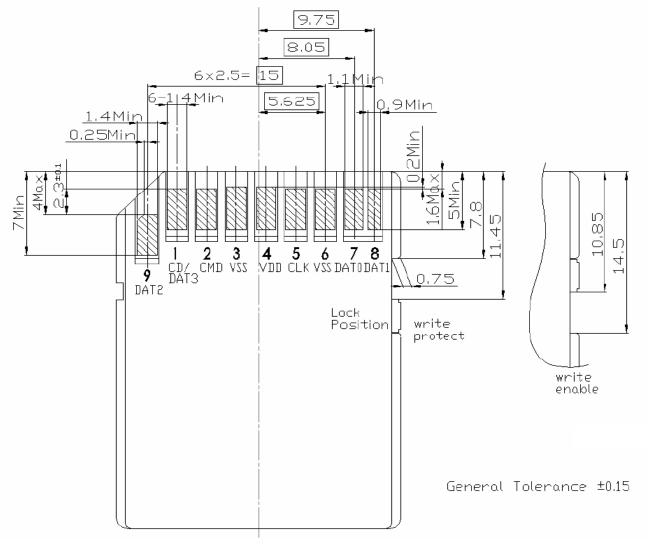

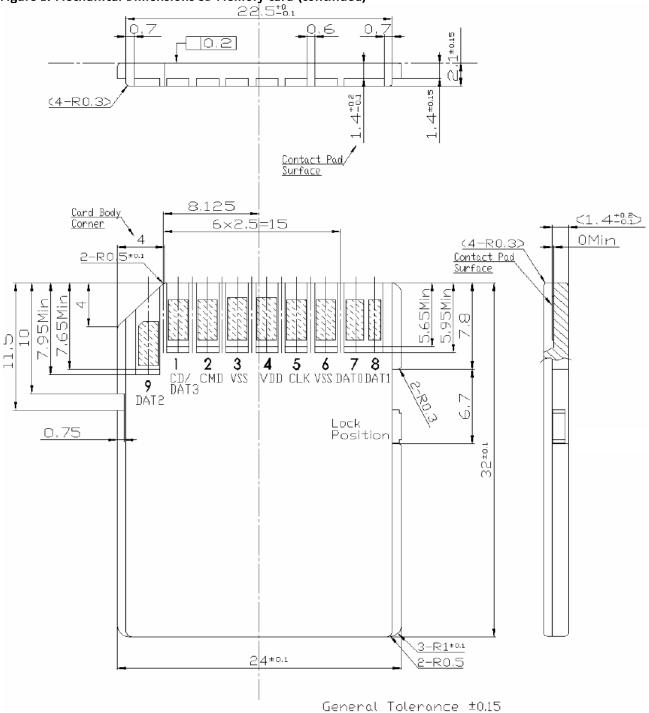

The SD Memory Card contains a single chip controller and Flash memory module(s). The controller interfaces with a host system allowing data to be written to and read from the Flash memory module(s). Figure 1 and Figure 2 show card dimensions.

Figure 1: Mechanical Dimensions SD Memory Card

Figure 2: Mechanical Dimensions SD Memory Card (continued)

## **6** Electrical interface

#### 6.1 Electrical description

Figure 3: SD Memory Card Block Diagram

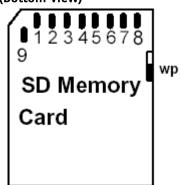

Figure 4: SD Memory Card Shape and Interface (Bottom View)

Table 11: SD Memory Card Pad Assignment

| Pin # |                      | SD Mode           |                                |      | SPI Mode          |                        |  |

|-------|----------------------|-------------------|--------------------------------|------|-------------------|------------------------|--|

|       | Name                 | Type <sup>1</sup> | Description                    | Name | Type <sup>1</sup> | Description            |  |

| 1     | CD/DAT3 <sup>2</sup> | I/0/PP3           | Card Detect/ Data Line [Bit 3] | CS   | <b>I</b> 3        | Chip Select (neg true) |  |

| 2     | CMD                  | PP                | Command/Response               | DI   | I                 | Data In                |  |

| 3     | VSS1                 | S                 | Supply voltage ground          | VSS  | S                 | Supply voltage ground  |  |

| 4     | VDD                  | S                 | Supply voltage                 | VDD  | S                 | Supply voltage         |  |

| 5     | CLK                  |                   | Clock                          | SCLK | 1                 | Clock                  |  |

| 6     | VSS2                 | S                 | Supply voltage ground          | VSS2 | S                 | Supply voltage ground  |  |

| 7     | DATo                 | I/O/PP            | Data Line [Bit o]              | DO   | O/PP              | Data Out               |  |

| 8     | DAT1 <sup>4</sup>    | I/O/PP            | Data Line [Bit 1]              | RSV  |                   |                        |  |

| 9     | DAT2 <sup>5</sup>    | I/O/PP            | Data Line [Bit 2]              | RSV  |                   |                        |  |

## Notes:

- 1) S: power supply; I: input; O: output using push-pull drivers; PP: I/O using push-pull drivers;

- The extended DAT lines (DAT1-DAT3) are input on power up. They start to operate as DAT lines after SET\_BUS\_WIDTH command. The Host shall keep its own DAT1-DAT3 lines in input mode, as well, while they are not used.

- 3) At power up this line has a 50k0hm pull up enabled in the card. This resistor serves two functions Card detection and Mode Selection. For Mode Selection, the host can drive the line high or let it be pulled high to select SD mode. If the host wants to select SPI mode it should drive the line low. For Card detection, the host detects that the line is pulled high. This pull-up should be disconnected by the user, during regular data transfer, with SET\_CLR\_CARD\_DETECT (ACMD42) command

- 4) DAT1 line may be used as Interrupt Output (from the Card) in SDIO mode during all the times that it is not in use for data transfer operations (refer to "SDIO Card Specification" for further details).

- 5) DAT2 line may be used as Read Wait signal in SDIO mode (refer to "SDIO Card Specification" for further details).

#### 6.2 DC characteristics

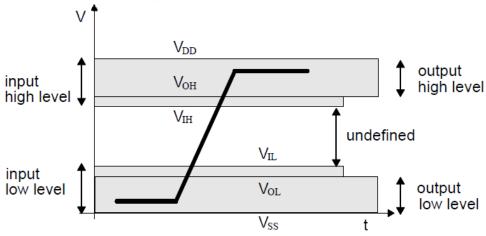

Measurements are at Recommended Operating Conditions unless otherwise specified.

Table 12: DC Characteristics

| Symbol          | Parameter                                        | min                   | typ  | max                   | unit | notes                |

|-----------------|--------------------------------------------------|-----------------------|------|-----------------------|------|----------------------|

| V <sub>OH</sub> | Output HIGH Voltage                              | 0.75*V <sub>DD</sub>  |      |                       | V    | $V_{OH} = -2mA$      |

| $V_{OL}$        | Output LOW Voltage                               |                       |      | 0.125*V <sub>DD</sub> | V    | V <sub>oL</sub> =2mA |

| $V_{IH}$        | Input HIGH Voltage                               | 0.625*V <sub>DD</sub> |      | VDD+o.3               | V    |                      |

| $V_{IL}$        | Input LOW Voltage                                | -0.3                  |      | 0.25*V <sub>DD</sub>  | V    |                      |

|                 | Operating Current Read                           |                       | 40   | 60                    | mA   | @ 25°C               |

|                 | Operating Current Write                          |                       | 60   | 80                    | mA   | @ 25°C               |

|                 | Background read and refresh <sup>1</sup>         |                       | 70   | 90                    | mA   | @ 25°C               |

| I <sub>DD</sub> | Pre-initialization Standby Current               |                       | 4800 | 8000                  | μΑ   | @ 25°C               |

|                 | Post-initialization Standby Current <sup>2</sup> |                       | 1100 | 3000                  | μΑ   | @ 25°C               |

|                 | Post-Illitialization Standby Current             |                       | 1500 | 4000                  | μΑ   | @ 85°C               |

| I <sub>LI</sub> | Input Leakage Current <sup>3</sup>               | -10                   |      | 10                    | μΑ   | without              |

| I <sub>LO</sub> | Output Leakage Current <sup>3</sup>              | -10                   |      | 10                    | μΑ   | pull up R            |

#### Notes:

- 1) The card performs auto data read of the whole card to check for ECC errors and performs data refresh. Typical this operation starts 5–10 minutes after power on or if some large multiple bit errors were detected

- 2) Before auto read the idle current is larger than the typical idle current after auto read

- 3) Before initialization DAT1 and DAT2 have a pull-up resistor with a leakage current of 60µA

Figure 5: Bus Signal levels

Table 13: SD Memory Card Recommended Operating Conditions

| Symbol          | _               | min                                              | typ | max | unit |    |

|-----------------|-----------------|--------------------------------------------------|-----|-----|------|----|

|                 |                 | Normal Operating Status                          | 2.7 | 3.3 | 3.6  | V  |

| V <sub>DD</sub> | Supply Voltage  | Basic Communication (CMDo, CMD15, CMD55, ACMD41) | 2.0 | 3.3 | 3.6  | V  |

| _               | Power Up Time ( | from oV to VDD min)                              |     |     | 250  | ms |

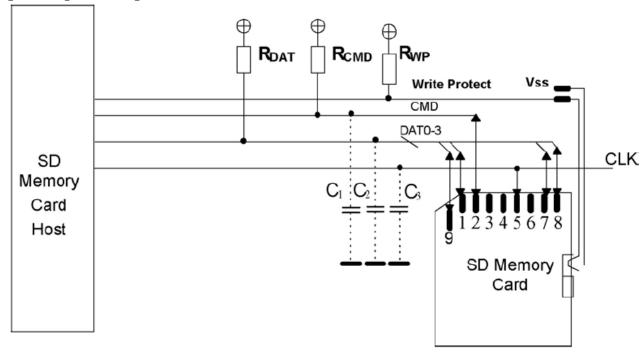

### **6.3 Signal Loading**

The total capacitance  $C_L$  is the sum of the bus master capacitance  $C_{HOST}$ , the bus capacitance  $C_{BUS}$ , and the capacitance  $C_{CARD}$  of the card connected to the line:

$C_L = C_{HOST} + C_{BUS} + C_{CARD}$ To allow the sum of the host and bus capacitances to be up to 20pF for the card, the following conditions in the table below are met by the card.

Table 14: Signal loading

| Parameter                                        | Symbol                | Min | Max | Unit | Notes                                                                    |

|--------------------------------------------------|-----------------------|-----|-----|------|--------------------------------------------------------------------------|

| Pull up resistance                               | $R_{CMD}$ , $R_{DAT}$ | 10  | 100 | k0hm | To prevent bus floating                                                  |

| Pull up resistance inside card (pin1)            | $R_{DAT_3}$           | 10  | 90  | k0hm | May be used for card detection                                           |

| Bus signal line capacitance for each signal line | $C_L$                 |     | 40  | pF   | Single card<br>C <sub>HOST</sub> +C <sub>BUS</sub> shall not exceed 30pF |

| Signal card capacitance for each signal pin      | $C_{CARD}$            |     | 10  | pF   | Single card                                                              |

| Signal line inductance                           |                       |     | 16  | nH   | f ≤ 20MHz                                                                |

| Capacioty Connected to Power line                | C <sub>C</sub>        |     | 5µF | μF   | To prevent inrush current                                                |

Figure 6: Signal Loading

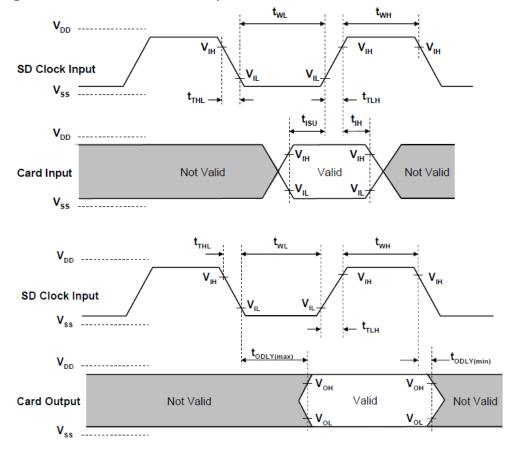

### 6.4 AC characteristics

### 6.4.1 Default Speed mode (0 - 25MHz)

Table 15: AC Characteristics Default Speed Mode

| Parameter                                                    | Symbol                      | Min      | Max | Unit | Notes                                     |  |  |

|--------------------------------------------------------------|-----------------------------|----------|-----|------|-------------------------------------------|--|--|

| Clock Clk All values are referred to min (VIH) and max (VIL) |                             |          |     |      |                                           |  |  |

| Clock frequency in data transfer mode                        | $f_{pp}$                    | 0        | 25  | MHz  |                                           |  |  |

| Clock frequency in card id mode                              | $f_{\mathtt{OD}}$           | 0/100 1) | 400 | kHz  |                                           |  |  |

| Clock low time                                               | $t_{WL}$                    | 10       |     | ns   | C <sub>card</sub> ≤1opF (1 card)          |  |  |

| Clock high time                                              | $t_{WH}$                    | 10       |     | ns   | C <sub>CARD</sub> \( \text{IOpt (i cald)} |  |  |

| Clock rise time                                              | $t_{\scriptscriptstyleTLH}$ |          | 10  | ns   |                                           |  |  |

| Clock fall time                                              | $t_{\scriptscriptstyleTHL}$ |          | 10  | ns   |                                           |  |  |

| Inputs CMD, DAT (referenced to CLK)                          |                             |          |     |      |                                           |  |  |

| CMD, DAT input setup time                                    | $t_{ISU}$                   | 5        |     | ns   | C <sub>card</sub> ≤1opF (1 card)          |  |  |

| CMD, DAT input hold time                                     | $t_{IH}$                    | 5        |     | ns   | C <sub>CARD</sub> ~ 10 pt (1 card)        |  |  |

| Outputs CMD, DAT (referenced to CLK)                         |                             |          |     |      |                                           |  |  |

| CMD, DAT output delay time during Data                       | +                           | 0        | 11. | ns   |                                           |  |  |

| Transfer Mode                                                | t <sub>odly</sub>           | 0        | 14  | 115  | $C_1 \leq 4opF$ (1 card)                  |  |  |

| CMD, DAT output delay time during Identification Mode        | t <sub>odly</sub>           | 0        | 50  | ns   | վ <u>-</u> 40pi (i caiu)                  |  |  |

Notes

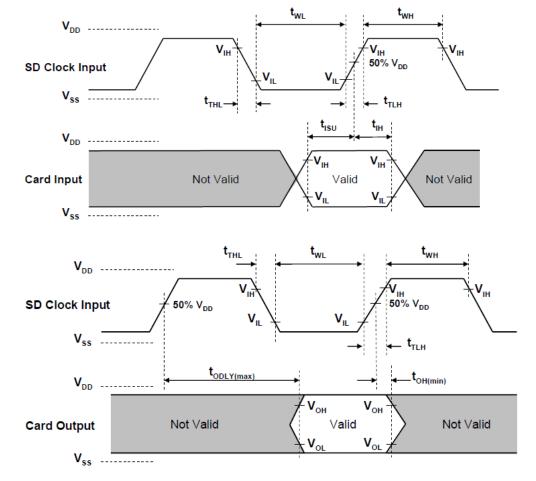

Figure 7: AC Characteristics Default Speed Mode

<sup>1.</sup> o kHz means to stop the clock. The minimum clock frequency should not be below 100kHz

## 6.4.2 High Speed mode (0 - 50MHz)

Table 16: AC Characteristics High Speed Mode

| Parameter                                                    | Symbol                      | Min | Max | Unit | Notes                              |  |  |

|--------------------------------------------------------------|-----------------------------|-----|-----|------|------------------------------------|--|--|

| Clock Clk All values are referred to min (VIH) and max (VIL) |                             |     |     |      |                                    |  |  |

| Clock frequency in data transfer mode                        | $f_{pp}$                    | 0   | 50  | MHz  |                                    |  |  |

| Clock low time                                               | $t_{WL}$                    | 7   |     | ns   |                                    |  |  |

| Clock high time                                              | $t_{wH}$                    | 7   |     | ns   | C <sub>card</sub> ≤1opF (1 card)   |  |  |

| Clock rise time                                              | $t_{\scriptscriptstyleTLH}$ |     | 3   | ns   |                                    |  |  |

| Clock fall time                                              | $t_{\scriptscriptstyleTHL}$ |     | 3   | ns   |                                    |  |  |

| Inputs CMD, DAT (referenced to CLK)                          |                             |     |     |      |                                    |  |  |

| input setup time                                             | t <sub>isu</sub>            | 6   |     | ns   | C <sub>cARD</sub> ≤1opF (1 card)   |  |  |

| input hold time                                              | t <sub>IH</sub>             | 2   |     | ns   | C <sub>CARD</sub> > 10 pt (1 catu) |  |  |

| Outputs CMD, DAT (referenced to CLK)                         |                             |     |     |      |                                    |  |  |

| output delay time during data transfer                       | todly                       |     | 14  | ns   | C <sub>L</sub> ≤ 4opF (1 card)     |  |  |

| mode                                                         | -0011                       |     | '   |      |                                    |  |  |

| output hold time                                             | $t_{oH}$                    | 2.5 |     | ns   | $C_L \ge 15 pF$ (1 card)           |  |  |

Notes

Figure 8: AC Characteristics High Speed Mode

<sup>1.</sup> In order to satisfy severe timing, the host shall drive only one card with max 4opF total at each line.

## 7 Host access Specification

The following chapters summarize how the host accesses the card:

- Chapter 7.1 summarizes the SD and SPI buses.

- Chapter 7.2 summarizes the registers.

#### 7.1 SD and SPI Bus Modes

The card supports SD and the SPI Bus modes. Application can chose either one of the modes. Mode selection is transparent to the host. The card automatically detects the mode of the reset command and will expect all further communication to be in the same communication mode. The SD mode uses a 4-bit high performance data transfer, and the SPI mode provides compatible interface to MMC host systems with little redesign, but with a lower performance.

#### 7.1.1 SD Bus Mode Protocol

The SD Bus mode has a single master (host) and multiple slaves (cards) synchronous topology. Clock, power, and ground signals are common to all cards. After power up, the SD Bus mode uses DATo only; after initialization, the host can change the cards' bus width from 1 bit (DATo) to 4 bits (DATo-DAT3). In high speed mode, only one card can be connected to the bus.

Communication over the SD bus is based on command and data bit streams which are initiated by a start bit and terminated by a stop bit.

- Command: a command is a token which starts an operation. A command is sent from the host either to a single card (addressed command) or to all connected cards (broadcast command). A command is transferred serially on the CMD line.

- Response: a response is a token which is sent from an addressed card, or (synchronously) from all

connected cards, to the host as an answer to a previously received command. A response is transferred

serially on the CMD line.

- Data: data can be transferred from the card to the host or vice versa. Data is transferred via the data lines.

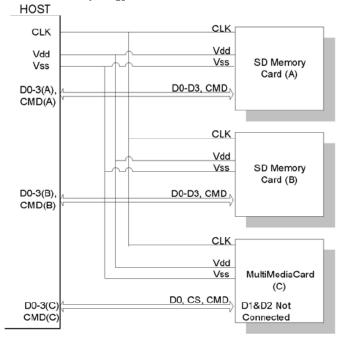

The SD bus signals are listed in Table 17, and the SD bus topology is illustrated in Figure 9: SD Bus Topology.

Table 17: SD Bus Signals

| Signal    | Description                           |

|-----------|---------------------------------------|

| CLK       | Host to card clock signal             |

| CMD       | Bidirectional Command/Response signal |

| DATo-DAT3 | 4 Bidirectional data signals          |

| Vdd, Vss  | Power and Ground                      |

Figure 9: SD Bus Topology

#### 7.1.2 SPI Bus Mode Protocol

The Serial Parallel Interface (SPI) Bus is a general purpose synchronous serial interface. The SPI mode consists of a secondary communication protocol. The interface is selected during the first reset command after power up (CMDo) and it cannot be changed once the card is powered on.

While the SD channel is based on command and data bit streams which are initiated by a start bit and terminated by a stop bit, the SPI channel is byte oriented. Every command or data block is built of 8-bit bytes and is byte aligned to the CS signal.

The card identification and addressing methods are replaced by a hardware Chip Select (CS) signal. There are no broadcast commands. For every command, a card (slave) is selected by asserting (active low) the CS signal. The CS signal must be continuously active for the duration of the SPI transaction (command, response and data). The only exception occurs during card programming, when the host can de-assert the CS signal without affecting the programming process.

The bidirectional CMD and DAT lines are replaced by unidirectional dataIn and dataOut signals.

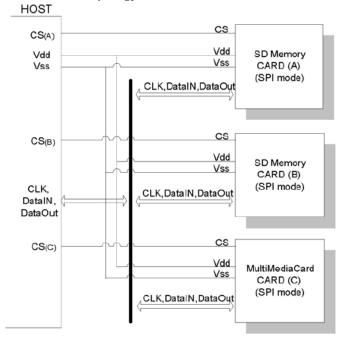

The SPI bus signals are listed Table 18 and the SPI bus topology is illustrated in Figure 10.

Table 18: SPI Bus Signals

| Signal   | Description               |

|----------|---------------------------|

| /CS      | Host to card chip select  |

| CLK      | Host to card clock signal |

| Data In  | Host to card data signal  |

| Data Out | Card to host data signal  |

| Vdd, Vss | Power and ground          |

Figure 10: SPI bus topology

#### 7.1.3 Mode Selection

The SD Memory Card wakes up in the SD mode. It will enter SPI mode if the CS signal is asserted (negative) during the reception of the reset command (CMDo) and the card is in *idle\_state*. If the card recognizes that the SD mode is required it will not respond to the command and remain in the SD mode.

If SPI mode is required the card will switch to SPI and respond with the SPI mode R1 response.

The only way to return to the SD mode is by entering the power cycle. In SPI mode the SD Memory Card protocol state machine is not observed. All the SD Memory Card commands supported in SPI mode are always available. During the initialization sequence, if the host gets Illegal Command indication for ACMD41 sent to the card, it may assume that the card is Multimedia Card. In that case it should re-start the card as Multimedia Card using CMD0 and CMD1.

### 7.2 Card Registers

The SD Memory Card has registers. Refer to Table 19 to Table 25 for detail.

Table 19: SD Memory Card registers

| Register<br>Name | Bit<br>Width | Description                          | Function                                                                                                                                 |

|------------------|--------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| CID              | 128          |                                      | This register contains the card identification information used during the Card Identification phase.                                    |

| OCR              |              |                                      | This register describes the operating voltage range and contains the status bit in the power supply.                                     |

| CSD              | 1112         |                                      | This register provides information on how to access the card content. Some fields of this register are writeable by PROGRAM_CSD (CMD27). |

| SCR              |              | SD Memory Card's<br>Special features | This register provides information on special features.                                                                                  |

| RCA              | 16           | Relative Card<br>Address             | This register carries the card address is SD Card mode.                                                                                  |

| SSR              | 512          |                                      | information about the card proprietary features and vendor specific life time information                                                |

Table 20: CID register

| Register Name | Bit Width | Description               | typ. value                |

|---------------|-----------|---------------------------|---------------------------|

| MID           | 8         | Manufacture ID            | ox5d                      |

| OID           | 16        | OEM/Application ID        | 0X5342                    |

| PNM           | 40        | Product Name              | ("LgBM1")<br>g=generation |

| PRV           | 8         | Product Revision          | oxgg                      |

| PSN           | 32        | Product Serial Number     | XXXXXXXX                  |

| _             | 4         | Reserved                  | 0X0                       |

| MDT           | 12        | Manufacture Date          | oxyym                     |

| CRC           | 7         | Check sum of CID contents | chksum                    |

| -             | 1         | Not used; always=1        | 1                         |

Table 21: OCR register

| OCR bit position | VDD voltage<br>window | typ. value | OCR bit position | VDD voltage<br>window         | typ. value |

|------------------|-----------------------|------------|------------------|-------------------------------|------------|

| 0-3              | Reserved              | 0          | 15               | 2.7-2.8                       | 1          |

| 4                | 1.6-1.7               | 0          | 16               | 2.8-2.9                       | 1          |

| 5                | 1.7-1.8               | 0          | 17               | 2.9-3.0                       | 1          |

| 6                | 1.8-1.9               | 0          | 18               | 3.0-3.1                       | 1          |

| 7                | 1.9-2.0               | 0          | 19               | 3.1-3.2                       | 1          |

| 8                | 2.0-2.1               | 0          | 20               | 3.2-3.3                       | 1          |

| 9                | 2.1-2.2               | 0          | 21               | 3.3-3.4                       | 1          |

| 10               | 2.2-2.3               | 0          | 22               | 3.4-3.5                       | 1          |

| 11               | 2.3-2.4               | 0          | 23               | 3.5-3.6                       | 1          |

| 12               | 2.4-2.5               | 0          | 24               | Switching to 1.8V accepted    | 0          |

| 13               | 2.5-2.6               | 0          | 25-30            | Reserved                      |            |

| 14               | 2.6-2.7               | 0          | 30               | Card Capacity<br>Status (CCS) | *1)        |

|                  |                       |            | 31               | o=busy; 1=ready               | *2)        |

#### Notes

- 1. This bit is valid only when the card power up status bit is set.

- 2. This bit is set to LOW if the card has not finished the power up routine.

Table 22: CSD register

| Register Name        | Bits    | Bit Width | Description                         | typ. Value   |

|----------------------|---------|-----------|-------------------------------------|--------------|

| CSD_STRUCTURE        | 127:126 | 2         | CSD structure                       | 01           |

| _                    | 125:120 | 6         | Reserved                            | 00000        |

| TAAC                 | 119:112 | 8         | Data read access time 1             | 00001110     |

| NSAC                 | 111:104 | 8         | Data read access time 2 (CLK cycle) | 00000000     |

| TRAN_SPEED           | 103:96  | 8         | Data transfer rate                  | 00110010     |

| CCC                  | 95:84   | 12        | Card command classes                | 010110110101 |

| READ_BL_LEN          | 83:80   | 4         | Read data block length              | 1001         |

| READ_BL_PARTIAL      | 79      | 1         | Partial blocks for read allowed     | 0            |

| WRITE_BLK_MISALIGN   | 78      | 1         | Write block misalignment            | 0            |

| READ_BLK_MISALIGN    | 77      | 1         | Read block misalignment             | 0            |

| DSR_IMP              | 76      | 1         | DSR implemented                     | 0            |

| _                    | 75:70   | 6         | Reserved                            | 000000       |

| C_SIZE               | 69:48   | 22        | Device size                         | xxx*)        |

| _                    | 47      | 1         | Reserved                            | 0            |

| ERASE_BLK_EN         | 46      | 1         | Erase single block enable           | 1            |

| SECTOR_SIZE          | 45:39   | 7         | Erase sector size                   | 1111111      |

| WP_GRP_SIZE          | 38:32   | 7         | Write protect group size            | 0000000      |

| WP_GRP_ENABLE        | 31      | 1         | Write protect group enable          | 0            |

| _                    | 30:29   | 2         | Reserved                            | 00           |

| R2W_FACTOR           | 28:26   | 3         | Write speed factor                  | 010          |

| WRITE_BL_LEN         | 25:22   | 4         | Write data block length             | 1001*)       |

| WRITE_BL_PARTIAL     | 21      | 1         | Partial blocks for write allowed    | 0            |

| _                    | 20:16   | 5         | Reserved                            | 00000        |

| FILE_FORMAT_GRP      | 15      | 1         | File format group                   | o W(1)       |

| COPY                 | 14      | 1         | Copy flag                           | o W(1)       |

| PERM_WRITE_PROTECT   | 13      | 1         | Permanent write protection          | o W(1)       |

| TMP_WRITE_PROTECT    | 12      | 1         | Temporary write protection          | o W          |

| FILE_FORMAT          | 11:10   | 2         | File format                         | 00 W(1)      |

| _                    | 9:8     | 2         | Reserved                            | 00 W         |

| CRC                  | 7:1     | 7         | Checksum of CSD contents            | xxxxxxx W    |

| - *\ D.:: C: d b.ld. | 0       | 1         | Always=1                            | 1            |

<sup>\*)</sup> Drive Size and block sizes vary with card capacity

memory capacity = (C\_SIZE+1) \* 512kByte

W value can be changed with CMD27 (PROGRAM\_CSD)

W(1) value can be changed ONCE with CMD27 (PROGRAM\_CSD)

Table 23: SCR register

| Field                 | Bits  | Bit Width | typ Value | remark                    |

|-----------------------|-------|-----------|-----------|---------------------------|

| SCR_STRUCTURE         | 63:60 | 4         | 0000      | SCR 1.012.00              |

| SD_SPEC               | 59:56 | 4         | 0010      | SD 2.0 or 3.0             |

| DATA_STAT_AFTER_ERASE | 55    | 1         | 1         | data are oxFF after erase |

| SD_SECURITY           | 54:52 | 3         | 011       | 2.00 (SDHC)               |

| SD_BUS_WIDTHS         | 51:48 | 4         | 0101      | 1 or 4 bit                |

| SD_SPEC3              | 47    | 1         | 1         | yes→ SD3.o                |

| EX_SECURITY           | 46:43 | 4         | 0000      | no extended security      |

| Reserved              | 42:34 | 9         | 0         | 0                         |

| CMD_SUPPORT           | 33:32 | 2         | 11        | CMD23 and CMD20 supported |

| Reserved              | 31:0  | 32        | 0         | 0                         |

Table 24: RCA register

| Field | Bit Width | typ Value |

|-------|-----------|-----------|

| RCA   | 16        | 0x0000*)  |

<sup>\*)</sup> After Initialization the card can change the RCA register.

Table 25: SSR register

| Field                                                                        | Bits    | Bit<br>Width | typ Value    | remark                           |

|------------------------------------------------------------------------------|---------|--------------|--------------|----------------------------------|

| Data bus width                                                               | 511:510 | 2            | 0X2*)        | 4 bit width                      |

| Secured mode                                                                 | 509:509 | 1            | 0X0          | not secured                      |

| Reserved for security                                                        | 508:502 | 7            | 0X00         | -                                |

| Reserved                                                                     | 501:496 | 6            | 0X00         | _                                |

| SD card type                                                                 | 495:480 | 16           | 0x0000       | Regular SD                       |

|                                                                              |         |              | 0X03000000   | 48MB                             |

| Size protected area                                                          | 479:448 | 32           | 0X04000000   | 64MB                             |

| Speed class                                                                  | 447:440 | 8            | 0X03         | Class 6                          |

| Move performance                                                             | 439:432 | 8            | 0X05         | 5 MB/s                           |

| Allocation unit size                                                         | 431:428 | 4            | 0X9          | 4 MiB                            |

| Reserved                                                                     | 427:424 | 4            | 0X0          |                                  |

| Erase unit size                                                              | 423:408 | 16           | 0X0001       | 1 AU                             |

| Erase unit timeout                                                           | 407:402 | 6            | 0X10         | 16 seconds                       |

| Erase unit offset                                                            | 401:400 | 2            | 0X1          | 1 seconds                        |

| UHS mode Speed Grade                                                         | 399:396 | 4            | 0X0          | (no UHS)                         |

| Allocation unit size in UHS mode                                             | 395:392 | 4            | OXO          | no UHS                           |

| Reserved                                                                     | 391:312 | 80           |              |                                  |

| Data structure version identifier, currently 1                               | 311:304 | 8            | 0X01         | version 1                        |

| Number of manufacturer marked defect blocks                                  | 303:288 | 16           | 0X0008       | 8 initial BB                     |

| Number of initial spare blocks (worst chip)                                  | 287:272 | 16           | 0X0074       | 116 spare blocks                 |

| Number of initial spare blocks (sum over all chips)                          | 271:256 | 16           | 0X0074       | 116 spare blocks                 |

| Percentage of remaining spare blocks (worst chip)                            | 255:248 | 8            | 0x64*)       | 100%                             |

| Percentage of remaining spare blocks (all chips)                             | 247:240 | 8            | 0x64*)       | 100%                             |

| Number of uncorrectable ECC errors (not including ECC errors during startup) | 239:224 | 16           | oxoooo*)     | o uncorrectable errors           |

| Number of correctable ECC errors (not including ECC errors during startup)   | 223:192 | 32           | oxoo45074b*) | 4523851 correctable ECC errors   |

| Lowest wear level class                                                      | 191:176 | 16           | oxoooo*)     | 0                                |

| Highest wear level class                                                     | 175:160 | 16           | oxoooo*)     | 0                                |

| Wear level threshold                                                         | 159:144 | 16           | 0x007f       | 127 block erases per WL<br>class |

| Total number of block erases                                                 | 143:96  | 48           | oxoo1ffo*)   | 8176 block erase<br>commands     |

| Number of flash blocks, in units of 256 blocks                               | 95:80   | 16           | 0X0008       | 2048 flash blocks                |

| Maximum flash block erase count target, in wear                              |         |              |              | Flash endurance 15 WL            |

| level class units                                                            | 79:64   | 16           | oxooof       | classes                          |

|                                                                              |         |              |              | (1920 erases)                    |

| Power on count                                                               | 63:32   | 32           | oxooooooo3*) | 3x power on                      |

| Firmware version                                                             | 31:0    | 32           | 0X13112529   | Firmware 131125                  |

Bit 311:0 are vendor specific, example values in the table

<sup>\*)</sup> value change in operation

## 8 RoHS and WEEE update from Swissbit

Dear Valued Customer,

We at Swissbit place great value on the environment and thus pay close attention to the diverse aspects of manufacturing environmentally and health friendly products. The European Parliament and the Council of the European Union have published two Directives defining a European standard for environmental protection. This states that CompactFlash Cards must comply with both Directives in order for them to be sold on the European market:

- RoHS Restriction of Hazardous Substances

- WEEE Waste Electrical and Electronic Equipment

Swissbit would like to take this opportunity to inform our customers about the measures we have implemented to adapt all our products to the European norms.

#### What is the WEEE Directive (2012/19/EU)?

#### The Directive covers the following points:

- Prevention of WEEE

- Recovery, recycling and other measures leading to a minimization of wastage of electronic and electrical equipment

- Improvement in the quality of environmental performance of all operators involved in the EEE life cycle, as well as measures to incorporate those involved at the EEE waste disposal points

#### What are the key elements?

#### The WEEE Directive covers the following responsibilities on the part of producers:

Producers must draft a disposal or recovery scheme to dispose of EEE correctly. Producers must be registered as producers in the country in which they distribute the goods. They must also supply and publish information about the EEE categories. Producers are obliged to finance the collection, treatment and disposal of WEEE.

#### Inclusion of WEEE logos on devices

In reference to the Directive, the WEEE logo must be printed directly on all devices that have sufficient space. «In exceptional cases where this is necessary because of the size of the product, the symbol of the WEEE Directive shall be printed on the packaging, on the instructions of use and on the warranty» (WEEE Directive 2012/19/EU)

#### When does the WEEE Directive take effect?

The Directive came into effect internationally on July 04, 2012.

#### What is RoHS (2011/65/EU)?

#### The goals of the Directive are to:

- Place less of a burden on human health and to protect the environment by restricting the use of hazardous substances in new electrical and electronic devices

- To support the WEEE Directive (see above)

#### RoHS enforces the restriction of the following 6 hazardous substances in electronic and electrical devices:

- Lead (Pb) no more than 0.1% by weight in homogeneous materials

- Mercury (Hg) no more than 0.1% by weight in homogeneous materials

- Cadmium (Cd) no more than 0.01% by weight in homogeneous materials

- Chromium (Cr6+) no more than 0.1% by weight in homogeneous materials

#### Swissbit is obliged to minimize the hazardous substances in the products.

According to part of the Directive, manufacturers are obliged to make a self-declaration for all devices with RoHS. Swissbit carried out intensive tests to comply with the self-declaration. We have also already taken steps to have the analyses of the individual components guaranteed by third-party companies.

Swissbit carried out the following steps during the year with the goal of offering our customers products that are fully compliant with the RoHS Directive.

- Preparing all far-reaching directives, logistical enhancements and alternatives regarding the full understanding and introduction of the RoHS Directive's standards

- Checking the components and raw materials:

- o Replacing non-RoHS-compliant components and raw materials in the supply chain

- Cooperating closely with suppliers regarding the certification of all components and raw materials used by Swissbit

- Modifying the manufacturing processes and procedures

- Successfully adapting and optimizing the new management-free integration process in the supply chain

- Updating existing production procedures and introducing the new procedures to support the integration process and the sorting of materials

- Carrying out the quality process

- Performing detailed function and safety tests to ensure the continuous high quality of the Swissbit product line

#### When does the RoHS Directive take effect?

As of June 08, 2011 only new electrical and electronic devices with approved quantities of RoHS will be put on the market.

#### When will Swissbit be offering RoHS-approved products?

Swissbit's RoHS-approved products are available now. Please contact your Swissbit contact person to find out more about exchanging your existing products for RoHS-compliant devices.

#### For your attention

We understand that packaging and accessories are not EEE material and are therefore not subject to the WEEE or RoHS Directives.

Contact details: Swissbit AG Industriestrasse 4 CH 9552 Bronschhofen

Tel: +41 71 913 03 03 - Fax: +41 71 913 03 15

E-mail: info@swissbit.com - Website: www.swissbit.com

## 9 Part Number Decoder

| 11. Temp. | Option |

|-----------|--------|

|-----------|--------|

| Extended Temp. Range<br>-25°C to 85°C   | E |

|-----------------------------------------|---|

| Industrial Temp. Range<br>-40°C to 85°C | I |

#### 12. DIE Classification

|                           | S-40<br>MLC | S-400<br>SLC |

|---------------------------|-------------|--------------|

| MONO (single die package) | G           | М            |

| DDP (dual die package)    | L           | D            |

| QDP (dual die package)    | Н           | Q            |

#### 13. PIN Mode

| Single nCE & R/nB    | Е |

|----------------------|---|

| Dual nCE & Dual R/nB | F |

| Quad nCE & Quad R/nB | G |

## 14. Configuration XYZ

### X→ Configuration

| Configuration | Х |

|---------------|---|

| default       | 1 |

#### Y → FW Revision

| FW Revision | Υ |

|-------------|---|

| Version 1   | 1 |

#### Z → optional

| 2 7 Optional |   |

|--------------|---|

| Optional     | Z |

| optional     | 1 |

### 15. Option

| Swissbit / Standard | STD |

|---------------------|-----|

# **10** Swissbit Label specification

#### 10.1 Front side label

4GB SDHC Memory Card

32GB SDHC Memory Card

## 10.2 Back side marking

SWISSBIT

SFSD8192L1BM1

T0-E-GE-111-STD

0413-60012345

Made in Germany

CE WEEE

Partnumber Date-Lot/Serial

Example of the back side laser marking

## 11 Revision History

**Table 26: Document Revision History**

| Date              | Revision | Revision Details                                                                                                                                               |  |

|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| October 10, 2013  | 0.80     | nitial preliminary release                                                                                                                                     |  |

| December 16, 2013 | 0.90     | updated card LBA values                                                                                                                                        |  |

| December 20, 2013 | 0.95     | Add SD 3.0 compliant, SCR register                                                                                                                             |  |

| March 05, 2014    | 0.96     | Standby currents corrected DC and AC characteristics updated to SDA 3.0 specification SSR-Register erase count target, CE Declaration removed (extra document) |  |

#### Disclaimer:

No part of this document may be copied or reproduced in any form or by any means, or transferred to any third party, without the prior written consent of an authorized representative of Swissbit AG ("SWISSBIT"). The information in this document is subject to change without notice. SWISSBIT assumes no responsibility for any errors or omissions that may appear in this document, and disclaims responsibility for any consequences resulting from the use of the information set forth herein. SWISSBIT makes no commitments to update or to keep current information contained in this document. The products listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. Moreover, SWISSBIT does not recommend or approve the use of any of its products in life support devices or systems or in any application where failure could result in injury or death. If a customer wishes to use SWISSBIT products in applications not intended by SWISSBIT, said customer must contact an authorized SWISSBIT representative to determine SWISSBIT willingness to support a given application. The information set forth in this document does not convey any license under the copyrights, patent rights, trademarks or other intellectual property rights claimed and owned by SWISSBIT. The information set forth in this document is considered to be "Proprietary" and "Confidential" property owned by SWISSBIT.

ALL PRODUCTS SOLD BY SWISSBIT ARE COVERED BY THE PROVISIONS APPEARING IN SWISSBIT'S TERMS AND CONDITIONS OF SALE ONLY, INCLUDING THE LIMITATIONS OF LIABILITY, WARRANTY AND INFRINGEMENT PROVISIONS. SWISSBIT MAKES NO WARRANTIES OF ANY KIND, EXPRESS, STATUTORY, IMPLIED OR OTHERWISE, REGARDING INFORMATION SET FORTH HEREIN OR REGARDING THE FREEDOM OF THE DESCRIBED PRODUCTS FROM INTELLECTUAL PROPERTY INFRINGEMENT, AND EXPRESSLY DISCLAIMS ANY SUCH WARRANTIES INCLUDING WITHOUT LIMITATION ANY EXPRESS, STATUTORY OR IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

©2014 SWISSBIT AG All rights reserved.

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331