# **ST2601B**

# 8-bit Integrated Microcontroller

# **Datasheet**

Version 1.1 2009/05/07 Note: Sitronix Technology Corp. reserves the right to change the contents in this document without prior notice. This is not a final specification. Some parameters are subject to change.

#### **1 GENERAL DESCRIPTION**

The ST2601B is a 8-bit integrated microcontroller designed with CMOS silicon gate technology. The true static CPU core, power down modes and dual oscillators design makes the ST2601B suitable for power saving and long battery life designs. The ST2601B integrates various logic to support functions on-chip which are needed by system designers.

The ST2601B features the capacity of memory access of maximum 44M bytes and DMA function for fast memory transfer. Six chip-select pins are equipped for direct connection to external ROM, SRAM, Flash memory or other devices. The maximum size for a single external memory device can be 16M bytes.

The ST2601B has 39 I/Os grouped into 5 ports. They are Port-C, Port-D, Port-E (7 pins), Port-F and Port-L, where the Port-F consists of 8 open-drain output pins shared with LCD COMs. Each I/O pins can be programmed to input or output individually. Port-C input pins provide both pull-up and pull-down options. The other input pins only support the pull-up option. In the case of output mode, Port-C output pins have open-drain type and CMOS type options; while the other ports are fixed at CMOS type. The Port-C/D/E/F/L are shared with other system functions. All the properties of the I/O pins are still programmable when they are configured as other special functional signals.

The ability of driving large LCD panels, up to 100X100in BW mode, and hardware gray-level support may enrich the display information and the diversify the display contents as well. By the patented sharing mechanism design of internal memory, the LCD display function can be done without the need of external display RAM. The variable LCD buffer design also makes it feasible to use small internal display RAM as the buffer of large-sized display. User may free major internal RAM for computing or temporary access while keeping the display content. The clock of LCD (LCDCK) is not only sourced from

main-frequency (OSC), it can also be sourced by OSCX (32KHz crystal) to make current consumption to be minimum. Besides, Vlcd has excellent voltage variation when Vdd changes from 2.4V to 3.6V. Further more, ST2601B has inside trimming fuse function for Vlcd and LVD.So every ST2601B real-chip will have almost the same default Vlcd and LVD voltage.

The ST2601B equips 2 serial communication ports, one UART port and one SPI port, to perform different communications, ex.: RS-232 and IrDA, with system components or other products such as PC, Notebook, and popular PDA. Three clocking outputs can produce synthesized PWM signals or high frequency carrier for IR remote control. This helps products become more useful in our daily life.

The built-in four-channel PSG are designed to generate key tone, melody, voice, and speech. Two dedicated pins with large driving capacity can drive a buzzer/speaker directly.

The ST2601B has a Low Voltage Detector (LVD) for power management usage. The status of internal or external power can be detected and reported to the management software.

Power bouncing during power-on is a major problem when designing a reliable system. The ST2601B equips a Low Voltage Reset function to keep the whole system in reset status when power is low. After the power returns to normal level, the system may recover its original states and keeps working correctly.

With these integrated functions inside, the ST2601B single chip microcontroller is a right solution for PDA, translator, databank and other consumer products.

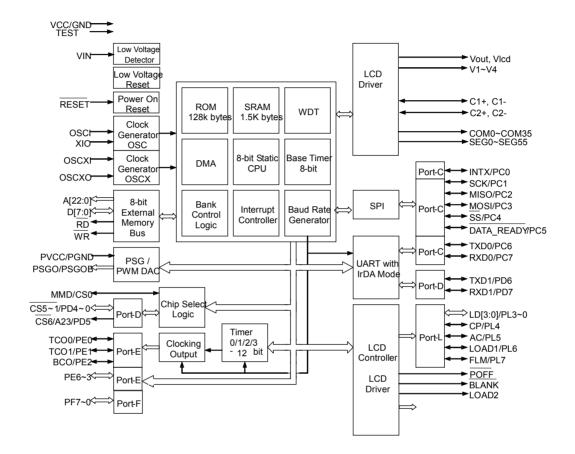

The block diagram of ST2601B is shown in the following figure.

#### 2 BLOCK DIAGRAM

FIGURE 2-1 ST2601B Block Diagram

#### **3 FEATURES**

- Totally static 8-bit CPU

- ROM: 128k x 8-bit

- RAM: 1.5K x 8-bit

- Stack: Up to 128-level deep

- Operation voltage: 2.4V ~ 3.6V

- Operation frequency:

- 3.0Mhz@2.4V(Min.)

- 4.0Mhz@2.7V(Min.)

- LCD Drives

- COM: 36 outputs. Eight shared with one output port

- SEG: 56 outputs. Shared with 3 I/O ports and memory bus signals.

- One <u>8x8</u> Signed Multiplier

- Low Voltage Reset (LVR)

- Two levels by code option

- Low Voltage Detector (LVD)

- Programmable 4 levels

- System power or external battery level can be detected.

- Programmable Watchdog Timer (WDT)

- Memory interface to ROM, RAM, Flash

#### Memory configuration

- Three kinds of banks for program, data and interrupt

- 12-bit bank registers support up to 44M bytes

- Six programmable chip-selects with 4 modes

- Maximum single device of 16M bytes

- General-Purpose I/O (GPIO) ports

- Up to 39 bit programmable I/Os

- 8 dedicated CMOS I/Os

- 23 shared with LCD SEGs

- 8 open drain output pins shared with LCD COMs

- Bit programmable pull-up for input pins

- Pull-up/down and open-drain/CMOS control for Port-C Timer/Counter

- Four 12-bit timers.

- One 8-bit base timer

- Seven fixed base timers

- Three clocking outputs

- Clock sources including Timer0/1, baud rate generator

- Eleven prioritized interrupts with dedicated exception vectors

- External interrupt (edge triggered)

- LCD buffer interrupt

- Base timer interrupt

- Timer0~3 interrupts (x4)

- SPI interrupts (x2)

- UART interrupts (x2)

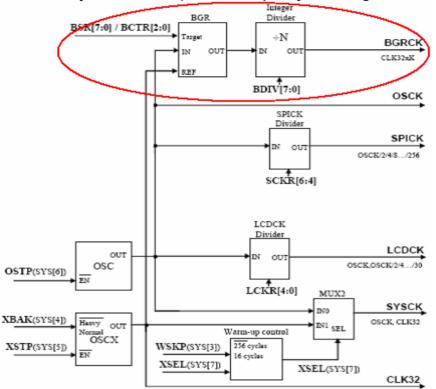

- Dual clock sources with warm-up timer

Low frequency crystal oscillator (OSCX)

- High frequency resistor or crystal/resonator oscillator

- (OSC) selected by pin option ...... 455K~4M Hz

- Direct Memory Access (DMA)

- Block-to-Block transfer

- Block to Single port

LCD Power Management

- DC-DC converter with 8-level output control

- LC driving voltage regulator with 16-level control

- -1/4, 1/5, 1/6 bias options with 4 voltage followers

- LCD Driver

- 32x28~56x36 resolution, maximum 2016 dots

- One clock source from osc / oscx

- Internal bias resistors(1/4, 1/5, 1/6 bias).

- LCD Controller (LCDC)

- Software programmable display size up to 100X100

- B/W, Hardware 4/16 gray levels with 5-bit palette

- Support 1-/4-/8-bit LCD data bus

- Share system memory with display buffer and with no loss of the CPU time

- LCD buffer extension function to combine both internal and external RAM for larger display

- Diverse functions including virtual screen, panning, scrolling, contrast control and alternating signal generator

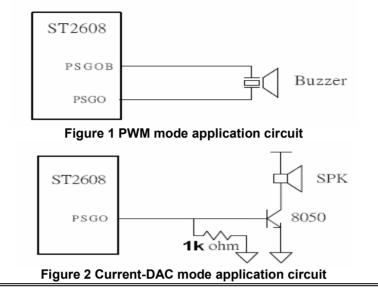

- Programmable Sound Generator (PSG)

- Four channels with three playing modes:

9-bit ADPCM, 8-bit PCM and 8-bit melody

- One 16-byte buffer and 6-bit volume control per channel

- Wavetable melody support

- Two dedicated PWM outputs for direct driving

- One 12-bit current DAC

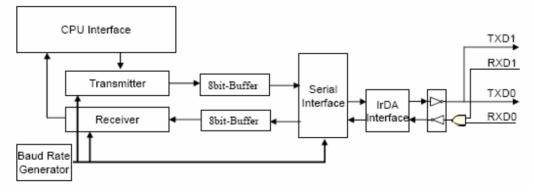

- Universal Asynchronous Receiver/Transmitter (UART)

Full-duplex operation

- Baud rate generator with one digital PLL

- Standard baud rates of 600 bps to 115.2 kbps

- Both transmitter and receiver buffers supported

- Direct glueless support of IrDA physical layer protocol

- Two sets of I/Os (TX,RX) for two independent devices

- Serial Peripheral Interface (SPI)

- Master and slave modes

- Five serial signals including enable and data-ready

- Both transmitter and receiver buffers supported

- Programmable data length from 7-bit to 16-bit

- VIcd/LVD trimming fuse function:

- VIcd default voltage variation trimming.

- 4-level LVD voltage variation trimming.

- Three power down modes

- WAI0 mode

- WAI1 mode

- STP mode

## 4 SIGNAL DESCRIPTIONS

| TABLE 4-1 | Signal I | Function | Groups |

|-----------|----------|----------|--------|

|           | Orginari |          | Groups |

| Function Group                 | Pad No. | Designation                                                 | Description                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|--------------------------------|---------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                |         |                                                             | VCC: Power supply for system                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Power                          |         | VCC , PVCC, AVCC                                            | AVCC: Power supply for LCD function                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                |         |                                                             | <b>PVCC:</b> Power supply for PSGO and PSGOB                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                |         |                                                             | GND: System power ground                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Ground                         |         | GND , PGND, AGND                                            | AGND: Power ground for LCD function                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                |         |                                                             | PGND: Power ground for PSGO and PSGOB                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                |         |                                                             | RESET : Active low system reset signal input                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                |         |                                                             | TEST: Leave this pin open when normal operation                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                |         |                                                             | <b>MMD</b> / $\overline{\mathrm{CS0}}$ : Memory modes selection pin                                                                                                                                                                                                                                                                                   |  |  |  |

|                                |         | RESET,                                                      | Normal mode: Enable internal ROM.                                                                                                                                                                                                                                                                                                                     |  |  |  |

| System control                 |         | TEST,                                                       | MMD/ $\overline{CS0}$ is connected to GND.                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                |         | MMD/CS0                                                     | Emulation mode: Disable internal ROM.                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                |         |                                                             | $\begin{array}{ll} \mbox{MMD}/\overline{\text{CS0}} & \mbox{is connected to the chip-select pin of external ROM. During reset period, the MMD/CS0} & \mbox{is an internally pulled-up input pin. After reset cycles, MMD/\overline{CS0} & \mbox{is changed to be an output pin. It will output signal } \hline \end{centering} \label{eq:constraint}$ |  |  |  |

|                                |         |                                                             | High frequency oscillator (OSC) mode selected by code-option                                                                                                                                                                                                                                                                                          |  |  |  |

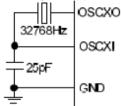

|                                |         | XIO,OSCI                                                    | Crystal mode: One crystal or resonator should be connected<br>between OSCI and XIO                                                                                                                                                                                                                                                                    |  |  |  |

| Clock                          |         | OSCXO,OSCXI, ,                                              | Resistor oscillator mode: One resistor should be connected<br>between OSCI and VCC                                                                                                                                                                                                                                                                    |  |  |  |

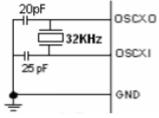

|                                |         |                                                             | OSCXI, OSCXO: Connect one 32768Hz crystal between these two pins when using low frequency oscillator                                                                                                                                                                                                                                                  |  |  |  |

|                                |         | WR / SEG9,                                                  | External memory R/W control signals / LCD Segment drivers                                                                                                                                                                                                                                                                                             |  |  |  |

| External memory<br>bus signals |         | RD / SEG8                                                   |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| / LCD drivers                  |         | A[22:0]/SEG32~SEG10                                         | External memory address bus / LCD Segment drivers                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                |         | D[7:0]/SEG7~SEG0                                            | External memory data bus / LCD Segment drivers                                                                                                                                                                                                                                                                                                        |  |  |  |

| PSG/PWM DAC                    |         | PSGO, PSGOB                                                 | PSG outputs. Connect to one buzzer or speaker                                                                                                                                                                                                                                                                                                         |  |  |  |

| Chip selects / LCD             |         | CS5 ~ 1/PD4~0 /<br>SEG33~SEG37,                             | I/O port D and chip-select outputs / LCD Segment drivers                                                                                                                                                                                                                                                                                              |  |  |  |

| drivers                        |         | CS6 /A23/PD5 /SEG38                                         |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| UART                           |         | RXD0/PC7,TXD0/PC6,<br>RXD1/PD7/SEG40,TXD1/<br>PD6/SEG39     | UART signals and I/Os / LCD Segment drivers                                                                                                                                                                                                                                                                                                           |  |  |  |

| SPI                            |         | DATA_READY/PC5 ,<br>SS/PC4 , SDO/PC3 ,<br>SDI/PC2 , SCK/PC1 | SPI signals and I/Os                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Function Group                                  | Pad No. | Designation                                                                                                                 | Description                                                   |  |  |  |  |  |  |  |

|-------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|--|--|--|--|

| External<br>clock/signal<br>interrupt           |         | INTX/PC0                                                                                                                    | External interrupt inputs                                     |  |  |  |  |  |  |  |

| Clocking output                                 |         | BCO/PE2/SEG43 ,<br>TCO1/PE1/SEG42 ,<br>TCO0/PE0/SEG41                                                                       | Clocking outputs / LCD Segment drivers                        |  |  |  |  |  |  |  |

| GPIO / LCD drivers                              |         | PE6~3/SEG47~SEG44                                                                                                           | I/O port E/ LCD Segment drivers                               |  |  |  |  |  |  |  |

| LCD control<br>signals (for<br>controller mode) |         | BLANK/COM0,<br>POFF/COM1,<br>FLM/COM2,<br>LOAD1/COM3,<br>LOAD2/COM4,<br>AC/COM5,CP/COM6,<br>EIO/COM7,<br>LD7~LD0/COM15/COM8 | LCD control signals                                           |  |  |  |  |  |  |  |

| LCD voltage source                              |         | Vout, Vlcd, V1, V2, V3, V4                                                                                                  | LCD voltage sources                                           |  |  |  |  |  |  |  |

| LCD voltage<br>booster                          |         | C1+, C1-, C2+, C2-                                                                                                          | Connect a 0.1 uF between C1+ and C1-, C2+ and C2-repectively. |  |  |  |  |  |  |  |

| Low Voltage<br>Detector                         |         | VIN                                                                                                                         | Analog input pin of Low Voltage Dector module                 |  |  |  |  |  |  |  |

#### **TABLE 4-2 Signal Function Groups (continued)**

## 5 PAD DIAGRAM

|                                                                                                                                                                   |                                                                                                                                                                                                                                              | segpad [13] | segpad [12] | segpad [11] | segpad [10] | segpad [9]  | segpad [8]  | segpad [7]  | segpad [6] | segpad [5] | segpad [4] | segpad [3] | segpad [2] | segpad [1] | segpad [0] | V4pad  | V3pad | V2pad  | V1pad  | VLCD   | VOUT   | agnd   | avcc   | C2+  | C1+   | c2-  | c1-  | VIN             |                                                                                                                                                                                                         |                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|------------|------------|------------|--------|-------|--------|--------|--------|--------|--------|--------|------|-------|------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| segpad [14]<br>segpad [15]<br>segpad [16]<br>segpad [17]<br>segpad [19]<br>segpad [20]<br>segpad [21]<br>segpad [22]<br>segpad [22]<br>segpad [23]<br>segpad [25] |                                                                                                                                                                                                                                              |             |             |             |             |             |             |             |            |            |            |            |            |            |            |        |       |        |        |        |        |        |        |      |       |      |      |                 | $X \times X \times$                                                                                                             | compad [35]<br>compad [34]<br>compad [32]<br>compad [32]<br>compad [31]<br>compad [30]<br>compad [29]<br>compad [27]<br>compad [26]<br>compad [25]<br>compad [23]                |

| segpad [26]<br>segpad [27]<br>segpad [28]<br>segpad [30]<br>segpad [31]<br>segpad [32]<br>segpad [33]<br>segpad [34]<br>segpad [35]<br>segpad [36]                |                                                                                                                                                                                                                                              |             |             |             |             | ,           |             |             |            |            | Γ          |            | 2          |            | 6          | 5      |       |        |        | 1      |        | E      | 3      |      |       |      |      |                 | $\square$                                                                                                     | compad [22]<br>compad [21]<br>compad [20]<br>compad [19]<br>compad [18]<br>compad [17]<br>compad [16]<br>compad [15]<br>compad [14]<br>compad [13]<br>compad [12]<br>compad [11] |

| segpad [38]<br>segpad [39]<br>segpad [40]<br>segpad [41]<br>segpad [42]<br>segpad [42]<br>segpad [44]<br>segpad [45]<br>segpad [46]<br>segpad [47]<br>segpad [48] | $\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes\boxtimes$ | X           | X           | X           | X           | X           | X           | X           | X          | X          | X          | X          | X          | X          | X          | K test | X     | X      | X      | X      | X      | X      | X      |      |       |      |      | X pfuse_pad [3] | $\square \boxtimes \boxtimes$ | compad [10]<br>compad [9]<br>compad [8]<br>compad [6]<br>compad [6]<br>compad [4]<br>compad [3]<br>compad [2]<br>compad [1]<br>compad [0]                                        |

| l                                                                                                                                                                 |                                                                                                                                                                                                                                              | segpad [49] | segpad [50] | segpad [51] | segpad [52] | segpad [53] | segpad [54] | segpad [55] | VCC        |            |            |            |            | MMD/CS0    | Reset      |        |       | bc [5] | pc [4] | bc [3] | pc [2] | pc [1] | bc [0] | PVCC | PSGOB | PSGO | PGND | GND             |                                                                                                                                                                                                         | J                                                                                                                                                                                |

#### **DEVICE INFORMATION** 6

- 1. Pad size: 90um x 90um

- Substrate: GND

Chip size: 3520 um x 3800 um

| PAD<br>No. | Symbol  | х       | Y       |

|------------|---------|---------|---------|

| 1          | SEG[14] | -1690.0 | 1750.5  |

| 2          | SEG[15] | -1690.0 | 1640.5  |

| 3          | SEG[16] | -1690.0 | 1530.5  |

| 4          | SEG[17] | -1690.0 | 1420.5  |

| 5          | SEG[18] | -1690.0 | 1315.0  |

| 6          | SEG[19] | -1690.0 | 1215.0  |

| 7          | SEG[20] | -1690.0 | 1115.0  |

| 8          | SEG[21] | -1690.0 | 1015.0  |

| 9          | SEG[22] | -1690.0 | 915.0   |

| 10         | SEG[23] | -1690.0 | 808.0   |

| 11         | SEG[24] | -1690.0 | 702.5   |

| 12         | SEG[25] | -1690.0 | 602.5   |

| 13         | SEG[26] | -1690.0 | 502.5   |

| 14         | SEG[27] | -1690.0 | 402.5   |

| 15         | SEG[28] | -1690.0 | 302.5   |

| 16         | SEG[29] | -1690.0 | 202.5   |

| 17         | SEG[30] | -1690.0 | 102.5   |

| 18         | SEG[31] | -1690.0 | 2.5     |

| 19         | SEG[32] | -1690.0 | -101.0  |

| 20         | SEG[33] | -1690.0 | -201.0  |

| 21         | SEG[34] | -1690.0 | -306.5  |

| 22         | SEG[35] | -1690.0 | -416.5  |

| 23         | SEG[36] | -1690.0 | -522.0  |

| 24         | SEG[37] | -1690.0 | -622.0  |

| 25         | SEG[38] | -1690.0 | -722.0  |

| 26         | SEG[39] | -1690.0 | -822.0  |

| 27         | SEG[40] | -1690.0 | -922.0  |

| 28         | SEG[41] | -1690.0 | -1029.0 |

| 29         | SEG[42] | -1690.0 | -1134.5 |

| 30         | SEG[43] | -1690.0 | -1234.5 |

| 31         | SEG[44] | -1690.0 | -1334.5 |

| 32         | SEG[45] | -1690.0 | -1434.5 |

| 33         | SEG[46] | -1690.0 | -1540.0 |

| 34         | SEG[47] | -1690.0 | -1650.0 |

| 35         | SEG[48] | -1690.0 | -1760.0 |

| PAD | Symbol  | X       | Y        |  |  |

|-----|---------|---------|----------|--|--|

| No. | -       |         |          |  |  |

| 36  | SEG[49] | -1348.3 | -1830.0  |  |  |

| 37  | SEG[50] | -1238.3 | -1830.0  |  |  |

| 38  | SEG[51] | -1128.3 | -1830.0  |  |  |

| 39  | SEG[52] | -1028.3 | -1830.0  |  |  |

| 40  | SEG[53] | -928.3  | -1830.0  |  |  |

| 41  | SEG[54] | -828.3  | -1830.0  |  |  |

| 42  | SEG[55] | -728.3  | -1830.0  |  |  |

| 43  | VCC     | -607.0  | -1830.0  |  |  |

| 44  | XIO     | -502.0  | -1830.0  |  |  |

| 45  | OSCI    | -402.0  | -1830.0  |  |  |

| 46  | OSCXO   | -302.0  | -1830.0  |  |  |

| 47  | OSCXI   | -202.0  | -1830.0  |  |  |

| 48  | MMD/CS0 | -102.0  | -1830.0  |  |  |

| 49  | RESETB  | -2.0    | -1830.0  |  |  |

| 50  | PC[7]   | 101.7   | -1830.0  |  |  |

| 51  | TEST    | 103.2   | -1650.95 |  |  |

| 52  | PC[6]   | 201.7   | -1830.0  |  |  |

| 53  | PC[5]   | 301.7   | -1830.0  |  |  |

| 54  | PC[4]   | 401.7   | -1830.0  |  |  |

| 55  | PC[3]   | 501.7   | -1830.0  |  |  |

| 56  | PC[2]   | 601.7   | -1830.0  |  |  |

| 57  | PC[1]   | 701.7   | -1830.0  |  |  |

| 58  | PC[0]   | 801.7   | -1830.0  |  |  |

| 59  | PVCC    | 918.8   | -1830.0  |  |  |

| 60  | PSGOB   | 1031.9  | -1830.0  |  |  |

| 61  | PSGO    | 1158.1  | -1830.0  |  |  |

| 62  | PGND    | 1271.2  | -1830.0  |  |  |

| 63  | GND     | 1389.9  | -1830.0  |  |  |

| 64  | COM[0]  | 1690.0  | -1786.6  |  |  |

| 65  | COM[1]  | 1690.0  | -1676.6  |  |  |

| 66  | COM[2]  | 1690.0  | -1566.6  |  |  |

| 67  | COM[3]  | 1690.0  | -1466.6  |  |  |

| 68  | COM[4]  | 1690.0  | -1366.6  |  |  |

| 69  | COM[5]  | 1690.0  | -1266.6  |  |  |

| 70  | COM[6]  | 1690.0  | -1166.6  |  |  |

| PAD<br>No. | Symbol  | Х       | Y       |  |  |

|------------|---------|---------|---------|--|--|

| 71         | COM[7]  | 1690.0  | -1066.6 |  |  |

| 72         | COM[8]  | 1690.0  | -966.6  |  |  |

| 73         | COM[9]  | 1690.0  | -866.6  |  |  |

| 74         | COM[10] | 1690.0  | -766.6  |  |  |

| 75         | COM[11] | 1690.0  | -666.6  |  |  |

| 76         | COM[12] | 1690.0  | -566.6  |  |  |

| 77         | COM[13] | 1690.0  | -466.6  |  |  |

| 78         | COM[14] | 1690.0  | -366.6  |  |  |

| 79         | COM[15] | 1690.0  | -266.6  |  |  |

| 80         | COM[16] | 1690.0  | -166.6  |  |  |

| 81         | COM[17] | 1690.0  | -66.6   |  |  |

| 82         | COM[18] | 1690.0  | 33.4    |  |  |

| 83         | COM[19] | 1690.0  | 133.4   |  |  |

| 84         | COM[20] | 1690.0  | 233.4   |  |  |

| 85         | COM[21] | 1690.0  | 333.4   |  |  |

| 86         | COM[22] | 1690.0  | 433.4   |  |  |

| 87         | COM[23] | 1690.0  | 533.4   |  |  |

| 88         | COM[24] | 1690.0  | 633.4   |  |  |

| 89         | COM[25] | 1690.0  | 733.4   |  |  |

| 90         | COM[26] | 1690.0  | 833.4   |  |  |

| 91         | COM[27] | 1690.0  | 933.4   |  |  |

| 92         | COM[28] | 1690.0  | 1033.4  |  |  |

| 93         | COM[29] | 1690.0  | 1133.4  |  |  |

| 94         | COM[30] | 1690.0  | 1233.4  |  |  |

| 95         | COM[31] | 1690.0  | 1333.4  |  |  |

| 96         | COM[32] | 1690.0  | 1434.6  |  |  |

| 97         | COM[33] | 1690.0  | 1534.6  |  |  |

| 98         | COM[34] | 1690.0  | 1644.6  |  |  |

| 99         | COM[35] | 1690.0  | 1754.6  |  |  |

| 100        | VIN     | 1362.1  | 1830.0  |  |  |

| 101        | C1-     | 1234.35 | 1830.0  |  |  |

| 102        | C2-     | 1124.35 | 1830.0  |  |  |

| 103        | C1+     | 1021.05 | 1830.0  |  |  |

| 104        | C2+     | 921.05  | 1830.0  |  |  |

| 105        | AVCC    | 819.05  | 1830.0  |  |  |

| PAD<br>No. | Symbol  | Y        |        |

|------------|---------|----------|--------|

| 106        | AGND    | 717.45   | 1830.0 |

| 107        | VOUT    | 615.45   | 1830.0 |

| 108        | VLCD    | 515.45   | 1830.0 |

| 109        | V1      | 413.95   | 1830.0 |

| 110        | V2      | 313.95   | 1830.0 |

| 111        | V3      | 213.95   | 1830.0 |

| 112        | V4      | 113.55   | 1830.0 |

| 113        | SEG[0]  | 7.95     | 1830.0 |

| 114        | SEG[1]  | -92.05   | 1830.0 |

| 115        | SEG[2]  | -192.05  | 1830.0 |

| 116        | SEG[3]  | -292.05  | 1830.0 |

| 117        | SEG[4]  | -392.05  | 1830.0 |

| 118        | SEG[5]  | -492.05  | 1830.0 |

| 119        | SEG[6]  | -592.05  | 1830.0 |

| 120        | SEG[7]  | -692.05  | 1830.0 |

| 121        | SEG[8]  | -792.05  | 1830.0 |

| 122        | SEG[9]  | -892.05  | 1830.0 |

| 123        | SEG[10] | -992.05  | 1830.0 |

| 124        | SEG[11] | -1092.05 | 1830.0 |

| 125        | SEG[12] | -1202.05 | 1830.0 |

| 126        | SEG[13] | -1312.05 | 1830.0 |

|            |         |          |        |

|            |         |          |        |

|            |         |          |        |

|            |         |          |        |

|            |         |          |        |

|            |         |          |        |

|            |         |          |        |

|            |         |          |        |

| PAD<br>No. | Symbol | x | Y |

|------------|--------|---|---|

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

| PAD<br>No. | Symbol | x | Y |

|------------|--------|---|---|

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

| -          |        |   |   |

|            |        |   |   |

|            |        |   |   |

| -          |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

| -          |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

|            |        |   |   |

#### 7 ELECTRICAL CHARACTERISTICS

#### 7.1 Absolute Maximum Rations

\*Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. All the ranges are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied or intended. Exposed to the absolute maximum rating conditions for extended periods may affect device reliability.

#### 7.2 DC/AC Electrical Characteristics

Standard operation conditions: VCC = 3.0V, GND = 0V, T<sub>A</sub> = 25°C, OSC = 4M Hz, unless otherwise specified

| Parameter                       | Symbol           | Min.    | Тур. | Max.     | Unit | Condition                                                                 |

|---------------------------------|------------------|---------|------|----------|------|---------------------------------------------------------------------------|

| Operating Voltage               | VCC              | 2.4     | 3.0  | 3.6      | V    | Fosc = 3MHz                                                               |

| Operating voltage               | VCC              | 2.7     | 3.0  | 3.6      | V    | Fosc = 4MHz                                                               |

| Operating Frequency             | F1               | -       | -    | 3        | MHz  | VCC = 2.4V ~ 3.6V                                                         |

| Operating Frequency             | F <sub>2</sub>   | -       | -    | 4        | MHz  | VCC = 2.7 ~ 3.6V                                                          |

| Operating Current               | I <sub>OP</sub>  |         | 2.5  | 3        | mA   | All I/O port are input and pull-up, execute NOP instruction, LCDC on      |

| Standby Current                 | I <sub>SB0</sub> |         | 450  | 550      | μA   | All I/O port are input and pull-up, OSCX on, LCDC off (WAIT0 mode)        |

| Standby Current                 | I <sub>SB1</sub> |         | 3.5  | 5        | μA   | All I/O port are input and pull-up, OSCX on, LCDC off (WAIT1 mode)        |

| Standby Current                 | I <sub>SB2</sub> |         | 0.5  | 1        | μA   | All I/O port are input and pull-up, OSCX off, LCDC off (WAIT1 mode)       |

| Standby Current                 | I <sub>SB3</sub> |         | 100  | 130      | υΑ   | LCD on, sysck = LCDCK = OSCX, OSC off, Wait0, no<br>panel (fast B/W mode) |

| Input High Voltage              | V <sub>IH</sub>  | 0.7Vcc  |      | Vcc+0.3  | V    | Port-C/D/E/L                                                              |

|                                 |                  | 0.85Vcc |      |          | V    | RESET                                                                     |

| Input Low Voltage               | V <sub>IL</sub>  | GND-0.3 |      | 0.3Vcc   | V    | Port-C/D/E/L                                                              |

|                                 |                  |         |      | 0.15Vccc | v    | RESET                                                                     |

| Pull-up resistance              | RIH              |         | 150  |          | KΩ   | Port-C/D/E/L (input Voltage=0.7VCC)                                       |

| Output high voltage             | V <sub>OH1</sub> | 0.7Vcc  |      |          | V    | Port-C/D/L (I <sub>OH</sub> =-6mA)                                        |

| Output low voltage              | $V_{\text{OL1}}$ |         |      | 0.3Vcc   | V    | Port-C/D/E/L (I <sub>OL</sub> =9mA)                                       |

| Output high voltage             | $V_{\text{OH2}}$ | 0.7Vcc  |      |          | V    | PSG0/PSG0B( in PWM mode), $I_{OH}$ = 35mA.                                |

| Output low voltage              | $V_{\text{OL2}}$ |         |      | 0.3Vcc   | V    | PSG0/PSG0B( in PWM mode), I <sub>OL</sub> = -65mA.                        |

| DAC current                     |                  | 2.4mA   | 3    | 3.6mA    |      | DAC output current of maximum digital input value                         |

| Low Voltage Detector<br>current | Ilvr             |         | 30   | 60       | μA   | Total LVD current consumption                                             |

| Vlcd variation                  |                  | -3%     |      | +3%      |      |                                                                           |

| INT LVD variation               |                  | -4%     |      | +4%      |      |                                                                           |

| EXT LVD variation               |                  | -4%     |      | +4%      |      |                                                                           |

| SPI clock frequency             |                  |         | -    | 4.0      | MHz  | SPI slave mode                                                            |

#### 7.3 AC Electrical Characteristics

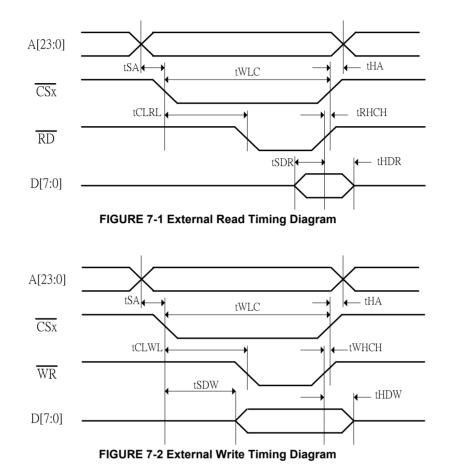

TABLE 7-1 Timing parameters for FIGURE 7-1 and FIGURE 7-2Standard operation conditions: VCC = 3.0V, GND = 0V,  $T_A = 25^{\circ}C$

| Symbol | Characteristic                                               |      | Rating   |      | Unit |

|--------|--------------------------------------------------------------|------|----------|------|------|

| Oymbol | Ondracteristic                                               | Min. | Тур.     | Max. | Onit |

| tSA    | Address setup time                                           | —    | —        | 10   | ns   |

| tHA    | Address hold time                                            | 0    |          | —    | ns   |

| tWLC   | CS "L" pulse width                                           | 166  | —        | —    | ns   |

| tCLWL  | CS asserted to $\overline{\mathrm{WR}}$ asserted             | —    | 1/2 tWLC | —    | ns   |

| tWHCH  | CS negated after WR is negated                               | 10   | —        | —    | ns   |

| tSDW   | CS asserted to data-out is valid                             | _    | 1/2 tWLC | _    | ns   |

| tHDW   | Data-out hold time after $\overline{\mathrm{WR}}$ is negated | 20   | —        |      | ns   |

| tCLRL  | CS asserted to $\overline{\text{RD}}$ asserted               | —    | 1/2 tWLC | —    | ns   |

| tRHCH  | CS negated after $\overline{RD}$ is negated                  | 10   | _        | _    | ns   |

| tSDR   | Data-in valid before $\overline{RD}$ is negated              | 30   | —        | —    | ns   |

| tHDR   | Data-in hold time after $\overline{RD}$ is negated           | 10   | —        | —    | ns   |

| tR     | Signal rise time                                             | _    | 20       | _    | ns   |

| tF     | Signal fall time                                             | _    | 10       | _    | ns   |

#### 7.4 Characteristic Charts

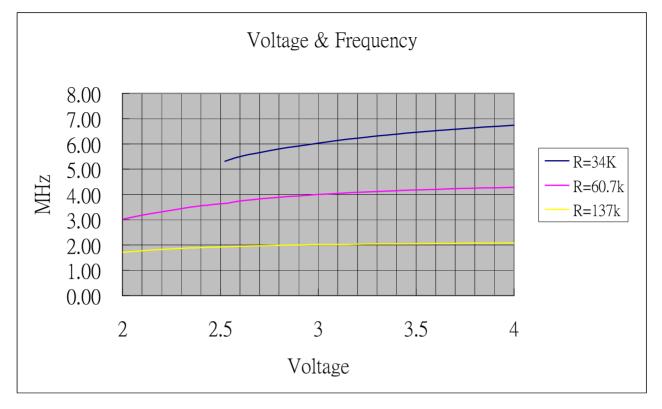

FIGURE 7-3 Frequency of R-OSC as a function of VCC

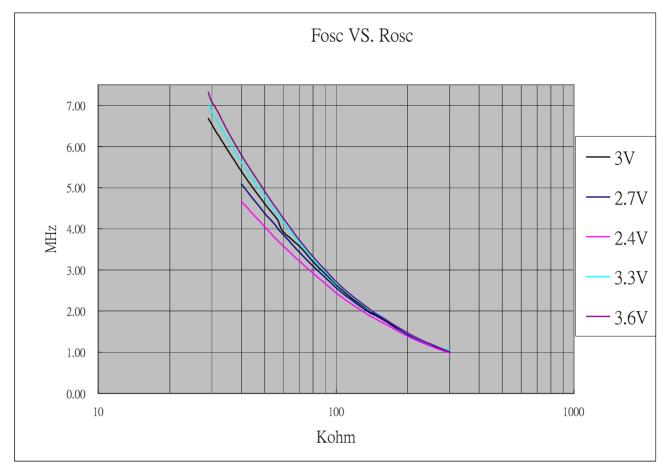

FIGURE 7-4 Frequency of R-OSC as a function of RESISTANCE

| Voltage   |          |

|-----------|----------|

| Frequency | 3V       |

| 4MHz      | 60K Ohm  |

| 3MHz      | 90K Ohm  |

| 2MHz      | 140K Ohm |

| 1MHz      | 300K Ohm |

|           |          |

#### 8 APPLICATION CIRCUITS

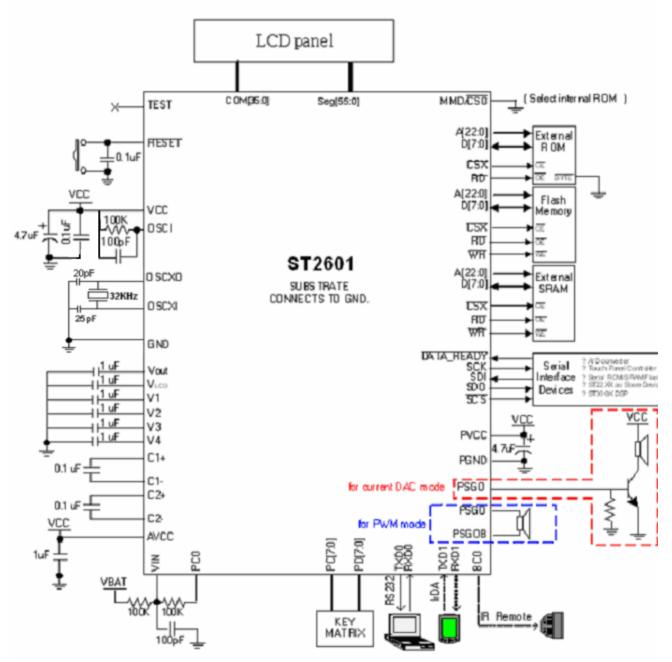

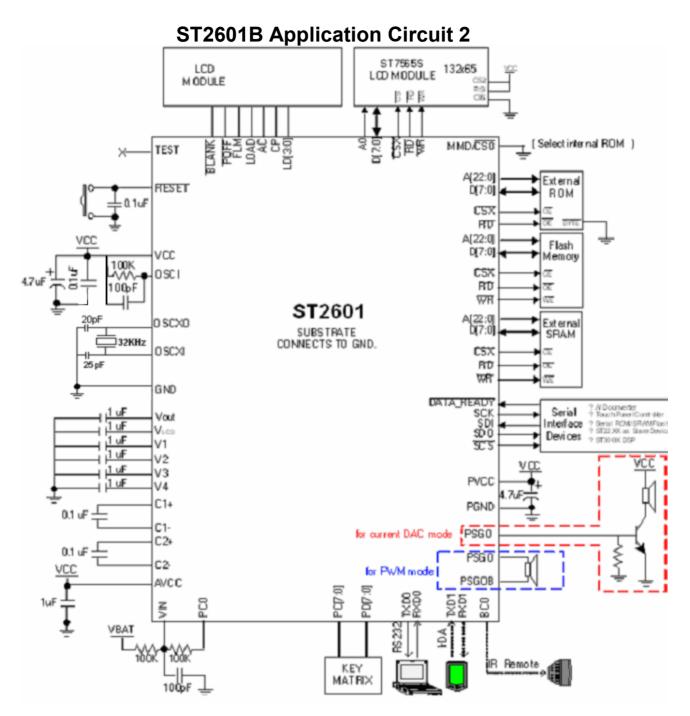

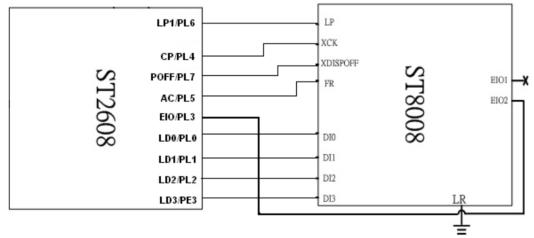

# **ST2601B Application Circuit 1**

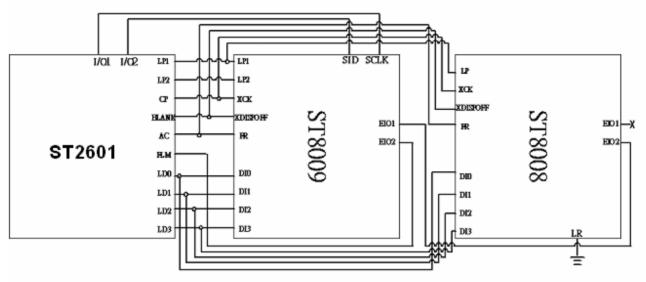

# ST2601B+ST8008+ST8009 Application Circuit

Note:

LR pin of ST8008 is connected to GND.

L/R bit of ST8009 is configured as low by "interface control selection" instruction

# 9 FEATURE COMPARISON OF ST26XXB SERIES

| Part Number                     | ST2608B                                       | ST2604B                                    | ST2602B                                    | ST2601B                                   |  |  |  |  |

|---------------------------------|-----------------------------------------------|--------------------------------------------|--------------------------------------------|-------------------------------------------|--|--|--|--|

| ROM                             | 1M Byte                                       | 512K Byte                                  | 256K Byte                                  | 128K Byte                                 |  |  |  |  |

| RAM                             | 5K Byte                                       | 3.5K Byte                                  | 2.5K Byte                                  | 1.5K Byte                                 |  |  |  |  |

| Built-in LCD Driver             | 36 COMs X 72<br>SEGs                          | 36 COMs X 64 SEGs                          | 36 COMs X 56 SEGs                          | 36 COMs X 56<br>SEGs                      |  |  |  |  |

| Driving LCD with<br>ext. driver | ~9000 dots (16<br>gray)<br>~36000 dots (mono) | ~6000 dots (16 gray)<br>~24000 dots (mono) | ~4000 dots (16 gray)<br>~16000 dots (mono) | ~2500dots (16 gray)<br>~10000 dots (mono) |  |  |  |  |

| Dedicated I/O                   | 24 (PA, PC, PL)                               | 16 (PA, PC)                                | 8 (PC)                                     | 8 (PC)                                    |  |  |  |  |

| LCD-Shared I/O                  | 32 (PB, PD, PE,<br>PF)                        | 39 (PB[6:0], PD, PE,<br>PL, PF)            | 31 (PD, PE[6:0], PL,<br>PF)                | 31 (PD, PE[6:0], PL,<br>PF)               |  |  |  |  |

| LCD gray level                  |                                               | 16 gray                                    | levels                                     |                                           |  |  |  |  |

| PSG /<br>volume-control         |                                               | 4-channel wavet                            | able / 64 levels                           |                                           |  |  |  |  |

| DAC                             |                                               | 9-bit PWM, 12-b                            | bit current DAC                            |                                           |  |  |  |  |

| Low voltage detector            |                                               | 4 lev                                      | rels                                       |                                           |  |  |  |  |

| Low voltage reset               |                                               | Yes                                        |                                            |                                           |  |  |  |  |

| Watchdog timer                  |                                               | Yes                                        |                                            |                                           |  |  |  |  |

| Serieal interface               | UART, SPI, IrDA                               |                                            |                                            |                                           |  |  |  |  |

| Trimming fuse                   | YES                                           |                                            |                                            |                                           |  |  |  |  |

| LCDCK=32KHz                     |                                               | YE                                         | S                                          |                                           |  |  |  |  |

# 9.1 LCFG Setting Difference of ST2600B series

#### ST2608B

| 050012.01 |         | Pad Definition  |          |         |       |          |          |          |          |

|-----------|---------|-----------------|----------|---------|-------|----------|----------|----------|----------|

| CFGS[2~0] | SEG0~31 | SEG32           | SEG33~38 | SEG39   | SEG40 | SEG41~47 | SEG48~55 | SEG56~63 | SEG64~71 |

| 00X       |         | SEG0~71         |          |         |       |          |          |          |          |

| 010       |         | SEG0~63 PE0~PE7 |          |         |       |          | PE0~PE7  |          |          |

| 011       |         | SEG0~55 PB0~PB7 |          |         |       |          |          | PE0~PE7  |          |

| 100       |         |                 | SEG0~47  |         |       |          | No Use   | PB0~PB7  | PE0~PE7  |

| 101       | SEG0~31 | No Use          | PD       | PD0~PD7 |       | No       | Use      | PB0~PB7  | PE0~PE7  |

| 110       | A/D Bus | A/D Bus PD0~F   |          |         |       | SEG0~31  |          |          |          |

| 111       | A/D Bus | PD              | 0~PD7    |         | No    | Use      | PB0~PB7  | PE0~PE7  |          |

#### ST2604/ST2604B

| CFGS[2~0] | Pad Definition |           |           |        |          |          |          |

|-----------|----------------|-----------|-----------|--------|----------|----------|----------|

|           | SEG0~31        | SEG32     | SEG33~39  | SEG40  | SEG41~47 | SEG48~55 | SEG56~63 |

| 000       |                |           | SEG       | ) ~ 63 |          |          |          |

| 001       |                | SEG0 ~    | 39        | PD7    | PB0 ~ 6  | PE0 ~ 7  | PL0 ~ 7  |

| 010       |                | SEG0 ~ 63 |           |        |          |          |          |

| 011       |                |           | SEG0 ~ 55 |        |          |          | PL0 ~ 7  |

| 100       |                |           | SEG0 ~ 47 |        |          | PE0 ~ 7  | PL0 ~ 7  |

| 101       | SEG0 ~ 31      | A22       | PD0 ~ 7   |        | PB0 ~ 6  | PE0 ~ 7  | PL0 ~ 7  |

| 110       | A/D bus        |           | PD0 ~ 7   |        | PB0 ~ 6  | PE0 ~ 7  | PL0 ~ 7  |

| 111       | A/D bus        |           | PD0 ~ 7   |        | PB0 ~ 6  | PE0 ~ 7  | PL0 ~ 7  |

#### ST2601B / ST2602B

| CFGS[2~0] | Pad Definition |               |           |       |          |          |  |

|-----------|----------------|---------------|-----------|-------|----------|----------|--|

|           | SEG0~31        | SEG32         | SEG33~39  | SEG40 | SEG41~47 | SEG48~55 |  |

| 000       |                |               | SEG0 ~ 5  | 5     |          |          |  |

| 001       |                | SEG0 ~        | 39        | PD7   | PE0 ~ 6  | PL0 ~ 7  |  |

| 010       |                | SEG0 ~ 55     |           |       |          |          |  |

| 011       |                |               | SEG0 ~ 5  | 5     |          |          |  |

| 100       |                |               | SEG0 ~ 47 |       |          | PL0 ~ 7  |  |

| 101       | SEG0 ~ 31      | A22           | PD0 ~ 7   |       | PE0 ~ 6  | PL0 ~ 7  |  |

| 110       | A/D bus        |               | PD0 ~ 7   |       | PE0 ~ 6  | PL0 ~ 7  |  |

| 111       | A/D bus        | ) bus PD0 ~ 7 |           |       | PE0 ~ 6  | PL0 ~ 7  |  |

## 10 CHECK LIST

| Check List of ST2601B-                                                |                                                                                                                                                                                                                                      |  |  |  |  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 8-Bit Microcontroller With 128K By                                    | tes ROM                                                                                                                                                                                                                              |  |  |  |  |

| CODE OPTION<br>LOW VOLTAGE RESET                                      | 1.4 Volt 2.1 Volt                                                                                                                                                                                                                    |  |  |  |  |

| OSCILLATOR                                                            | _32768 Hz Crystal<br>_R-OSC MHz (Resistor = KΩ)<br>_Resonator _Crystal MHz                                                                                                                                                           |  |  |  |  |

| OPERATING VOLTAGE                                                     | 2.4V ~ 3.6V    2.7V ~ 3.6V      Regulator    V      Other Range    ~      Note: Maximum operating frequency = 4.0 Mhz@2.7V, 3.0 Mhz@2.4V                                                                                             |  |  |  |  |

|                                                                       |                                                                                                                                                                                                                                      |  |  |  |  |

| BATTERY<br>POWER DOWN MODES                                           | CR20 x AAx AAAx<br>WAI-0 WAI-1                                                                                                                                                                                                       |  |  |  |  |

| LOW VOLTAGE DETECTOR                                                  | Disabled<br>Internal-LVD level1(2.4V) Internal-LVD level2(2.6V)<br>Internal-LVD level3(2.8V) Internal-LVD level4(3.0V)<br>External-LVD level1(1.2V) External-LVD level2(1.3V)<br>External-LVD level3(1.4V) External-LVD level4(1.5V) |  |  |  |  |

| UART                                                                  | Enabled, Baud Rate: bps Disabled                                                                                                                                                                                                     |  |  |  |  |

| SPI                                                                   | Enabled, Bit Rate: bps Disabled                                                                                                                                                                                                      |  |  |  |  |

| ST2600B EV<br>mode Selection<br>Please check ST2600B DVB<br>(PCB-300) | □ ST2601B EV mode: JP58 2→3 JP59 1→2                                                                                                                                                                                                 |  |  |  |  |

| LCD SPECIFICATIONS                                                    | Resolution: x Duty: 1/ Bias: 1/ VLCD: V<br>Frame Rate: Hz Alternation: Every _Frame _ Lines                                                                                                                                          |  |  |  |  |

|                                                                       | Driver: _ST8012x _ST8008x _ST8009x _ST8011x                                                                                                                                                                                          |  |  |  |  |

| LCD Gray-level                                                        | Black and White 4 Gray-level 16 Gray-level                                                                                                                                                                                           |  |  |  |  |

| PSG mode                                                              | Current-type DAC                                                                                                                                                                                                                     |  |  |  |  |

| Register Value                                                        | When playing sound: the PSGC =, LFRA =,LXMAX=,<br>When LCD is on: LCKR=LCTR=LFRA =LXMAX=,<br>LYMAX=LPOW =LREG =LCFG =<br>When LVD is on: LVCTR =<br>When power down: SYS =(WAIT0 or WAIT1)                                           |  |  |  |  |

| Data sheet                                                                                                                                                                                                            | ST2601B user's manual Ver         |                     |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|--|--|--|--|

| CODE FILE: .BI                                                                                                                                                                                                        | N                                 | DATE(Y/M/D): 20 / / |  |  |  |  |

| CHECK SUM:                                                                                                                                                                                                            | /lode)                            |                     |  |  |  |  |

| Note: a. File format must be<br>b. File should be wrapped in ZIP fo<br>c. Only single file is allowed.<br>d. File length is 128K bytes.<br>e. Functions should be checked on<br>f. Electric characteristics of the em | the emulation board or by real ch | ip.                 |  |  |  |  |

| CUSTOMER                                                                                                                                                                                                              |                                   |                     |  |  |  |  |

| COMPANY                                                                                                                                                                                                               |                                   |                     |  |  |  |  |

| SIGNATURE                                                                                                                                                                                                             |                                   |                     |  |  |  |  |

| SITRONIX                                                                                                                                                                                                              | SITRONIX                          |                     |  |  |  |  |

| FAE/SA                                                                                                                                                                                                                | FAE/SA                            |                     |  |  |  |  |

| SALSE                                                                                                                                                                                                                 |                                   |                     |  |  |  |  |

#### **Project Name**

| _   | ITEM                                                                                                                                                                                                                                                                                                                                                                                                                   | CHECK | NOTE |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

|     | Make sure the resistor of R-OSC matches the desired frequency and VCC                                                                                                                                                                                                                                                                                                                                                  |       |      |

| 2.  | Make sure the referenced data sheet is the most updated version                                                                                                                                                                                                                                                                                                                                                        |       |      |

| 3.  | After power on, enter wait-1 mode for0.5 second before normal operation                                                                                                                                                                                                                                                                                                                                                |       |      |

| 4.  | Initialize user RAM and every related control register                                                                                                                                                                                                                                                                                                                                                                 |       |      |

| 5.  | Confirm Vlcd level, duty, bias, frame rate, alternating rate and the display quality of LCD                                                                                                                                                                                                                                                                                                                            |       |      |

| ô.  | Make sure to set LCKR=00h before turning off LCD function                                                                                                                                                                                                                                                                                                                                                              |       |      |

| 7.  | Make sure to implement a mechanism to fine-tune LCD contrast level. The mechanism could be pin-option or keying-adjustment.                                                                                                                                                                                                                                                                                            |       |      |

| 3.  | Confirm PSG output mode: Current DAC or one of three PWM modes                                                                                                                                                                                                                                                                                                                                                         |       |      |

| Э.  | Before entering power down mode, turn off unused peripheral such as LCD controller, PSG, Current DAC and LVD                                                                                                                                                                                                                                                                                                           |       |      |

| 10. | Confirm I/O direction, default state and function-enable bits. Enable pull-up for<br>unused input pins                                                                                                                                                                                                                                                                                                                 |       |      |

| 11. | Read from an input port after the signals are stable. Ex. when doing key scan, delay 12 us from a new scan value then read the return lines.                                                                                                                                                                                                                                                                           |       |      |

| 12. | If an input connects to VCC or GND directly, make sure to remove any DC current from internal pull-up/down resistor after the status is read.                                                                                                                                                                                                                                                                          |       |      |

| 13. | Do not use "read-modify-write" instructions, e.g. ROR and SMB0, to the registers that are read-only, write-only or have different functions for read and write. The registers at least include PA ~ PF, PL, PCL, PSGxA, PSGxB, TxCH, TxCL, PRS, BTSR, BTC, MULL, MULH, MISC, SYS, IREQL, IREQH, LSSAL, LSSAH, LVPW, LCKR, LFRA, LPAL, SDATAH, SDATAL, SSR, DMSL, DMSH, DMDL, DMDH, DCNTL, DCNTH, LVCTR, UDATA and USR. |       |      |

| 14. | Disable unused functions and reserve "RTI" instruction for unused interrupt vectors                                                                                                                                                                                                                                                                                                                                    |       |      |

| 15. | Always disable interrupt function (by an 'SEI' instruction) when modifying the IENAL, IENAH, IREQL and IREQH registers.                                                                                                                                                                                                                                                                                                |       |      |

| 16. | Check stack memory is limited within 256 bytes.                                                                                                                                                                                                                                                                                                                                                                        |       |      |

| 17. | Design a test mode to check every possible function                                                                                                                                                                                                                                                                                                                                                                    |       |      |

| 18. | Follow the standard operation flow of using LCDCK=32KHz.                                                                                                                                                                                                                                                                                                                                                               |       |      |

| 19. | Use ST2600B (enable ST2602B EV mode), to develop the whole system., and verify every functions, especially sound quality and LCD performance.                                                                                                                                                                                                                                                                          |       |      |

|     | RC-type OSC has inter-sample variation.<br>For frequency-sensitive application (for example:IR communication and speech<br>sampling rate), please use 32KHz_OSC to calibrate RC-type OSC by firmware<br>Fill up ROM until there has no empty place. (total 131072 bytes)                                                                                                                                               |       |      |

# ST26xxB application note:

#### Content:

- 1. PSG: Current-DAC and PWM application circuit

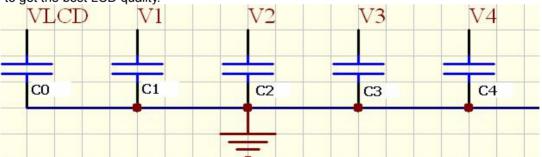

- 2. Methods to make up LCD voltage deviation

- 3. Vertical Cross talk on LCD display

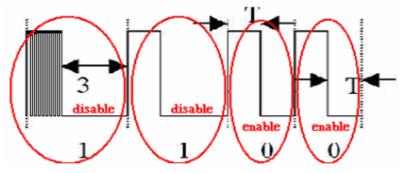

- 4. How to use IrDA mode to generate 38kHz carrier with data?

- 5. LCDCK=32k clock source on ST2602B/ST2608B display

- 6. System clock switching from OSC to OSCX

- 7. Measure RC-OSC system clock

- 8. IrDA mode application note

- 9. ST26xx UART details

- 10. IrDA BGRCK generation source

- 11. OC-OSC / X'tal application circuit

- 12. LCD blink cause by PSG

- 13. How to measure the internal current of ST2600B?

- 14. Ways to save power consumption

- 15. 32KHz (OSCX) application circuit

- 16. ST26XX+ST8008 CASCADE MODE CONNECTION

- 17. Standard flow for switching I/O and segment

- 18. LCDCK=32K with cascade mode

- 19. User Manual for ST2600B external bus usage

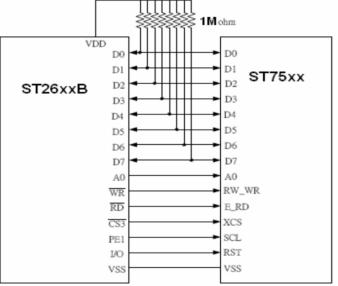

- 20. Pull-up resistance of D0~D7 for current issue when using ST75xx

Version 1.09

## <PSG: Current-DAC and PWM application circuit>

Description:

(These AP circuits are suitable for ST26xx series IC)

#### <Methods to make up LCD voltage deviation >

Notice1: In order to cover the variation of VLCD of LCD panel, be sure to reserve pin-option by GPIO to change the status of VLCD( bit0:3 of register LREG). Here we suggest that there are at least 5-level of voltage pin-option for VLCD. If the GPIO is not enough to make pin-option, programmer can use key-return-line method for power on pin-option.

For example: make pin-option for change VLCD at.../5.6/5.8/6.0V/6.2V/6.4/...

Notice2: Programmer should add a contrast controller function to adjust VLCD for the convenience of end-user to change the contrast as they like.

For example: VLCD is pre-set at **6.2** by pin-option, end-users can also adjust the contrast.../5.8/5.9V/6.0V/**6.2V**/6.3/6.4/...by using contrast controller function.

Notice3: Verifying the performance of voice on ST2602/2604/2608 DEMO boards. Because ST2600B DVB can not provide the totally voice efficacy, such like the volume and the quality of voice. So we strongly suggest to verify voice playing on ST2602B/ST2608B DEMO boards before MASK. (Ps...Because LCD SEG pins are shared with external EPROM, so the picture can not be verified on DEMO boards.)

#### <Vertical Cross talk on LCD display>

Solution: Vertical cross talk usually happens when the differential voltage of V0~V4 are not closely. In this case, increase C0~C4 (recommend > 1uF) will eliminate this problem. Fine tuning the value of capacitance to get the best LCD quality.

Sitronix

#### <How to use IrDA mode to generate 38kHz carrier with data?>

Port-E-2 (PE2) is shared with clock signal output function, and the frequency of this pin is programmable. Programmer can define which signal pattern is "0", and which signal is "1"

For example, using Timer\_interrupt to enable/disable PE2 function, and programmers can produce the signal pattern which means "0" or "1"

The same way, receive side can decode the signal by encode information.

## Sitronix

#### CDCK-22k clock source on ST2602B/ST2608B displays

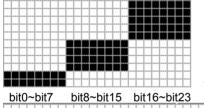

| <lcdc< th=""><th></th><th></th><th></th><th></th><th>10120</th><th></th><th>20001</th><th>, aispic</th><th>ay -</th><th></th><th></th></lcdc<> |              |       |                   |              | 10120           |                 | 20001            | , aispic                 | ay -     |                 |           |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-------------------|--------------|-----------------|-----------------|------------------|--------------------------|----------|-----------------|-----------|

| Address                                                                                                                                        | Name         | R/W   | Bit 7             | Bit 6        | Bit 5           | Bit 4           | Bit 3            | Bit 2                    | Bit 1    | Bit 0           | Default   |

|                                                                                                                                                |              | R/W   | LPWR              | BLNK         | REV             | CAS             | GL[3]            | GL[2]                    | GL[1]    | GL[0]           | 1000 0000 |

| Bit 3~2:                                                                                                                                       |              |       | D gray-leve       | selection    | bit             |                 |                  |                          |          |                 |           |

|                                                                                                                                                | 00 = B/W     |       |                   |              |                 |                 |                  |                          |          |                 |           |

|                                                                                                                                                | 01 = 4 gr    |       |                   |              |                 |                 |                  |                          |          |                 |           |