## IEEE 1394b THREE-PORT CABLE TRANSCEIVER/ARBITER

Check for Samples: TSB81BA3E

#### **FEATURES**

- Fully Supports Provisions of IEEE P1394b

Revision 1.33+ at 1-Gigabit Signaling Rates

- Fully Supports Provisions of IEEE 1394a-2000 and 1394-1995 Standard for High Performance Serial Bus

- Fully Interoperable With Firewire , i.LINK , and SB1394 <sup>™</sup>, Implementation of IEEE Std 1394

- Provides Three Fully Backward Compatible, (1394a-2000 Fully Compliant) Bilingual P1394b Cable Ports at up to 800 Megabits per Second (Mbits/s)

- Provides Three 1394a-2000 Fully Compliant Cable Ports at 100/200/400 Mbits/s

- Full 1394a-2000 Support Includes:

- Connection Debounce

- Arbitrated Short Reset

- Multispeed Concatenation

- Arbitration Acceleration

- Fly-By Concatenation

- Port Disable/Suspend/Resume

- Extended Resume Signaling for Compatibility With Legacy DV Devices

- Power-Down Features to Conserve Energy in Battery Powered Applications

- Low-Power Sleep Mode

- Fully Compliant With Open Host Controller Interface (HCI) Requirements

- Cable Power Presence Monitoring

- Cable Ports Monitor Line Conditions for Active Connection to Remote Node

- Register Bits Give Software Control of Contender Bit, Power Class Bits, Link Active Control Bit, and 1394a-2000 Features

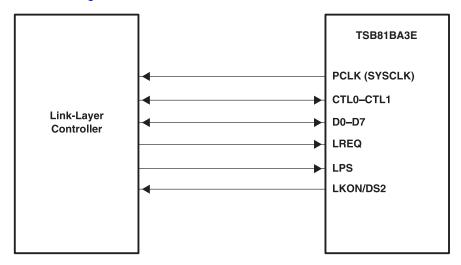

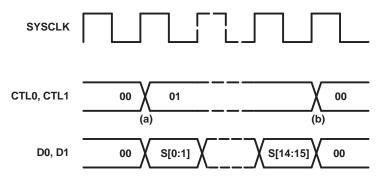

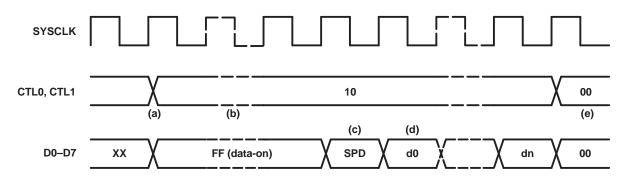

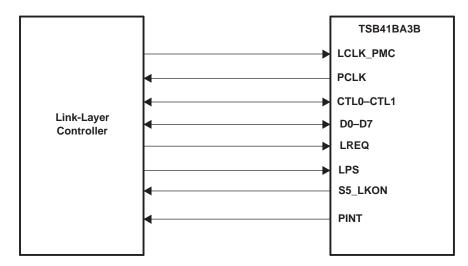

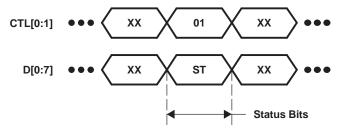

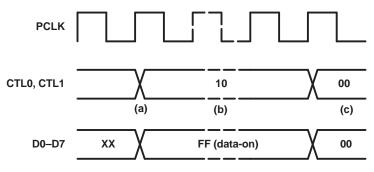

- Data Interface to Link-Layer Controller Pin Selectable From 1394a-2000 Mode (2/4/8 Parallel Bits at 49.152 MHz) or 1394b Mode (8 Parallel Bits at 98.304 MHz)

- Interface to Link-Layer Controller Supports Low Cost TI Bus-Holder Isolation

- Interoperable With Link-Layer Controllers Using 3.3-V Supplies

- Interoperable With Other 1394 Physical Layers (PHYs) Using 1.8-V, 3.3-V, and 5-V Supplies

- Low Jitter, External Crystal Oscillator Provides Transmit and Receive Data at 100/200/400/800 Mbits/s, and Link-Layer Controller Clock at 49.152 MHz and 98.304 MHz

- Separate Bias (TPBIAS) for Each Port

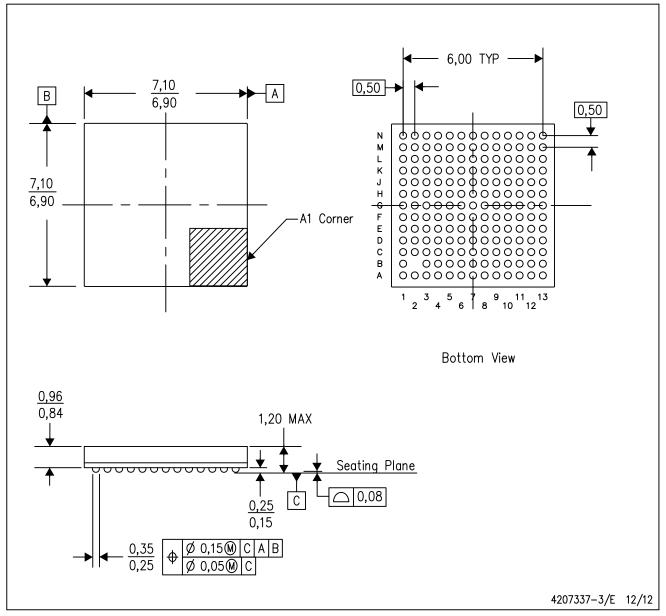

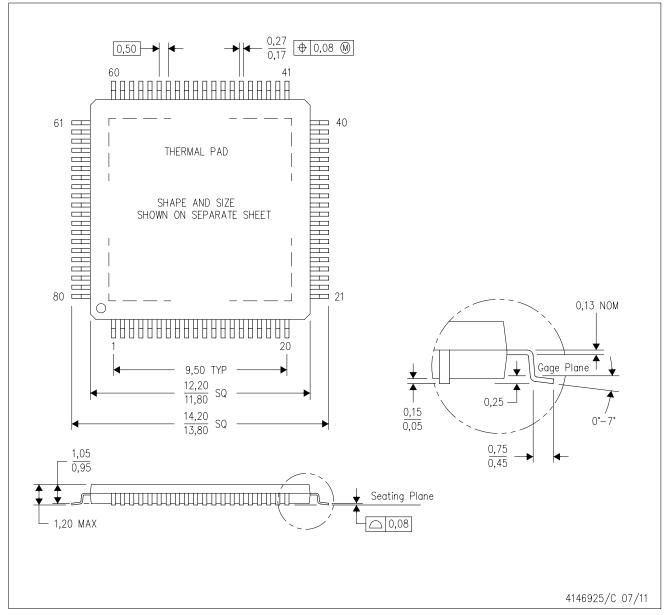

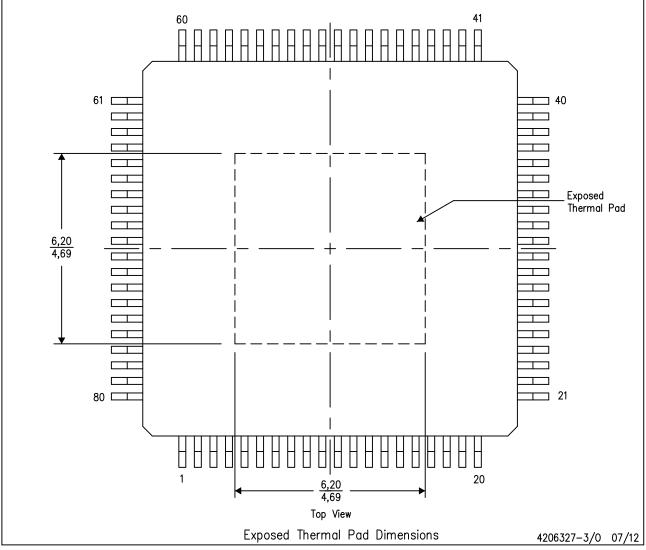

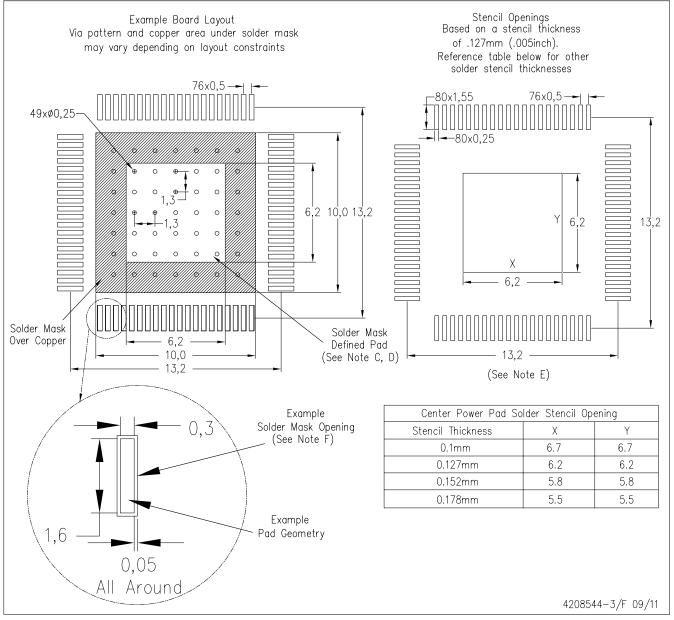

- Low Cost, High Performance 80-Pin TQFP (PFP) Thermally Enhanced Package and 168-Pin ZAJ (BGA) Package

- Software Device Reset (SWR)

- Fail-Safe Circuitry Senses Sudden Loss of Power to the Device and Disables the Ports to Ensure That the TSB81BA3E Does Not Load the TPBIAS of Any Connected Device and Blocks any Leakage From the Port Back to Power Plane

- The TSB81BA3E Has a 1394a-2000 Compliant Common-Mode Noise Filter on the Incoming Bias Detect Circuit to Filter Out Cross-Talk Noise

- The TSB81BA3E Is Port Programmable to Force 1394a Mode to Allow Use of 1394a Connectors (1394b Signaling Must Not Be Put Across 1394a Connectors or Cables)

- Internal Voltage Regulator Option

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## **DESCRIPTION**

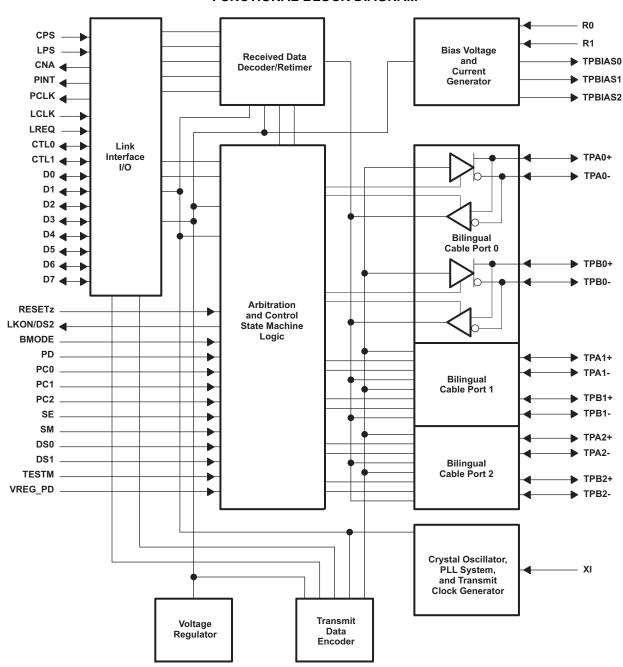

The TSB81BA3E provides the digital and analog transceiver functions needed to implement a three-port node in a cable-based IEEE 1394 network. Each cable port incorporates two differential line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and for packet reception and transmission. The TSB81BA3E is designed to interface with a link-layer controller (LLC), such as the TSB82AA2, TSB12LV21, TSB12LV26, TSB12LV32, TSB42AA4, TSB42AB4, TSB12LV01B, or TSB12LV01C. It also may be connected cable port to cable port to an integrated 1394 Link + PHY layer such as the TSB43AB2.

The TSB81BA3E can be powered by a single 3.3-V supply when the VREG\_PD terminal (terminal 73 on the PFP package and terminal B7 on the ZAJ package) is tied to GND. VREG\_PD enables the internal 3.3-V to 1.95-V regulator which provides the 1.95-V to the core. The When VREG\_PD is pulled high to VDD through at least a 1-k $\Omega$  resistor the TSB81BA3E internal regulator is off and the device can be powered by two separate external regulated supplies: 3.3-V for the I/Os and 1.95-V for the core. The core voltage is supplied to the PLLVDD-CORE and DVDD-CORE terminals to the requirements in the recommended operating conditions (1.95-V nominal). The PLLVDD-CORE terminals must be separated from the DVDD-CORE terminals. The PLLVDD-CORE and the DVDD-CORE terminals must be decoupled with 1 uF capacitors to stabilze the respective supply. Additional 0.10uF and 0.01uF high-frequency bypass capacitors may also be used. The separation between DVDD-CORE and PLLVDD-CORE may be implemented by separate power supply rails, or by a single power supply rail, where the DVDD-CORE and PLLVDD-CORE are separated by a filter network to keep noise from the PLLVDD-CORE supply.

The TSB81BA3E requires an external 98.304-MHz crystal oscillator to generate a reference clock. The external clock drives an internal phase-locked loop (PLL), which generates the required reference signal. This reference signal provides the clock signals that control transmission of the outbound encoded information. A 49.152-MHz clock signal is supplied to the associated LLC for synchronization of the two devices and is used for resynchronization of the received data when operating the PHY-link interface in compliance with the IEEE 1394a-2000 standard. A 98.304-MHz clock signal is supplied to the associated LLC for synchronization of the two devices when operating the PHY-link interface in compliance with the IEEE P1394b standard. The power down (PD) function, when enabled by asserting the PD terminal high, stops operation of the PLL.

Data bits to be transmitted through the cable ports are received from the LLC on two-, four-, or eight-bit parallel paths (depending on the requested transmission speed and PHY-link interface mode of operation). They are latched internally, combined serially, encoded, and transmitted at 98.304, 196.608, 393.216, 491.52, or 983.04 Mbits/s (referred to as S100, S200, S400, S400B, or S800 speed, respectively) as the outbound information stream.

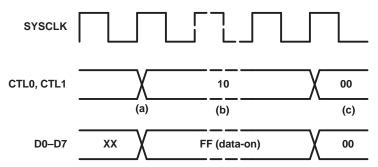

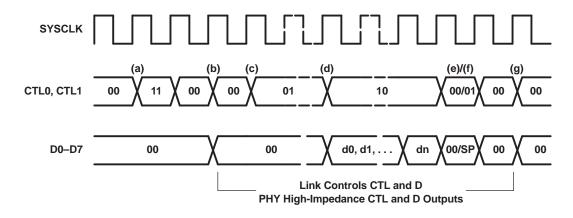

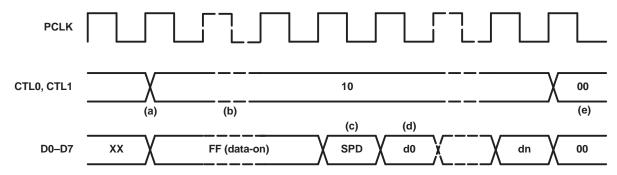

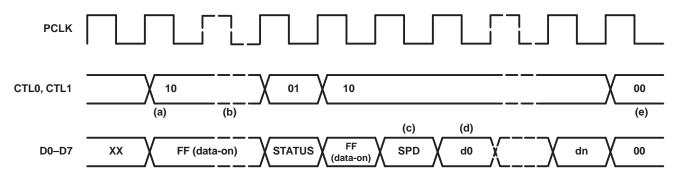

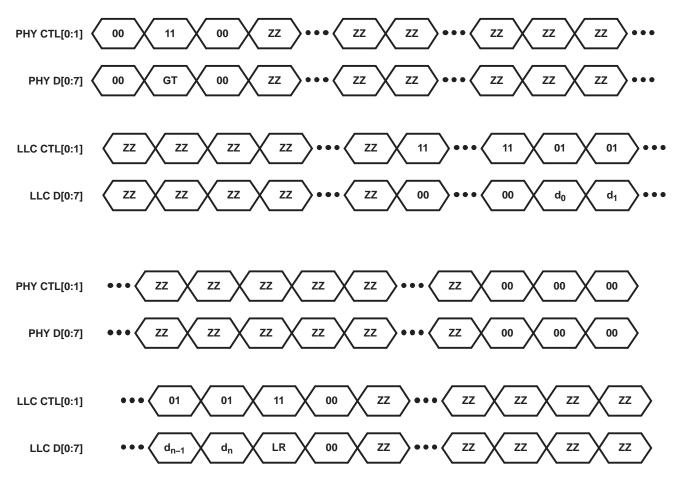

The PHY-link interface can follow either the IEEE 1394a-2000 protocol or the IEEE 1394b-2002 protocol. When using a 1394a-2000 LLC such as the TSB12LV26, the BMODE terminal must be deasserted. The PHY-link interface then operates in accordance with the legacy 1394a-2000 standard. When using a 1394b LLC such as the TSB82AA2, the BMODE terminal must be asserted. The PHY-link interface then conforms to the P1394b standard.

The cable interface can follow either the IEEE 1394a-2000 protocol or the 1394b protocol on all ports. The mode of operation is determined by the interface capabilities of the ports being connected. When any of the three ports is connected to a 1394a-2000 compliant device, the cable interface on that port operates in the 1394a-2000 data-strobe mode at a compatible S100, S200, or S400 speed. When a bilingual port is connected to a 1394b compliant node, the cable interface on that port operates per the P1394b standard at S400B or S800 speed. The TSB81BA3E automatically determines the correct cable interface connection method for the bilingual ports.

#### NOTE

The BMODE terminal does not select the cable interface mode of operation. The BMODE terminal selects the PHY-link interface mode of operation and affects the arbitration modes on the cable. When the BMODE terminal is deasserted, BOSS arbitration is disabled.

During packet reception the serial data bits are split into two-, four-, or eight-bit parallel streams (depending upon the indicated receive speed and the PHY-link interface mode of operation), resynchronized to the local system clock and sent to the associated LLC. The received data is also transmitted (repeated) on the other connected and active cable ports.

www.ti.com

During packet reception the serial data bits are split into two-, four-, or eight-bit parallel streams (depending upon the indicated receive speed and the PHY-link interface mode of operation), resynchronized to the local system clock and sent to the associated LLC. The received data is also transmitted (repeated) on the other connected and active cable ports.

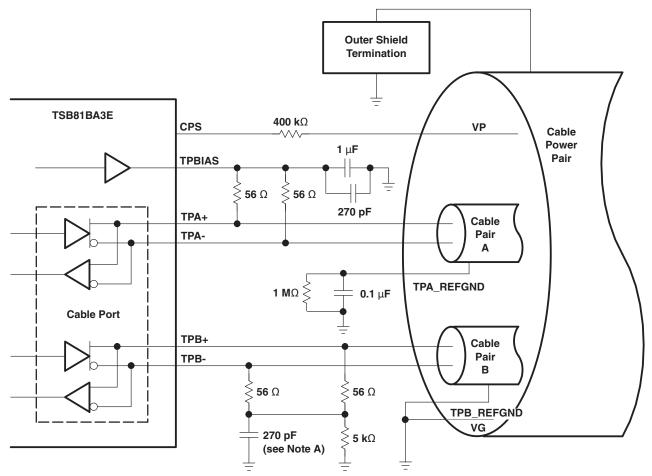

Both the twisted pair A (TPA) and the twisted pair B (TPB) cable interfaces incorporate differential comparators to monitor the line states during initialization and arbitration when connected to a 1394a-2000 compliant device. The outputs of these comparators are used by the internal logic to determine the arbitration status. The TPA channel monitors the incoming cable common-mode voltage. The value of this common-mode voltage is used during 1394a-mode arbitration and sets the speed of the next packet transmission. In addition, the TPB channel monitors the incoming cable common-mode voltage on the TPB pair for the presence of the remotely supplied twisted pair bias (TPBIAS) voltage.

When connected to a 1394a-2000 compliant node, the TSB81BA3E provides a 1.86-V nominal bias voltage at the TPBIAS terminal for port termination. The PHY contains three independent TPBIAS circuits (one for each port). This bias voltage, when seen through a cable by a remote receiver, indicates the presence of an active connection. This bias voltage source must be stabilized by an external filter capacitor of 1  $\mu$ F.

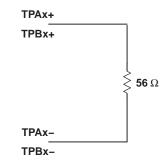

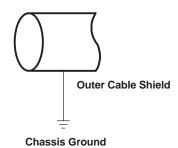

The line drivers in the TSB81BA3E are designed to work with external  $112-\Omega$  termination resistor networks to match the  $110-\Omega$  cable impedance. One termination network is required at each end of a twisted-pair cable. Each network is composed of a pair of series-connected ~ $56-\Omega$  resistors. The midpoint of the pair of resistors that are connected to the TPA terminals is connected to its corresponding TPBIAS voltage terminal. The midpoint of the pair of resistors that are directly connected to the TPB terminals is coupled to ground through a parallel RC network with recommended values of 5 k $\Omega$  and 270 pF. The values of the external line-termination resistors are designed to meet the standard specifications when connected in parallel with the internal receiver circuits. A precision external resistor connected between the R0 and R1 terminals sets the driver output current, along with other internal operating currents.

When the power supply of the TSB81BA3E is off while the twisted-pair cables are connected, the TSB81BA3E transmitter and receiver circuitry present a high-impedance signal to the cable that does not load the device at the other end of the cable.

When the TSB81BA3E is used without one or more of the ports brought out to a connector, the twisted-pair terminals of the unused ports must be terminated for reliable operation. For each unused port, the port must be forced to the 1394a-only mode (Data-Strobe-only mode), then the TPB+ and TPB- terminals can be tied together and then pulled to ground; or the TPB+ and TPB- terminals can be connected to the suggested normal termination network. The TPA+ and TPA- terminals of an unused port can be left unconnected. The TPBIAS terminal can be connected to a  $1-\mu F$  capacitor to ground or left unconnected.

To operate a port as a 1394b bilingual port, the force data-strobe-only terminal for the port (DS0, DS1, or DS2) needs to be pulled to ground through a 1-k $\Omega$  resistor. The port must be operated in the 1394b bilingual mode whenever a 1394b bilingual or a 1394b beta-only connector is connected to the port. To operate the port as a 1394a-only port, the force data-strobe-only terminal (DS0, DS1, or DS2) needs to be pulled to 3.3 V V<sub>CC</sub> through a 1-k $\Omega$  resistor. The only time the port must be forced to the data-strobe-only mode is if the port is connected to a 1394a connector (either 6 pin, which is recommended, or 4 pin). This mode is provided to ensure that 1394b Signaling is never sent across a 1394a cable.

The TESTM, VREG\_PD, SE, and SM terminals are used to set up various manufacturing test conditions. For normal operation, the TESTM and VREG\_PD terminals must be connected to  $V_{DD}$  through a 1-k $\Omega$  resistor. The SE and SM terminals must be tied to ground through a 1-k $\Omega$  resistor.

Three package terminals are used as inputs to set the default value for three configuration status bits in the self-ID packet. They may be pulled high through a  $1-k\Omega$  resistor or hardwired low as a function of the equipment design. The PC0, PC1, and PC2 terminals indicate the default power class status for the node (the need for power from the cable or the ability to supply power to the cable). The contender bit in the PHY register set indicates that the node is a contender either for the isochronous resource manager (IRM) or for the bus manager (BM). On the TSB81BA3E, this bit may only be set by a write to the PHY register set. If a node desires to be a contender for IRM or BM, then the node software must set this bit in the PHY register set.

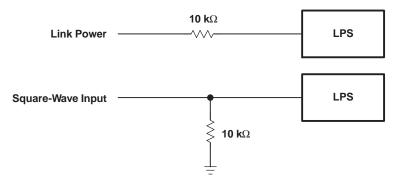

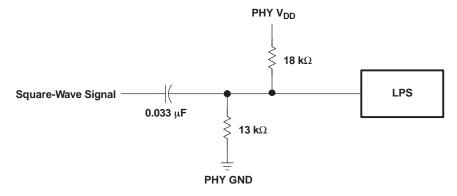

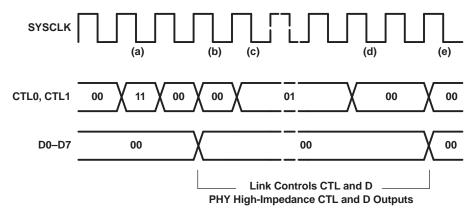

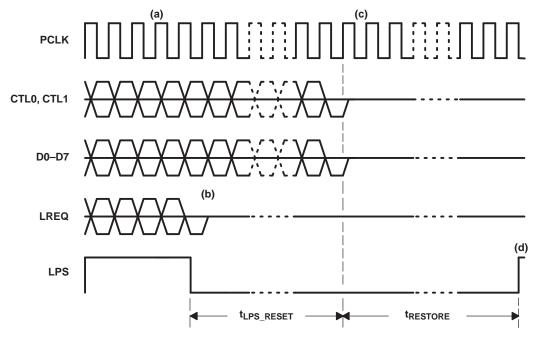

The LPS (link power status) terminal works with the LKON/DS2 terminal to manage the power usage in the node. The LPS signal from the LLC is used with the LCtrl bit (see Table 1 and Table 2 in the Application Information section) to indicate the active/power status of the LLC. The LPS signal also resets, disables, and initializes the PHY-LLC interface (the state of the PHY-LCC interface is controlled solely by the LPS input regardless of the state of the LCtrl bit).

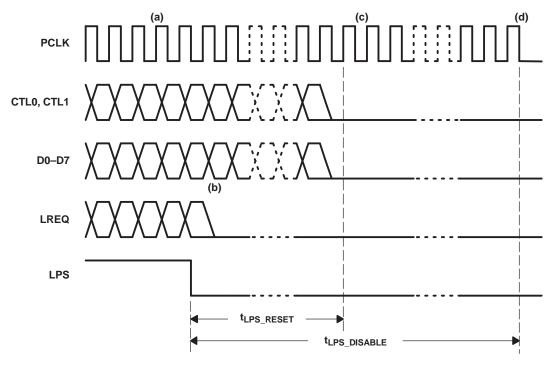

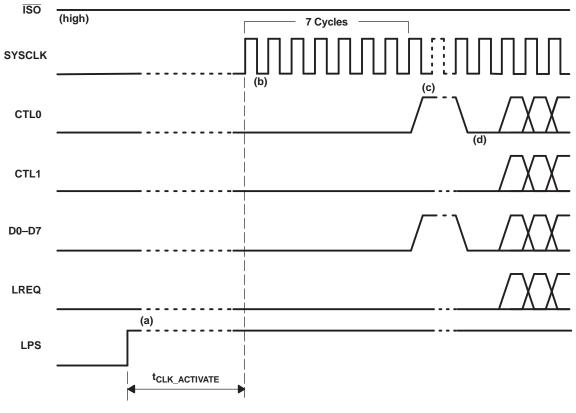

The LPS input is considered inactive if it remains low for more than the LPS\_RESET time (see the LPS terminal definition) and is considered active otherwise. When the TSB81BA3E detects that the LPS input is inactive, the PHY-LLC interface is placed into a low-power reset state in which the CTL and D outputs are held in the logic 0 state and the LREQ input is ignored; however, the PCLK output remains active. If the LPS input remains low for more than the LPS\_DISABLE time (see the LPS terminal definition), then the PHY-LLC interface is put into a low-power disabled state in which the PCLK output is also held inactive. The TSB81BA3E continues the necessary repeater functions required for normal network operation regardless of the state of the PHY-LLC interface. When the interface is in the reset or disabled state and the LPS input is again observed active, the PHY initializes the interface and returns to normal operation. The PHY-LLC interface is also held in the disabled state during hardware reset. When the LPS terminal is returned to an active state after being sensed as having entered the LPS\_DISABLE time, the TSB81BA3E issues a bus reset. This broadcasts the node self-ID packet, which contains the updated L bit state (the PHY LLC now being accessible).

The PHY uses the LKON/DS2 terminal to notify the LLC to power up and become active. When activated, the output LKON/DS2 signal is a square wave. The PHY activates the LKON/DS2 output when the LLC is inactive and a wake-up event occurs. The LLC is considered inactive when either the LPS input is inactive, as described above, or the LCtrl bit is cleared to 0. A wake-up event occurs when a link-on PHY packet addressed to this node is received, or conditionally when a PHY interrupt occurs. The PHY deasserts the LKON/DS2 output when the LLC becomes active (both LPS sensed as active and the LCtrl bit set to 1). The PHY also deasserts the LKON/DS2 output when a bus reset occurs, unless a PHY interrupt condition exists, which would otherwise cause LKON/DS2 to be active. If the PHY is power cycled and the power class is 0 through 4, then the PHY asserts LKON/DS2 for approximately 167  $\mu s$  or until both the LPS is active and the LCTRL bit is 1.

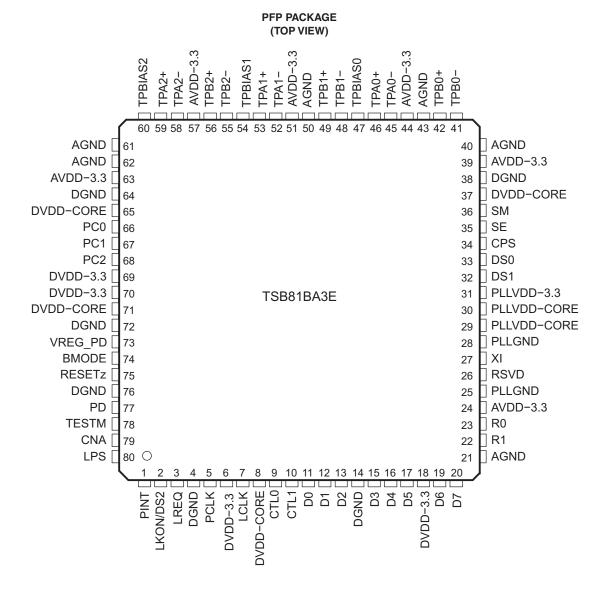

## **PIN ASSIGNMENTS**

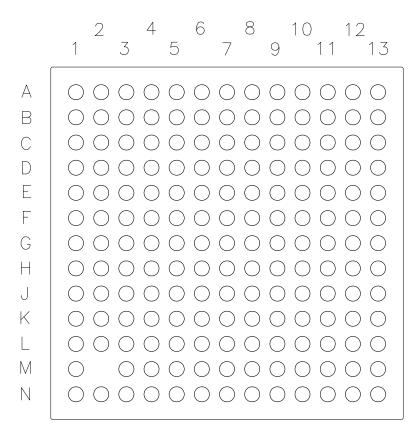

#### ZAJ PACKAGE (TOP VIEW)

#### **FUNCTIONAL BLOCK DIAGRAM**

#### TERMINAL FUNCTIONS

|                     |        | TERMINAL                             |                                                                                                                             | EKIVI | INAL FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|--------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |        | PFP                                  | ZAJ                                                                                                                         |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NAME                | TVDE   | PACKAGE                              | PACKAGE                                                                                                                     | 1/0   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NAME                | TYPE   | NO.<br>21, 40, 43,                   | NO.                                                                                                                         | I/O   | Analog circuit ground terminals. These terminals must be tied together to                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AGND <sup>(1)</sup> | Supply | 50, 61, 62                           | See DGND                                                                                                                    | -     | the low-impedance circuit board ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AVDD-3.3            | Supply | 24, 39, 44,<br>51, 57, 63            | M4, F10,<br>H10, J10,<br>E10                                                                                                | _     | Analog circuit power terminals. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled 0.1 $\mu F$ and 0.001 $\mu F$ . Lower frequency 10- $\mu F$ filtering capacitors are also recommended. These supply terminals are separated from the PLLVDD-CORE, PLLVDD-3.3, DVDD-CORE, and DVDD-3.3 terminals internal to the device to provide noise isolation. The PLLVDD-3.3, AVDD, and DVDD-3.3 terminals must be tied together with a low dc impedance connection on the circuit board. |

| BMODE               | CMOS   | 74                                   | В6                                                                                                                          | ı     | Beta-mode input. This terminal determines the PHY-link interface connection protocol. When logic-high (asserted), the PHY-link interface complies with the 1394b-2002 B PHY-link interface. When logic-low (deasserted), the PHY-link interface complies with the legacy 1394a-2000 standard. When using an LLC such as the 1394b-2002 TSB82AA2, this terminal must be pulled high. When using an LLC such as the 1394a-2000 TSB12LV26, this terminal must be tied low.                                                                  |

|                     |        |                                      |                                                                                                                             |       | NOTE: The PHY-link interface cannot be changed between the different protocols during operation.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CNA                 | CMOS   | 79                                   | A2                                                                                                                          | 0     | Cable not active output. This terminal is asserted high when there are no ports receiving incoming bias voltage. When any port receives bias, this terminal goes low.                                                                                                                                                                                                                                                                                                                                                                    |

| CPS                 | CMOS   | 34                                   | N9                                                                                                                          | I     | Cable-power status input. This terminal is normally connected to cable power through a 400-k $\Omega$ resistor. This circuit drives an internal comparator that detects the presence of cable power. This transition from cable power sensed to cable power not sensed can be used to generate an interrupt to the LLC.                                                                                                                                                                                                                  |

| CTL0<br>CTL1        | CMOS   | 9<br>10                              | F1<br>G1                                                                                                                    | I/O   | Control I/Os. These bidirectional signals control communication between the TSB81BA3E and the LLC. Bus holders are built into these terminals.                                                                                                                                                                                                                                                                                                                                                                                           |

| D0-D7               | CMOS   | 11, 12, 13,<br>15, 16, 17,<br>19, 20 | H1, H2, J2,<br>J1, K2, K1,<br>L1, M1                                                                                        | I/O   | Data I/Os. These are bidirectional data signals between the TSB82BA3 and the LLC. Bus holders are built into these terminals.                                                                                                                                                                                                                                                                                                                                                                                                            |

| DGND <sup>(1)</sup> | Supply | 4, 14, 38, 64,<br>72, 76             | E5, F4, F5,<br>F6, F7, F9,<br>G4, G5, G6,<br>G7, G8, G9,<br>G10, H4, H5,<br>H6, H7, H8,<br>J4, J5, J6,<br>J7, J8, K7,<br>L7 | _     | Digital circuit ground terminals. These terminals must be tied together to the low-impedance circuit board ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DS0                 | CMOS   | 33                                   | N8                                                                                                                          | ı     | Data-strobe-only mode for port 0. 1394a-only port 0 enable programming terminal. On hardware reset, this terminal allows the user to select whether port 0 acts like a 1394b bilingual port (terminal at logic 0) or as a 1394a-2000-only port (terminal at logic 1). Programming is accomplished by tying the terminal low through a 1-k $\Omega$ or less resistor (to enable 1394b bilingual mode) or high through a 1-k $\Omega$ or less resistor (to enable 1394a-2000-only mode). A bus holder is built into this terminal.         |

| DS1                 | CMOS   | 32                                   | M7                                                                                                                          | ı     | Data-strobe-only mode for port 1. 1394a-only port 1 enable programming terminal. On hardware reset, this terminal allows the user to select whether port 1 acts like a 1394b bilingual port (terminal at logic 0) or as a 1394a-2000-only port (terminal at logic 1). Programming is accomplished by tying the terminal low through a 1-k $\Omega$ or less resistor (to enable 1394b bilingual mode) or high through a 1-k $\Omega$ or less resistor (to enable 1394a-2000-only mode). A bus holder is built into this terminal.         |

(1) All AGND and DGND terminals are internally tied together in the ZAJ package.

|               |        | TERMINAL       |                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|--------|----------------|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |        | PFP<br>PACKAGE | ZAJ<br>PACKAGE |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NAME          | TYPE   | NO.            | NO.            | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DVDD-<br>CORE | Supply | 8, 37, 65, 71  | D9, K9, D8     | _   | Digital core circuit power terminals. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled 0.1 μF and 0.001 μF. An additional 1-μF capacitor is required for voltage regulation. These supply terminals are separated from the DVDD-3.3, PLLVDD-CORE, PLLVDD-3.3, and AVDD terminals internal to the device to provide noise isolation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DVDD-3.3      | Supply | 6, 18, 69, 70  | E4, K5, K6     | _   | Digital 3.3-V circuit power terminals. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled 0.1 $\mu F$ and 0.001 $\mu F$ . Lower-frequency 10- $\mu F$ filtering capacitors are also recommended. The DVDD-3.3 terminals must be tied together at a low-impedance point on the circuit board. These supply terminals are separated from the PLLVDD-CORE, PLLVDD-3.3, DVDD-CORE, and AVDD terminals internal to the device to provide noise isolation. The PLLVDD-3.3, AVDD, and DVDD-3.3 terminals must be tied together with a low dc impedance connection on the circuit board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LCLK          | CMOS   | 7              | G2             | I   | Link clock. Link-provided 98.304-MHz clock signal to synchronize data transfers from link to the PHY when the PHY-link interface is in the 1394b mode. A bus holder is built into this terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LKON/DS2      | CMOS   | 2              | D2             | I/O | Link-on output/Data-strobe-only input for port 2. This terminal may be connected to the link-on input terminal of the LLC through a 1-kΩ resistor if the link-on input is available on the link layer.  Data-strobe-only mode for port 2. 1394a-only port 0 enable programming terminal. On hardware reset, this terminal allows the user to select whether port 2 acts like a 1394b bilingual port (terminal at logic 0) or as a 1394a-2000-only port (terminal at logic 1). Programming is accomplished by tying the terminal low through a 1-kΩ or less resistor to enable 1394b bilingual mode or high through a 1-kΩ or less resistor to enable 1394a-2000-only mode. A bus holder is built into this terminal.  After hardware reset, this terminal is the link-on output, which notifies the LLC or other power-up logic to power up and become active. The link-on output is a square wave signal with a period of approximately 163 ns (8 PCLK cycles) when active. The link-on output is otherwise driven low, except during hardware reset when it is high impedance.  The link-on output is activated if the LLC is inactive (the LPS input inactive or the LCtrl bit cleared) and when one:  a. The PHY receives a link-on PHY packet addressed to this node.  b. The PEI (port-event interrupt) register bit is 1.  c. Any of the CTOI (configuration-timeout interrupt), CPSI (cable-power-status interrupt), or STOI (state-time-out interrupt) register bits is 1 and the RPIE (resuming-port interrupt enable) register bit is also 1.  d. The PHY is power-cycled and the power class is 0 through 4.  Once activated, the link-on output is active until the LLC becomes active (both the LPS input active and the LCtrl bit set). The PHY also deasserts the link-on output when a bus-reset occurs unless the link-on output is otherwise active because one of the interrupt bits is set (that is, the link-on output is active due solely to the reception of a link-on PHY packet).  In the case of power-cycling the PHY, the LKON signal must stop after 167 μs if the preceding conditions have n |

Copyright © 2009–2010, Texas Instruments Incorporated

|                   |        | TERMINAL       |                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|--------|----------------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |        | PFP<br>PACKAGE | ZAJ<br>PACKAGE  |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NAME              | TYPE   | NO.            | NO.             | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   |        |                |                 |     | Link power status input. This terminal monitors the active/power status of the link-layer controller (LLC) and controls the state of the PHY-LLC interface. This terminal must be connected to either the $V_{DD}$ supplying the LLC through an approximately 1-k $\Omega$ resistor or to a pulsed output that is active when the LLC is powered. A pulsed signal must be used when an isolation barrier exists between the LLC and PHY (see Figure 8). The LPS input is considered inactive if it is sampled low by the PHY for |

| LPS               |        |                |                 |     | more than an LPS_RESET time (~2.6 µs), and is considered active otherwise (that is, asserted steady high or an oscillating signal with a low time less than 2.6 µs). The LPS input must be high for at least 22 ns to be observed as high by the PHY.                                                                                                                                                                                                                                                                            |

| LPS               | CMOS   | 80             | D3              | I   | When the TSB81BA3E detects that the LPS input is inactive, it places the PHY-LLC interface into a low-power reset state. In the reset state, the CTL (CTL0 and CTL1) and D (D0 to D7) outputs are held in the logic 0 state and the LREQ input is ignored; however, the PCLK output remains active. If the LPS input remains low for more than an LPS_DISABLE time (~26 $\mu$ s), then the PHY-LLC interface is put into a low-power disabled state in which the PCLK output is also held inactive.                              |

|                   |        |                |                 |     | The LLC state that is communicated in the self-ID packet is considered active only if both the LPS input is active and the LCtrl register bit is set to 1. The LLC state that is communicated in the self-ID packet is considered inactive if either the LPS input is inactive or the LCtrl register bit is cleared to 0.                                                                                                                                                                                                        |

| LREQ              | CMOS   | 3              | E1              | I   | LLC request input. The LLC uses this input to initiate a service request to the TSB81BA3E. A bus holder is built into this terminal.                                                                                                                                                                                                                                                                                                                                                                                             |

| PC0<br>PC1<br>PC2 | CMOS   | 66<br>67<br>68 | C11<br>A9<br>B8 | I   | Power class programming inputs. On hardware reset, these inputs set the default value of the power class indicated during self-ID. Programming is done by tying the terminals high through a 1-k $\Omega$ or smaller resistor or by tying directly to ground through a 1-k $\Omega$ or smaller resistor. Bus holders are built into these terminals.                                                                                                                                                                             |

| PCLK              | CMOS   | 5              | F2              | 0   | PHY clock. Provides a 98.304-MHz clock signal, synchronized with data transfers, to the LLC when the PHY-link interface is operating in the 1394b mode (BMODE asserted). PCLK output provides a 49.152-MHz clock signal, synchronized with data transfers, to the LLC when the PHY-link interface is in legacy 1394a-2000 (BMODE input deasserted).                                                                                                                                                                              |

| PD                | CMOS   | 77             | В3              | I   | Power-down input. A high on this terminal turns off all internal circuitry except the cable-active monitor circuits, which control the CNA output.  Asserting the PD input high also activates an internal pulldown on the RESET terminal to force a reset of the internal control logic.                                                                                                                                                                                                                                        |

| PINT              | CMOS   | 1              | E3              | 0   | PHY interrupt. The PHY uses this output to serially transfer status and interrupt information to the link when PHY-link interface is in the 1394b mode. A bus holder is built into this terminal.                                                                                                                                                                                                                                                                                                                                |

| PLLGND            | Supply | 25, 28         | F8, N4          | _   | PLL circuit ground terminals. These terminals must be tied together to the low-impedance circuit board ground plane.                                                                                                                                                                                                                                                                                                                                                                                                             |

| PLLVDD-<br>CORE   | Supply | 29, 30         | N6              | _   | PLL core circuit power terminals. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled 0.1 μF and 0.001 μF. An additional 1-μF capacitor is required for voltage regulation. The PLLVDD-CORE terminals must be separate from the DVDD-CORE terminals. These supply terminals are separated from the DVDD-CORE, DVDD-3.                                                                                                                                                      |

|                                  |         | TERMINAL             |                          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|---------|----------------------|--------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |         | PFP<br>PACKAGE       | ZAJ<br>PACKAGE           |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NAME                             | TYPE    | NO.                  | NO.                      | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PLLVDD-<br>3.3                   | Supply  | 31                   | N7                       | _   | PLL 3.3-V circuit power terminal. A combination of high-frequency decoupling capacitors near the terminal are suggested, such as paralleled 0.1 μF and 0.001 μF. Lower frequency 10-μF filtering capacitors are also recommended. This supply terminal is separated from the DVDD-CORE, DVDD-3.3, PLLVDD-CORE, and AVDD-3.3 terminals internal to the device to provide noise isolation. The DVDD-3.3 terminals must be tied together at a low-impedance point on the circuit board. The PLLVDD-3.3, AVDD-3.3, and DVDD-3.3 terminals must be tied together with a low dc impedance connection. |

| RESET                            | CMOS    | 75                   | A6                       | I   | Logic reset input. Asserting this terminal low resets the internal logic. An internal pullup resistor to V <sub>DD</sub> is provided so only an external delay capacitor is required for proper power-up operation (see <i>power-up reset</i> in the <i>Applications Information</i> section).  The RESET terminal also incorporates an internal pulldown, which is activated when the PD input is asserted high. This input is otherwise a                                                                                                                                                     |

|                                  |         |                      |                          |     | standard logic input, and can also be driven by an open-drain-type driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RSVD                             | Osc Out | 26                   | M5                       | 0   | This terminal must normally be left unconnected. When this terminal is probed, the terminal shows a 98.304-MHz signal. If this is perceived as an EMI problem, then the terminal may be pulled to ground through a 10-k $\Omega$ resistor. However, this causes an increase of up to 340 $\mu A$ in device current consumption.                                                                                                                                                                                                                                                                 |

| R0<br>R1                         | Bias    | 23<br>22             | N3<br>N2                 | _   | Current setting resistor terminals. These terminals are connected to a precision external resistance to set the internal operating currents and cable driver output currents. A resistance of 6.34 k $\Omega$ , $\pm 1\%$ , is required to meet the IEEE Std 1394-1995 output voltage limits.                                                                                                                                                                                                                                                                                                   |

| SE                               | CMOS    | 35                   | M10                      | I   | Test control input. This input is used in the manufacturing test of the TSB81BA3E. For normal use this terminal must be pulled low either through a 1-k $\Omega$ resistor to GND or directly to GND.                                                                                                                                                                                                                                                                                                                                                                                            |

| SM                               | CMOS    | 36                   | N10                      | I   | Test control input. This input is used in the manufacturing test of the TSB81BA3E. For normal use this terminal must be pulled low either through a 1-k $\Omega$ resistor to GND or directly to GND.                                                                                                                                                                                                                                                                                                                                                                                            |

| TESTM                            | CMOS    | 78                   | А3                       | ı   | Test control input. This input is used in the manufacturing test of the TSB81BA3E. For normal use this terminal must be pulled high through a 1-k $\Omega$ resistor to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                        |

| VREG_PD                          | CMOS    | 73                   | В7                       | I   | Voltage regulator power-down input. When asserted logic high, this pin will power-down the internal 3.3-V to 1.95-V regulator. For single 3.3-V supply operation, this pin should be tied to GND. If an external regulator is used to supply the 1.95-V PLLVDD-CORE and DVDD-CORE power rails this terminals should be pulled to Vcc through a 1-k $\Omega$ resistor to VDD.                                                                                                                                                                                                                    |

| TPA0-<br>TPA0+<br>TPB0-<br>TPB0+ | Cable   | 45<br>46<br>41<br>42 | K13<br>J13<br>M13<br>L13 | I/O | Port-0 twisted-pair differential-signal terminals. Board traces from each pair of positive and negative differential signal terminals must be kept matched and as short as possible to the external load resistors and to the cable connector. Request the S800 1394b layout recommendations document from your Texas Instruments representative.                                                                                                                                                                                                                                               |

| TPA1-<br>TPA1+<br>TPB1-<br>TPB1+ | Cable   | 52<br>53<br>48<br>49 | F13<br>E13<br>H13<br>G13 | I/O | Port-1 twisted-pair differential-signal terminals. Board traces from each pair of positive and negative differential signal terminals must be kept matched and as short as possible to the external load resistors and to the cable connector. Request the S800 1394b layout recommendations document from your Texas Instruments representative.                                                                                                                                                                                                                                               |

| TPA2-<br>TPA2+<br>TPB2-<br>TPB2+ | Cable   | 58<br>59<br>55<br>56 | B13<br>A13<br>D13<br>C13 | I/O | Port-2 twisted-pair differential-signal terminals. Board traces from each pair of positive and negative differential signal terminals must be kept matched and as short as possible to the external load resistors and to the cable connector. Request the S800 1394b layout recommendations document from your Texas Instruments representative.                                                                                                                                                                                                                                               |

|                               |        | TERMINAL       |                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-------------------------------|--------|----------------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                               |        | PFP<br>PACKAGE | ZAJ<br>PACKAGE    |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| NAME                          | TYPE   | NO.            | NO.               | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| TPBIAS0<br>TPBIAS1<br>TPBIAS2 | Cable  | 47<br>54<br>60 | J12<br>E12<br>A12 | I/O | Twisted-pair bias output and signal detect input. This provides the 1.86-V nominal bias voltage needed for proper operation of the twisted-pair cable drivers and receivers, and for signaling to the remote nodes that there is an active cable connection in 1394a-2000 mode. Each of these terminals, except for an unused port, must be decoupled with a 1-μF capacitor to ground. For the unused port, this terminal can be left unconnected. Please request the S800 1394b layout recommendation documents from your TI representative.                                                                  |  |  |

| ΧI                            | Osc In | 27             | N5                | _   | Oscillator input. This terminal connects to a 98.304-MHz low jitter external oscillator. The XI terminal is a 1.8-V CMOS input. Oscillator jitter must be 5 ps RMS or better. If only 3.3-V oscillators can be acquired, then great care must be taken to not introduce significant jitter by the means used to level shift from 3.3 V to 1.8 V. If a resistor divider is used, then a high current oscillator and low-value resistors must be used to minimize RC time constants. If a level-shifting circuit is used, then it must introduce very little jitter. Please see layout recommendations document. |  |  |

## Absolute Maximum Ratings(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                                                      |                                                | MIN  | MAX                   | UNIT        |

|------------------|------------------------------------------------------|------------------------------------------------|------|-----------------------|-------------|

| $V_{DD}$         | Supply voltage range <sup>(2)</sup>                  |                                                | -0.3 | 4                     | V           |

| VI               | Input voltage range <sup>(2)</sup>                   |                                                | -0.5 | V <sub>DD</sub> + 0.5 | V           |

| Vo               | Output voltage range at any output                   |                                                | -0.5 | V <sub>DD</sub> + 0.5 | V           |

|                  | Continuous total power dissipation                   |                                                | See  | Dissipation Ra        | tings Table |

| _                | On and in a face of the second second                | TSB81BA3E                                      | 0    | 70                    | 00          |

| $T_A$            | Operating free-air temperature                       | TSB81BA3EI                                     | -40  | 85                    | °C          |

| T <sub>stg</sub> | Storage temperature range                            | <u>,                                      </u> | 65   | 150                   | °C          |

|                  | Lead temperature 1.6 mm (1/16 in) from case for 10 s |                                                |      | 260                   | °C          |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **Dissipation Ratings**

| PACKAGE                | T <sub>A</sub> 25°C<br>POWER RATING | DERATING FACTOR <sup>(1)</sup> ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|------------------------|-------------------------------------|------------------------------------------------------------|---------------------------------------|---------------------------------------|

| PFP <sup>(2) (3)</sup> | 5.05 W                              | 52.5 mW/°C                                                 | 2.69 W                                | 1.9 W                                 |

| PFP <sup>(4)</sup> (3) | 3.05 W                              | 31.7 mW/°C                                                 | 1.62 W                                | 1.15 W                                |

<sup>(1)</sup> This is the inverse of the traditional junction-to-ambient thermal resistance ( $R_{\theta JA}$ ).

<sup>(2)</sup> All voltage values, except differential I/O bus voltages, are with respect to network ground.

<sup>2) 2-</sup>oz. trace and copper pad with solder.

<sup>(3)</sup> For more information, see the Texas Instruments application note PowerPAD™ Thermally Enhanced Package, (SLMA002).

<sup>(4) 2-</sup>oz. trace and copper pad without solder.

## RECOMMENDED OPERATING CONDITIONS

|                         |                                     |                                                  | MIN                      | TYP <sup>(1)</sup> | MAX                  | UNIT |

|-------------------------|-------------------------------------|--------------------------------------------------|--------------------------|--------------------|----------------------|------|

| 221                     | Complement                          | Source power node                                | 3.0                      | 3.3                | 3.6                  | V    |

| 3.3 V <sub>DD</sub>     | Supply voltage                      | Nonsource power node                             | 3.0(2)                   | 3.3                | 3.6                  | V    |

| Core<br>V <sub>DD</sub> | Supply voltage                      |                                                  | 1.85                     | 1.95               | 2.05                 | V    |

|                         |                                     | LREQ, CTL0, CTL1, D0-D7, LCLK                    | 2.6                      |                    |                      |      |

| V <sub>IH</sub>         | High-level input voltage            | LKON/DS2, PC0, PC1, PC2, PD, BMODE               | 0.7 ×<br>V <sub>DD</sub> |                    |                      | V    |

|                         |                                     | RESETz                                           | 0.6 ×<br>V <sub>DD</sub> |                    |                      |      |

|                         |                                     | LREQ, CTL0, CTL1, D0-D7, LCLK                    |                          |                    | 1.2                  |      |

| $V_{IL}$                | Low-level input voltage             | LKON/DS2, PC0, PC1, PC2, PD, BMODE               |                          |                    | $0.2 \times V_{DD}$  | V    |

|                         |                                     | RESETz                                           |                          |                    | $0.3 \times V_{DD}$  |      |

| $V_{OD}$                | 1394b Differential output voltage   |                                                  |                          | 700                |                      | mV   |

| $V_{CM}$                | 1394b Common-mode output voltage    |                                                  |                          | 1.5                |                      | V    |

| I                       | Supply current in low               | $V_{D D} = 3.3 V$                                |                          | 4                  |                      | mA   |

| I <sub>DD</sub>         | power/suspend <sup>(3)</sup>        | $V_{DD} = 3 V$                                   |                          | 3                  |                      | mA   |

| I <sub>OL/OH</sub>      | Output current                      | CTL0, CTL1, D0-D7, CNA, LKON/DS2, PINT, and PCLK | -4                       |                    | 4                    | mA   |

| Io                      | Output current                      | TPBIAS outputs                                   | -5.6                     |                    | 1.3                  | mA   |

| T <sub>A</sub>          | Operating ambient temperature range | TSB81BA3E                                        | 0                        |                    | 70                   | °C   |

| $T_J$                   | Junction temperature (4)            | TSB81BA3E                                        | 0                        |                    | 105                  | °C   |

| $V_{ID}$                | 1394b Differential input voltage    | Cable inputs, during data reception              | 200                      |                    | 800                  | mV   |

| $V_{ID}$                | 1394a Differential input voltage    | Cable inputs, during data reception              | 118                      |                    | 260                  | mV   |

| V ID                    | 1394a Dillerential Input Voltage    | Cable inputs, during arbitration                 | 168                      |                    | 265                  | IIIV |

| $V_{IC}$                | 1394a Common-mode input             | TPB cable inputs, source power node              | 0.4706                   |                    | 2.515                | V    |

| AIC.                    | voltage                             | TPB cable inputs, nonsource power node           | 0.4706                   |                    | 2.015 <sup>(2)</sup> | _ v  |

| t <sub>pu</sub>         | Power-up reset time                 | RESETz input                                     | 2 <sup>(5)</sup>         |                    |                      | ms   |

|                         |                                     | TPA, TPB cable inputs, S100 operation            |                          |                    | ±1.08                |      |

|                         | Receive input jitter                | TPA, TPB cable inputs, S200 operation            |                          |                    | ±0.5                 | ns   |

|                         |                                     | TPA, TPB cable inputs, S400 operation            | ±                        |                    | ±0.315               |      |

|                         |                                     | Between TPA and TPB cable inputs, S100 operation |                          |                    | ±0.8                 |      |

|                         | Receive input skew                  | Between TPA and TPB cable inputs, S200 operation | ±0.55                    |                    |                      | ns   |

|                         |                                     | Between TPA and TPB cable inputs, S400 operation |                          |                    |                      |      |

All typical values are at  $V_{DD}=3.3~V$  and  $T_A=25^{\circ}C$ . For a node that does not source power, see Section 4.2.2.2 in IEEE 1394a-2000. The low power/suspend mode assumes that the device is not receiving packets and it is toning.

The junction temperature reflects simulated conditions. The customer is responsible for verifying junction temperature. Time after valid clock received at PHY XI input terminal.

## ELECTRICAL CHARACTERISTICS Driver

over recommended ranges of operating conditions (unless otherwise noted)

|                    | PARAMETER                                         | TEST CONDITIONS                      | MIN                  | TYP MAX              | UNIT |

|--------------------|---------------------------------------------------|--------------------------------------|----------------------|----------------------|------|

| V <sub>OD</sub>    | Differential output voltage                       | 56 Ω, See Figure 1                   | 172                  | 265                  | mV   |

| I <sub>DIFF</sub>  | Driver difference current, TPA+, TPA-, TPB+, TPB- | Drivers enabled, speed signaling off | -1.05 <sup>(1)</sup> | 1.05 <sup>(1)</sup>  | mA   |