# High Performance Combo Controller for ATX Power Supplies

Housed in a SO-24WB package, the NCP1910 combines a state-of-the-art circuitry aimed to powering next generation of ATX or flat TVs converters. With a 65 or 100 kHz Continuous Conduction Mode Power Factor Controller and a LLC controller hosting a high-voltage driver, the NCP1910 is ready to power 85+ types of offline power supplies. To satisfy stringent efficiency considerations, the PFC circuit implements an adjustable frequency fold back to reduce switching losses as the load is going light. To cope with all the signal sequencing required by the ATX and flat TVs specifications, the controller includes several dedicated pins enabling handshake between the secondary and the primary sides. These signals include a power-good line but also a control pin which turns the controller on and off via an opto coupler. Safety-wise, a second OVP input offers the necessary redundancy in case the main feedback network would drift away. Finally, a fast fault input immediately reacts in presence of an over current condition by triggering an auto-recovery soft-start sequence.

## Features

- Fixed-Frequency 65 or 100 kHz CCM Power Factor Controller

- Average Current-Mode Control for Low Line Distortion

- Dynamic Response Enhancer Reduces Bulk Undershoot

- Independent Over Voltage Protection Sensing Pin with Latch-off Capability

- Adjustable Frequency Fold Back Improves Light Load Efficiency

- Adjustable Line Brown-Out Protection with 50 ms Delay to Help Meeting Hold-up Time Specifications

- Programmable Over current Threshold Leads to an Optimized Sensing Resistor

- ±1 A peak Current Drive Capability

- LLC Controller Operates from 25 kHz to 500 kHz

- On Board 600 V High-Voltage Drivers

- 1 A/0.5 A Sink/Source Capability

- Minimum Frequency Precision Down to ±3% Over Temperature Range

- Internally Fixed Dead-Time Value of 300 ns

- Adjustable Soft-Start Sequence

- Fast Fault Input with Soft-Start Trigger for Immediate Auto-recovery Protection

- On/Off Control Pin for Secondary-Based Remote Control

- On-Board 5 V Reference Voltage for Precise Thresholds/Hysteresis Adjustments

## **ON Semiconductor®**

http://onsemi.com

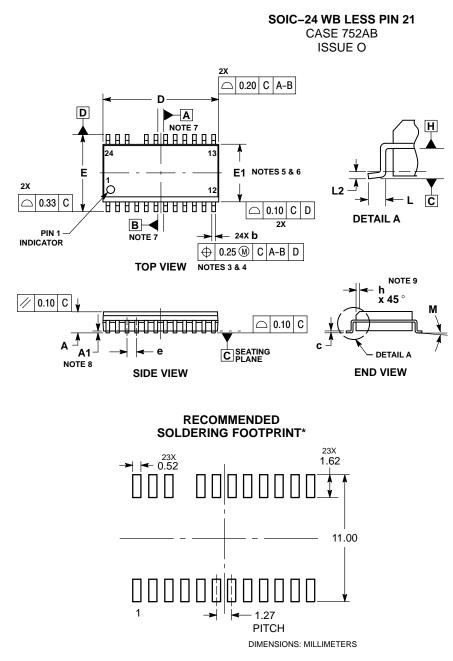

SO-24WB Less Pin 21 DW SUFFIX CASE 752AB

## MARKING DIAGRAM

- YY = Year WW = Work Week

- G = Pb-Free Package

- = FD-Fiee Fackage

## ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 35 of this data sheet.

- Power Good Output Management Signal

- A Version with Dual Ground Pinout (No Skip), B Version with Single Ground and Skip Operation for the LLC Controller

- 20 V Operation

- These are Pb-Free Devices

## **Typical Applications**

- Multi Output ATX Power Supplies (A version)

- Flat TVs Power Supplies (B version)

| 1-<br>SS Ш<br>Rt Ш<br>PG out Ш<br>ON/OFF Ш                                     | 0 | 24<br>⊐ Vboot<br>⊐ MU<br>⊐ Bridge                                            |

|--------------------------------------------------------------------------------|---|------------------------------------------------------------------------------|

| BO adj. U<br>Vref U<br>PG adj. U<br>OVP2 U<br>FB U<br>VCTRL U<br>VM U<br>LBO U |   | ML<br>V <sub>CC</sub><br>DRV<br>GND/PGND<br>Skip/AGND<br>CS/FF<br>CS<br>Fold |

Figure 1. Pin Connections

## **PIN DESCRIPTION**

| Pin No | Pin Name          | Function                                | Pin Description                                                                                                                                                          |

|--------|-------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | SS                | Soft-Start                              | A capacitor to ground sets the LLC soft-start duration                                                                                                                   |

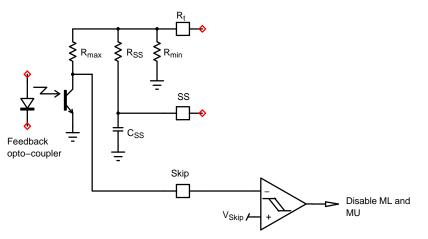

| 2      | Rt                | The LLC Feedback Pin                    | A resistive arrangement sets the maximum and minimum<br>switching frequencies with opto coupler-based feedback<br>capabilities.                                          |

| 3      | PG out            | The Open-Collector Power<br>Good Signal | This pin is low when $V_{\text{bulk}}$ is ok, opens when $V_{\text{bulk}}$ passes below a level adjusted by PGadj pin.                                                   |

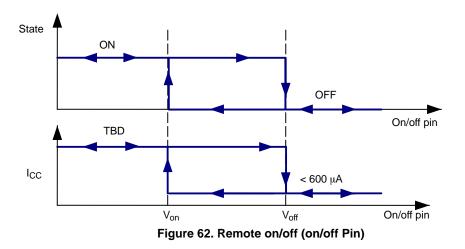

| 4      | on/off            | Remote Control                          | When pulled low, the circuit operates: the PFC starts first and once FB is in regulation, the LLC is authorized to work. When left open, the controller is in idle mode. |

| 5      | BO adj.           | Brown-Out Adjustment                    | This pin sets the on and off levels for the PFC powering the LLC converter                                                                                               |

| 6      | Vref              | The 5 V Reference Pin                   | This pin delivers a stable voltage for threshold adjustments                                                                                                             |

| 7      | PG adj.           | The Power Good Trip Level               | From the Vref pin, a dc level sets the trip point for the PFC bulk voltage at which the PG out signal is down.                                                           |

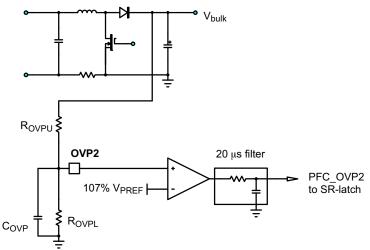

| 8      | OVP2              | Redundant OVP                           | A fully latched OVP monitoring the PFC bulk independently from FB pin.                                                                                                   |

| 9      | FB                | PFC Feedback                            | Monitors the boost bulk voltage and regulates it. It also serves as a quick auto-recovery OVP                                                                            |

| 10     | V <sub>CTRL</sub> | PFC Error Amplifier Output              | PFC error amplifier compensation pin                                                                                                                                     |

| 11     | V <sub>M</sub>    | PFC Current Amplifier Output            | A resistor to ground sets the maximum power level                                                                                                                        |

| 12     | LBO               | PFC Line Input Voltage Sensing          | Line feed forward and PFC brown-out                                                                                                                                      |

| 13     | Fold              | PFC Fold Back                           | This pin selects the power level at which the frequency starts to reduce gradually.                                                                                      |

| 14     | CS                | PFC Current Sense                       | This pin senses the inductor current and also programs the maximum sense voltage excursion                                                                               |

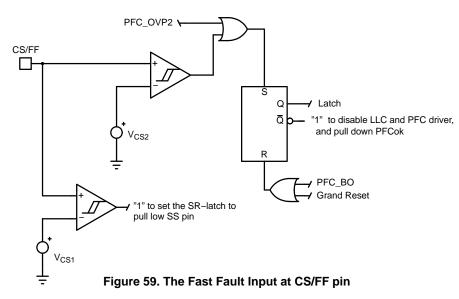

| 15     | CS/FF             | Fast-Fault Input                        | When pulled above 1 V, the LLC stops and re-starts via a full soft-start sequence.                                                                                       |

| 16     | Skip/AGND         | Skip (B)/AGND (A)                       | This pin is either used as the analog GND for the signal circuit (A) or for skip operation (B).                                                                          |

| 17     | GND/PGND          | GND (B)/PGND (A)                        | The controller ground for the driving loop (A) or the lump ground pin for all circuits (B)                                                                               |

| 18     | DRV               | PFC Drive Signal                        | The driving signal to the PFC power MOSFET                                                                                                                               |

| 19     | V <sub>CC</sub>   | The Controller Supply                   | The power supply pin for the controller, 20 V max.                                                                                                                       |

| 20     | ML                | Lower-Side MOSFET                       | Drive signal for the lower side half-bridge MOSFET                                                                                                                       |

| 22     | Bridge            | Half-Bridge                             | This pin connects to the LLC half-bridge                                                                                                                                 |

| 23     | MU                | Upper-Side MOSFET                       | Drive signal for the upper side half-bridge MOSFET                                                                                                                       |

| 24     | V <sub>boot</sub> | Bootstrapped Vcc                        | The bootstrapped $V_{CC}$ for the floating driver                                                                                                                        |

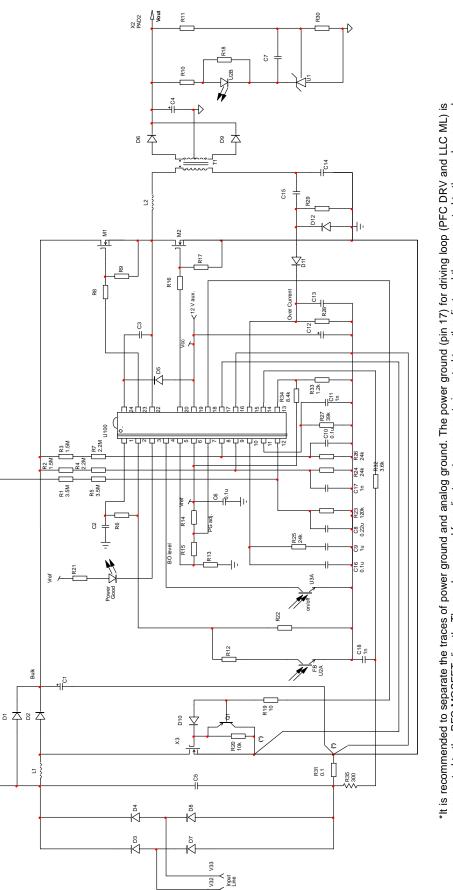

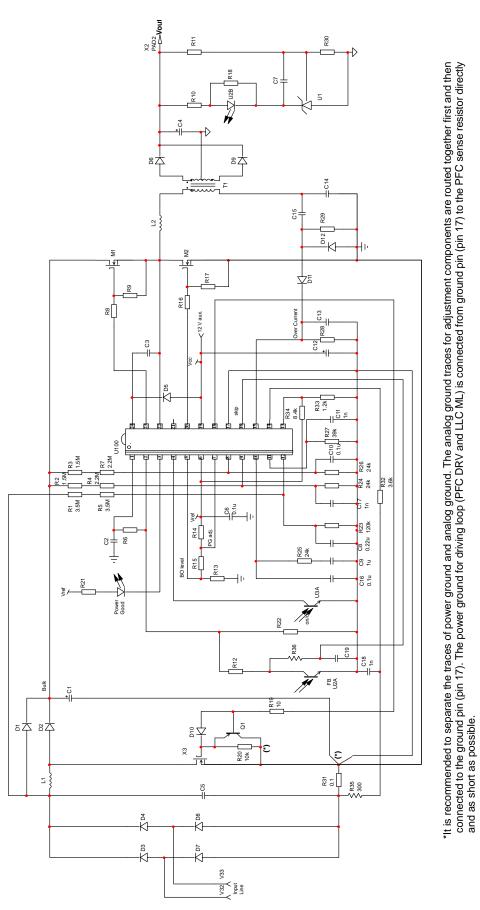

\*It is recommended to separate the traces of power ground and analog ground. The power ground (pin 17) for driving loop (PFC DRV and LLC ML) is connected to the PFC MOSFET directly. The analog ground for adjustment components is routed together first and then connected to the analog ground pin (pin 16) and the PFC sense resistor directly.

Figure 2. Typical Application Schematic in A Version

## **NCP1910**

Figure 3. Typical Application Schematic in B Version

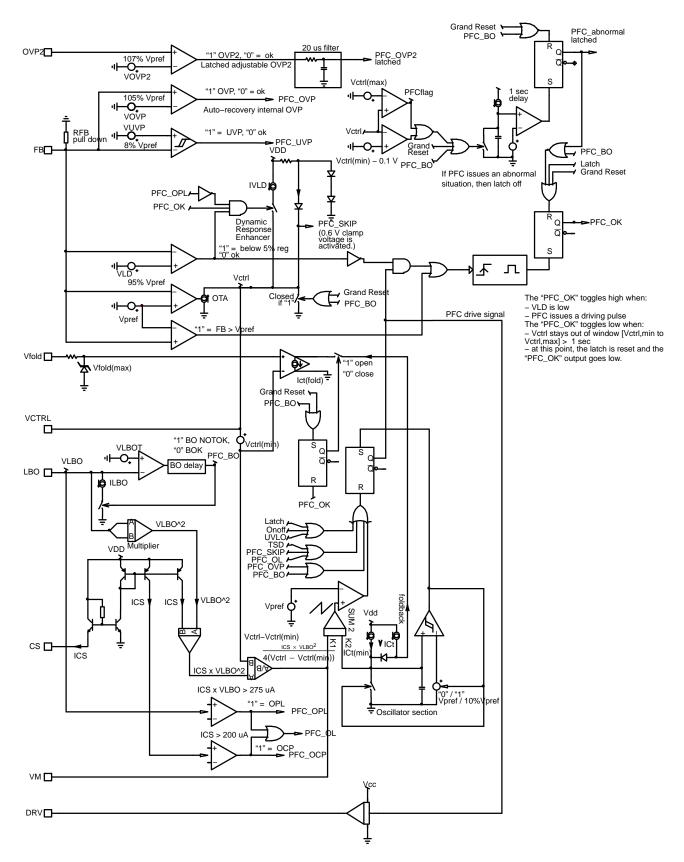

Figure 4. Internal PFC Block Diagram

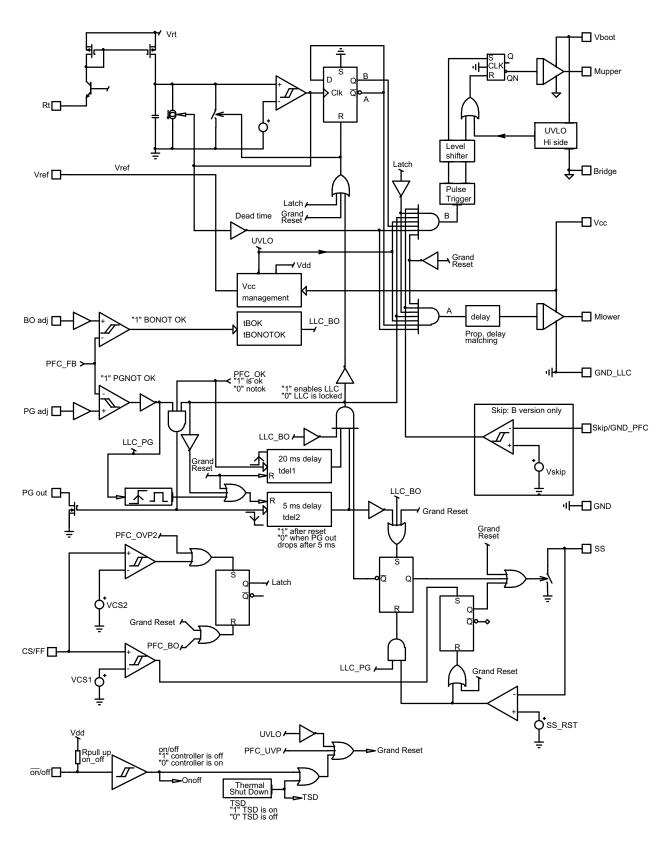

Figure 5. Internal LLC Block Diagram

## MAXIMUM RATINGS

| Symbol                                 | Rating                                                                                        | Value                                                   | Unit |

|----------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------|------|

| V <sub>Bridge</sub>                    | Continuous High Voltage Bridge Pin, Pin 22                                                    | -1 to 600                                               | V    |

| V <sub>BOOT</sub> –V <sub>Bridge</sub> | Floating Supply Voltage, Pin 24–22                                                            | -0.3 to 20                                              | V    |

| V <sub>MU</sub> , V <sub>DRV</sub>     | High Side Output Voltage, Pin 23                                                              | V <sub>BRIDGE</sub> – 0.3 to<br>V <sub>BOOT</sub> + 0.3 | V    |

| V <sub>ML</sub>                        | Low Side Output Voltage, Pin 18, 20                                                           | –0.3 to V <sub>CC</sub> + 0.3                           | V    |

| dV <sub>Bridge</sub> /dt               | Allowable Output Slew Rate on the Bridge Pin, Pin 22                                          | 50                                                      | V/ns |

| V <sub>CC</sub>                        | Power Supply Voltage, Pin 19                                                                  | 20                                                      | V    |

|                                        | Pin Voltage, All Pins (except pin 2, 6, 18–24, GND)                                           | -0.3 to 10                                              | V    |

| $R_{\thetaJA}$                         | Thermal Resistance Junction-to-Air<br>50 mm <sup>2</sup> , 1 oz<br>650 mm <sup>2</sup> , 1 oz | 80<br>65                                                | °C/W |

|                                        | Storage Temperature Range                                                                     | -60 to + 150                                            | °C   |

|                                        | ESD Capability, Human Body Model (All pins except $V_{CC}$ and HV)                            | 2                                                       | kV   |

|                                        | ESD Capability, Machine Model                                                                 | 200                                                     | V    |

| V <sub>CC</sub>                        | Power Supply Voltage, Pin 19                                                                  | 20                                                      | V    |

|                                        | Pin Voltage, All Pins (except pin 2, 6, 18 ~ 24, GND)                                         | –0.3 to 10                                              | V    |

| V <sub>Rt</sub>                        | R <sub>t</sub> Pin Voltage                                                                    | -0.3 to 5                                               | V    |

| V <sub>ref_out</sub>                   | V <sub>ref</sub> Pin Voltage                                                                  | –0.3 to 7                                               | V    |

| I <sub>MAX</sub>                       | Pin Current on Pin 10, 12, and 13                                                             | 0.5                                                     | mA   |

| I <sub>PGout</sub>                     | Pin Current on Pin 3                                                                          | 5                                                       | mA   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. This device(s) contains ESD protection and exceeds the following tests:

Human Body Model 2000 V per JEDEC Standard JESD22-A114E

Machine Model 200 V per JEDEC Standard JESD22-A115-A

2. This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

## **ELECTRICAL CHARACTERISTICS**

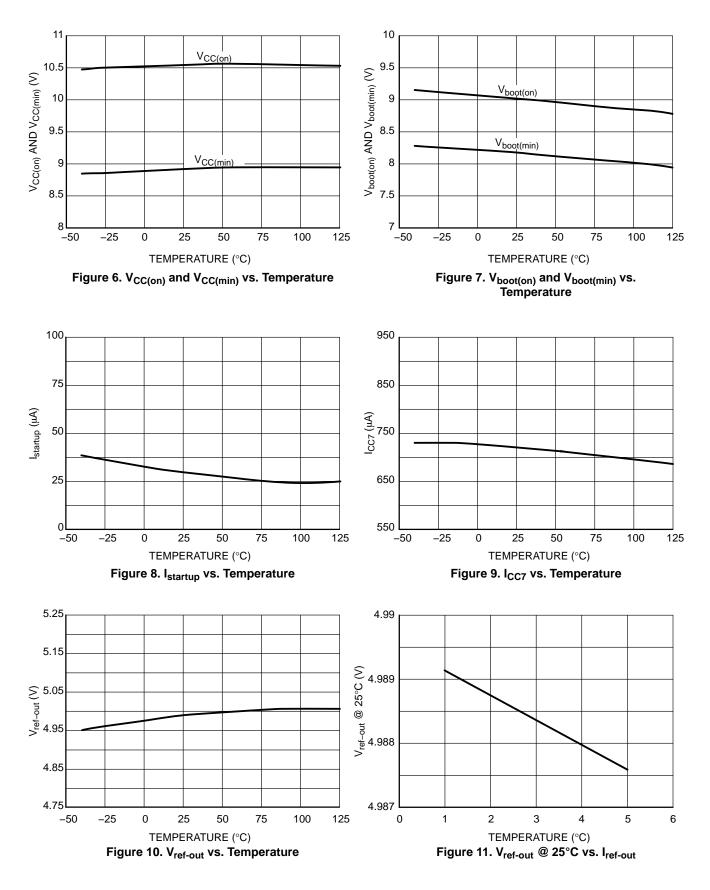

(For typical values  $T_J = 25^{\circ}$ C, for min/max values  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, Max  $T_J = 150^{\circ}$ C,  $V_{CC} = 12$  V unless otherwise noted)

| Symbol Rating | Pin | Min | Тур | Max | Unit |

|---------------|-----|-----|-----|-----|------|

|---------------|-----|-----|-----|-----|------|

## COMMON TO BOTH CONTROLLERS

SUPPLY SECTION

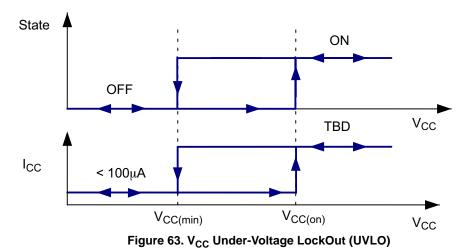

| V <sub>CC(on)</sub>    | Turn-On Threshold Level, V <sub>CC</sub> Going Up                     | 19    | 9.4    | 10.4       | 11.4        | V  |

|------------------------|-----------------------------------------------------------------------|-------|--------|------------|-------------|----|

| V <sub>CC(min)</sub>   | Minimum Operating Voltage after Turn-On                               | 19    | 8      | 9          | 10          | V  |

| V <sub>CC(Hys)</sub>   | Hysteresis between $V_{CC(on)}$ and $V_{CC(min)}$                     | 19    | 1.2    | -          | -           | V  |

| V <sub>Boot(on)</sub>  | Startup Voltage on the Floating Section                               | 24,22 | 7.8    | 8.8        | 9.8         | V  |

| V <sub>Boot(min)</sub> | Cutoff Voltage on the Floating Section                                | 24,22 | 7      | 8          | 9           | V  |

| I <sub>startup</sub>   | Startup Current, V <sub>CC</sub> < V <sub>CC(on)</sub>                | 19    | -      | -          | 100         | μΑ |

| I <sub>CC1</sub>       | PFC Consumption Alone, DRV Pin Unloaded, On/Off Pin Grounded, LLC Off | 19    |        |            |             | mA |

|                        | 65 kHz Version     100 kHz Version                                    |       | -<br>- | 5.1<br>5.3 | 6.4<br>6.54 |    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. In normal operation, when the power supply is un-plugged, the bulk voltage goes down. At a first crossed level, the PG pin opens. Later, when the bulk crosses a second level, the LLC turns off. There is no timing link between these events, except the bulk capacitor discharge slope. However, if for an unknown reason the PFC is disabled (fault, short-circuit), the PG pin immediately opens and if sufficient voltage is still present on the bulk (e.g. in high line condition), the LLC will be disabled after a typical time of 5 ms.

## ELECTRICAL CHARACTERISTICS (continued)

(For typical values  $T_J = 25^{\circ}$ C, for min/max values  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, Max  $T_J = 150^{\circ}$ C,  $V_{CC} = 12$  V unless otherwise noted)

| Symbol | Rating | Pin | Min | Тур | Max | Unit |  |

|--------|--------|-----|-----|-----|-----|------|--|

|--------|--------|-----|-----|-----|-----|------|--|

#### COMMON TO BOTH CONTROLLERS

#### SUPPLY SECTION

| I <sub>CC2</sub> | PFC Consumption Alone, DRV Pin Loaded by 1 nF, On/Off Pin<br>Grounded, LLC Off                                              | 19 |   |     |     | mA |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|----|---|-----|-----|----|

|                  | 65 kHz Version                                                                                                              |    | - | 5.9 | 7.4 |    |

|                  | • 100 kHz Version                                                                                                           |    | - | 6.4 | 7.9 |    |

| I <sub>CC4</sub> | IC Consumption, Both PFC & LLC DRV Pin Unloaded,<br>Rt = 70 k $\Omega$ (LLC F <sub>SW</sub> = 25 kHz)                       | 19 |   |     |     | mA |

|                  | • 65 kHz Version                                                                                                            |    | - | 5.9 | 7.2 |    |

|                  | • 100 kHz Version                                                                                                           |    | - | 6.0 | 7.3 |    |

| $I_{CC5}$        | IC Consumption, Both PFC & LLC DRV Pin Loaded by 1 nF,<br>$R_t = 70 \text{ k}\Omega \text{ (LLC } F_{SW} = 25 \text{ kHz})$ | 19 |   |     |     | mA |

|                  | • 65 kHz Version                                                                                                            |    | _ | 6.9 | 8.6 |    |

|                  | • 100 kHz Version                                                                                                           |    | - | 7.4 | 9.1 |    |

| I <sub>CC6</sub> | IC Consumption in Fault Mode from V <sub>boot</sub><br>(Drivers Disabled, V <sub>boot</sub> > V <sub>boot(min)</sub> )      | 19 | - | 64  | 300 | μΑ |

| I <sub>CC7</sub> | IC Consumption in OFF Mode from $V_{CC}$ ( $\overline{On}$ /Off Pin is Open)                                                | 19 | _ | _   | 950 | μA |

Reference Voltage for External Threshold Setting @  $I_{out} = 5 \text{ mA}$ 4.75 5.25 V V<sub>ref-out</sub> 6 5 Reference Voltage for External Threshold Setting @  $I_{out} = 5 \text{ mA} - T_J = 25^{\circ}C$ V V<sub>ref-out</sub> 6 4.9 5 5.1 Vcc Rejection Capability,  $I_{out} = 5 \text{ mA} - \Delta V_{CC} = 1 \text{ V} - T_J = 25^{\circ}\text{C}$ 0.01 5 V<sub>refLineRea</sub> 6 m٧ Reference Variation with Load Changes, 1 mA <  $I_{ref}$  < 5 mA –  $T_J$  = 25  $^{\circ}\text{C}$ VrefLoadReg 6 1.6 7 m٧ \_ Maximum Output Current Capability 6 5 mΑ I<sub>ref-out</sub> \_ \_

NOTE: Maximum capacitance directly connected to V<sub>REF</sub> pin must be under 100 nF.

DELAY

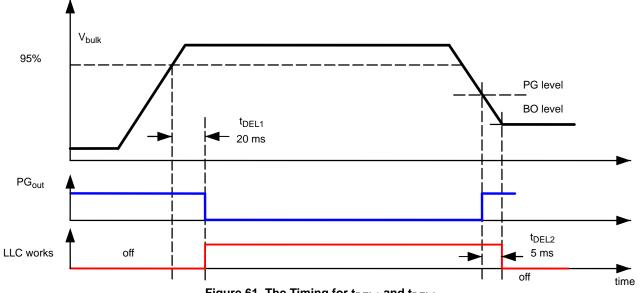

| t <sub>DEL1</sub> | Turn-On LLC Delay after PFC OK Signal is Asserted   | - | 10 | 20 | 30 | ms |

|-------------------|-----------------------------------------------------|---|----|----|----|----|

| t <sub>DEL2</sub> | Turn-Off LLC after Power Good Pin Goes Low (Note 3) | - | 2  | 5  | 8  | ms |

| DROTECTIONS       |                                                     |   |    |    |    |    |

PROTECTIONS

| R <sub>Pull-up</sub> | On/Off Pin Pull-Up Resistor                                  | 4 | -   | 5   | -   | kΩ |

|----------------------|--------------------------------------------------------------|---|-----|-----|-----|----|

| t <sub>on/off</sub>  | Propagation Delay from On to Off (ML & MU are Off) (Note 4)  | 4 | -   | -   | 1   | μs |

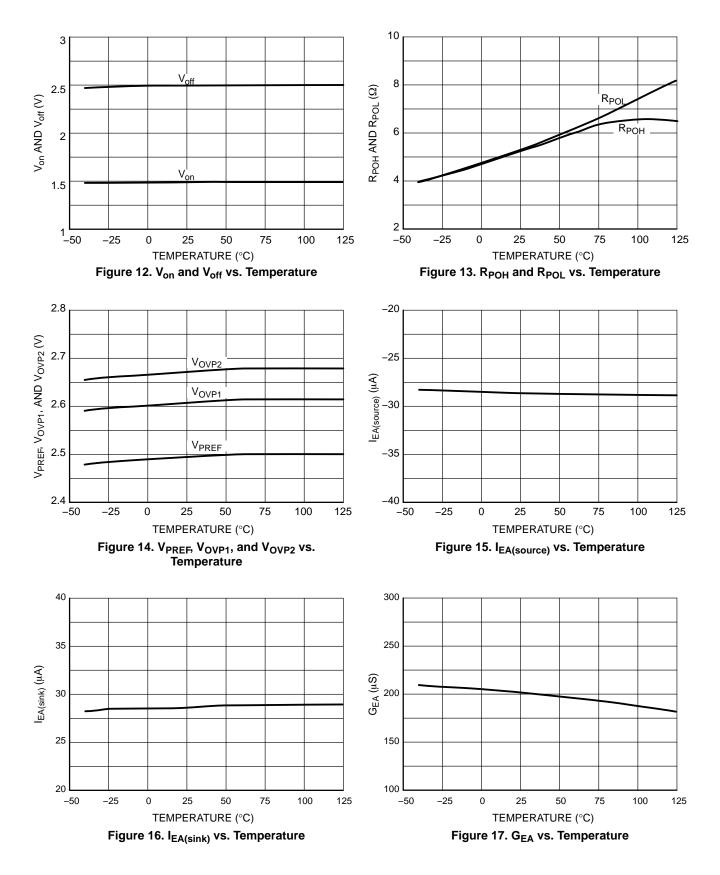

| Von                  | Low Level Input Voltage on On/Off Pin (NCP1910 is Enabled)   | 4 | -   | -   | 1   | V  |

| V <sub>off</sub>     | High Level Input Voltage on On/Off Pin (NCP1910 is Disabled) | 4 | 3   | -   | -   | V  |

| V <sub>op</sub>      | Open Voltage on On/Off Pin                                   | 4 | -   | 7   | -   | V  |

| I <sub>PG</sub>      | Maximum Power Good Pin Sink Current Capability               | 3 | 5   | -   | -   | mA |

| V <sub>PG</sub>      | Power Good Saturation Voltage for I <sub>PG</sub> = 5 mA     | 3 | -   | -   | 350 | mV |

| I <sub>PGadj</sub>   | Input Bias Current, PGadj Pin                                | 7 | -   | 10  | -   | nA |

| V <sub>PGadjH</sub>  | PG Comparator Hysteresis                                     | 7 | -   | 100 | -   | mV |

| TSD                  | Temperature Shutdown (Note 4)                                | - | 140 | -   | -   | °C |

| TSDhyste             | Temperature Hysteresis Shutdown                              | - | _   | 30  | _   | °C |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

In normal operation, when the power supply is un-plugged, the bulk voltage goes down. At a first crossed level, the PG pin opens. Later, when the bulk crosses a second level, the LLC turns off. There is no timing link between these events, except the bulk capacitor discharge slope. However, if for an unknown reason the PFC is disabled (fault, short-circuit), the PG pin immediately opens and if sufficient voltage is still present on the bulk (e.g. in high line condition), the LLC will be disabled after a typical time of 5 ms.

#### ELECTRICAL CHARACTERISTICS (continued)

| Symbol                                                                                      | Rating                                                                                                                                                         | Pin            | Min           | Тур             | Мах           | Unit |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|-----------------|---------------|------|

| POWER FACTO                                                                                 | R CORRECTION                                                                                                                                                   |                |               |                 |               |      |

| GATE DRIVE SE                                                                               | ECTION                                                                                                                                                         |                |               |                 |               |      |

| R <sub>POH</sub>                                                                            | Source Resistance @ I <sub>DRV</sub> = -100 mA                                                                                                                 | 18             | _             | 9               | 20            | Ω    |

| R <sub>POL</sub>                                                                            | Sink Resistance @ I <sub>DRV</sub> = 100 mA                                                                                                                    | 18             | -             | 6.6             | 18            | Ω    |

| t <sub>Pr</sub>                                                                             | Gate Drive Voltage Rise Time from 1.5 V to 10.5 V (C <sub>L</sub> = 1 nF)                                                                                      | 18             | -             | 60              | -             | ns   |

| t <sub>Pf</sub>                                                                             | Gate Drive Voltage Fall Time from 10.5 V to 1.5 V ( $C_L = 1 \text{ nF}$ )                                                                                     | 18             | -             | 40              | -             | ns   |

| REGULATION B                                                                                | LOCK                                                                                                                                                           |                | 1             |                 | 1             |      |

| V <sub>PREF</sub>                                                                           | PFC Voltage Reference                                                                                                                                          | _              | 2.425         | 2.5             | 2.575         | V    |

| I <sub>EA</sub>                                                                             | Error Amplifier Current Capability                                                                                                                             | 10             | _             | ±30             | _             | μA   |

| G <sub>EA</sub>                                                                             | Error Amplifier Gain                                                                                                                                           | _              | 100           | 200             | 300           | μS   |

| Ι <sub>Β</sub>                                                                              | Bias Current @ V <sub>FB</sub> = V <sub>PREF</sub>                                                                                                             | 9              | 0             | -               | 0.3           | μA   |

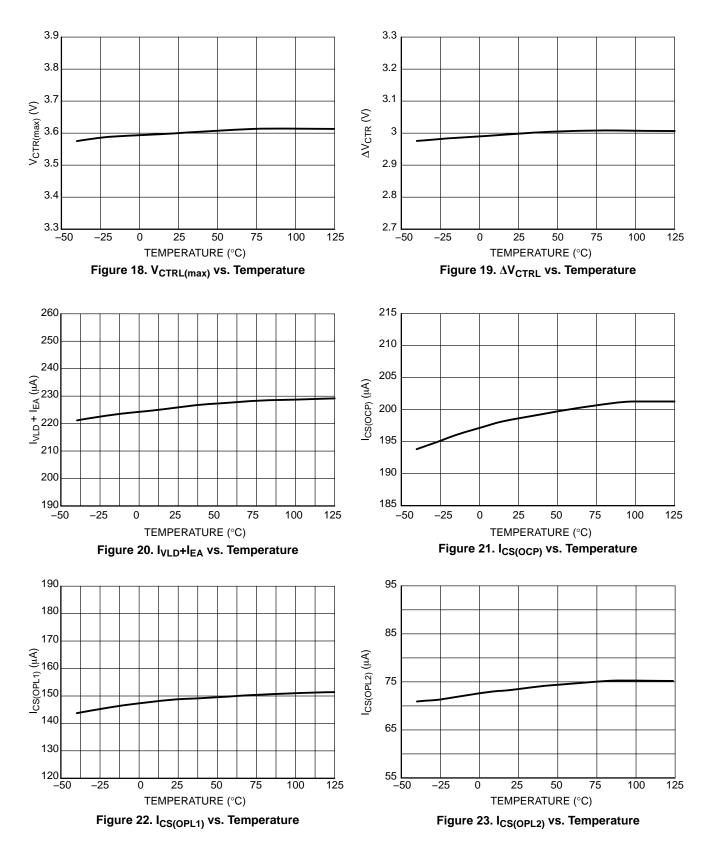

| V <sub>CTRL</sub><br>V <sub>CTRL(max)</sub><br>V <sub>CTRL(min)</sub><br>ΔV <sub>CTRL</sub> | Maximum Control Voltage @ $V_{FB} = 2 V$<br>Minimum Control Voltage @ $V_{FB} = 3 V$<br>$\Delta V_{CTRL} = V_{CTRL(max)} - V_{CTRL(min)}$                      | 10<br>10<br>10 | -<br>-<br>2.7 | 3.6<br>0.6<br>3 | -<br>-<br>3.3 | V    |

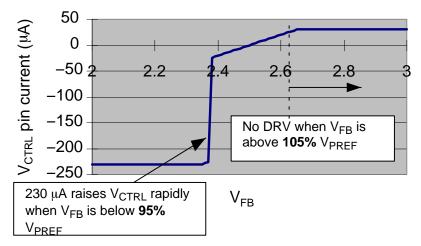

| V <sub>OUT</sub> L / V <sub>PREF</sub>                                                      | Ratio (V <sub>OUT</sub> Low Detect Threshold / V <sub>PREF</sub> ) (Note 4)                                                                                    | _              | 94            | 95              | 96            | %    |

| H <sub>OUT</sub> L / V <sub>PREF</sub>                                                      | Ratio (V <sub>OUT</sub> Low Detect Hysteresis / V <sub>PREF</sub> )                                                                                            | _              | -             | 0.5             | _             | %    |

| $I_{VLD} + I_{EA}$                                                                          | Source Current when (V <sub>OUT</sub> Low Detect) is Activated                                                                                                 | 10             | 190           | 230             | 260           | μA   |

| CURRENT SEN                                                                                 | SE                                                                                                                                                             |                |               |                 |               |      |

| VS                                                                                          | Current Sense Pin Offset Voltage, ( $I_{CS}$ = 100 $\mu$ A)                                                                                                    | 14             | -             | 10              | -             | mV   |

| I <sub>CS(OCP)</sub>                                                                        | Over-Current Protection Threshold                                                                                                                              | 14             | 185           | 200             | 215           | μA   |

| POWER LIMIT                                                                                 |                                                                                                                                                                |                |               |                 |               |      |

| I <sub>CS</sub> x V <sub>LBO</sub>                                                          | Over Power Limitation Threshold                                                                                                                                | _              | 215           | 275             | 335           | μVA  |

| I <sub>CS(OPL1)</sub><br>I <sub>CS(OPL2)</sub>                                              | Over-Power Current Threshold ( $V_{LBO} = 1.8 \text{ V}, V_M = 0 \text{ V}$ )<br>Over-Power Current Threshold ( $V_{LBO} = 3.6 \text{ V}, V_M = 0 \text{ V}$ ) | _              | 119<br>56     | 153<br>75       | 187<br>99     | μΑ   |

| PULSE WIDTH                                                                                 | MODULATION                                                                                                                                                     |                |               |                 |               |      |

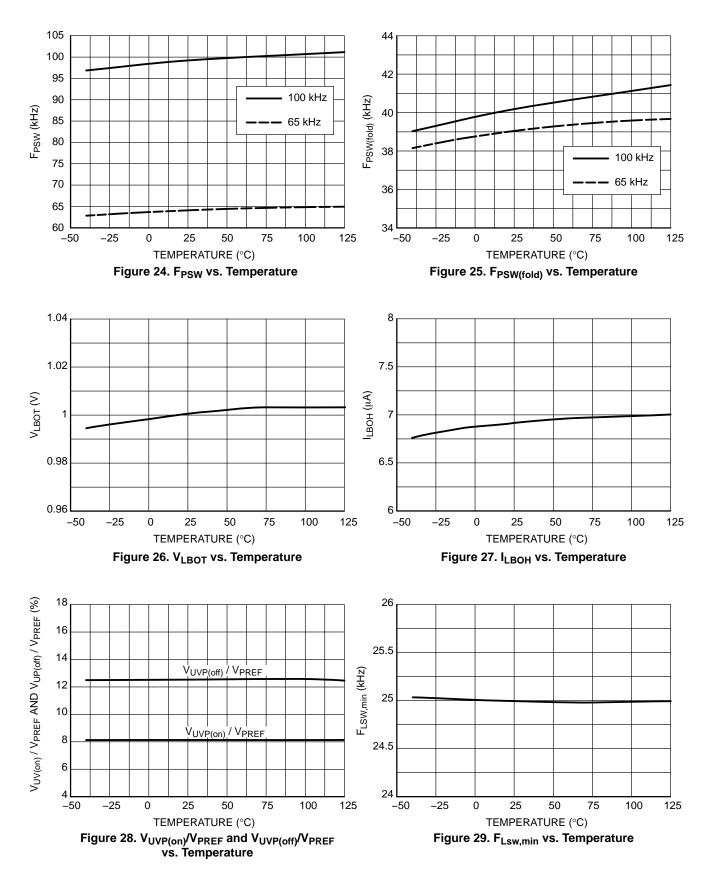

| F <sub>PSW</sub>                                                                            | PFC Switching Frequency<br>• 65 kHz Version<br>• 100 kHz Version                                                                                               | 18             | 58<br>90      | 65<br>100       | 72<br>110     | kHz  |

| F <sub>PSW(fold)</sub>                                                                      | Minimum Switching Frequency<br>(V <sub>fold</sub> = 1.5 V, V <sub>CTRL</sub> = V <sub>CTRL(min)</sub> + 0.1 V)<br>• 65 kHz Version<br>• 100 kHz Version        | 18             | 34<br>33      | 39<br>40        | 43<br>46      | kHz  |

| DC <sub>Pmax</sub>                                                                          | Maximum PFC Duty Cycle                                                                                                                                         | 18             | -             | 97              | -             | %    |

| DC <sub>Pmin</sub>                                                                          | Minimum PFC Duty Cycle                                                                                                                                         | 18             | -             | -               | 0             | %    |

| V <sub>CTRL(fold)</sub>                                                                     | V <sub>CTRL</sub> Pin Voltage to Start Frequency Foldback (V <sub>fold</sub> = 1.5 V)                                                                          | 10             | 1.8           | 2               | 2.2           | V    |

| V <sub>CTRL(foldend)</sub>                                                                  | $V_{CTRL}$ Pin Voltage as Frequency Foldback Reducing to the Minimum (FPSW = FPSW(fold), Vfold = 1.5 V)                                                        | 10             | 1.4           | 1.6             | 1.8           | V    |

| V <sub>fold(max)</sub>                                                                      | Maximum Internal Fold Voltage (Note 4)                                                                                                                         | -              | 1.97          | 2               | 2.03          | V    |

|                                                                                             | DUT DETECTION                                                                                                                                                  |                |               |                 |               |      |

|                                                                                             | Line Brown Out Voltage Threshold                                                                                                                               | 10             | 0.06          |                 | 1.04          | 1    |

| V <sub>LBOT</sub> | Line Brown-Out Voltage Threshold         | 12 | 0.96 | 1.00 | 1.04 | V  |

|-------------------|------------------------------------------|----|------|------|------|----|

| I <sub>LBOH</sub> | Line Brown-Out Hysteresis Current Source | 12 | 6    | 7    | 8    | μΑ |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

In normal operation, when the power supply is un-plugged, the bulk voltage goes down. At a first crossed level, the PG pin opens. Later, when the bulk crosses a second level, the LLC turns off. There is no timing link between these events, except the bulk capacitor discharge slope. However, if for an unknown reason the PFC is disabled (fault, short-circuit), the PG pin immediately opens and if sufficient voltage is still present on the bulk (e.g. in high line condition), the LLC will be disabled after a typical time of 5 ms.

#### ELECTRICAL CHARACTERISTICS (continued)

(For typical values  $T_J = 25^{\circ}$ C, for min/max values  $T_J = -40^{\circ}$ C to +125°C, Max  $T_J = 150^{\circ}$ C,  $V_{CC} = 12$  V unless otherwise noted)

| Symbol                  | Rating                       | Pin | Min | Тур | Max | Unit |

|-------------------------|------------------------------|-----|-----|-----|-----|------|

| POWER FACTO             | R CORRECTION                 |     |     |     |     |      |

| LINE BROWN-C            | UT DETECTION                 |     |     |     |     |      |

| t <sub>LBO(blank)</sub> | Line Brown-Out Blanking Time | -   | 25  | 50  | 75  | ms   |

| LDO(blaint)                |                                                                                                  |    | -   |     | -   | -  |

|----------------------------|--------------------------------------------------------------------------------------------------|----|-----|-----|-----|----|

| t <sub>LBO(window)</sub>   | Line Brown-Out Monitoring Window (Note 4)                                                        | -  | 25  | 50  | 75  | ms |

| V <sub>LBO(clamp)</sub>    | LBO Pin Clamped Voltage if $V_{BO}$ < $V_{LBOT}$ during $t_{LBO(BLANK)}$ (I_{LBO} = 100 $\mu A)$ | 12 | -   | 980 | -   | mV |

| V <sub>LBOH</sub>          | Hysteresis (V <sub>LBOT</sub> – V <sub>LBO(clamp)</sub> ) (Note 4)                               | 12 | 10  | 35  | 60  | mV |

| I <sub>LBO(clamp)</sub>    | Current Capability of LBO                                                                        | 12 | 100 | -   | -   | μΑ |

| V <sub>LBO(PNP)</sub>      | LBO Pin Voltage when Clamped by the PNP Transistor (I $_{LBO}$ = 100 $\mu A)$                    | 12 | 0.4 | 0.7 | 0.9 | V  |

| V <sub>LBO(PD)</sub>       | Pull Down V <sub>LBO</sub> Threshold                                                             | 12 | 1.8 | 2   | 2.2 | V  |

| t <sub>LBO(Pdlimit)</sub>  | Pull Down V <sub>LBO</sub> Time Limitation                                                       | -  | 4.5 | 5   | 6.1 | ms |

| tPFCflag                   | Time Delay to Confirm that $V_{\mbox{CTRL}}$ is the Maximum to Pull Down $V_{\mbox{LBO}}$        | -  | 2.5 | 5   | 7.5 | ms |

| t <sub>LBO</sub> (Pdblank) | Pull Down V <sub>LBO</sub> Blanking Time                                                         | -  | 55  | 77  | 90  | ms |

| CURRENT MOD                | DULATION                                                                                         |    | •   | •   | •   | •  |

| I <sub>M1</sub> | Multiplier Output Current                                                                                                                                                                                                                                     | 11 | 46 | 58 | 72   | μΑ |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|------|----|

| I <sub>M2</sub> | $      (V_{CTRL} = V_{CTRL(max)} - 0.2 \text{ V}, V_{LBO} = 3.6 \text{ V}, I_{CS} = 50  \mu\text{A} ) \\            Multiplier Output Current \\            (V_{CTRL} = V_{CTRL(max)} - 0.2 \text{ V}, V_{LBO} = 1.2 \text{ V}, I_{CS} = 150  \mu\text{A} ) $ | 11 | 15 | 19 | 24.5 |    |

#### **OVER-VOLTAGE PROTECTION**

| V <sub>OVP1</sub>                       | Internal Auto Recovery Over Voltage Threshold                                                     | 9     | 2.536 | 2.615 | 2.694 | V  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------|-------|-------|-------|-------|----|

| V <sub>OVP1H</sub>                      | Hysteresis of Internal Auto Recovery Over Voltage Threshold (Note 4)                              | 9     | -     | 44    | 60    | mV |

| t <sub>OVP1</sub>                       | Propagation Delay ( $V_{FB}$ = 108% $V_{PREF}$ ) to Drive Low                                     | 9, 18 | _     | 500   | -     | ns |

| V <sub>OVP2</sub>                       | External Latched Over Voltage Threshold                                                           | 8     | 2.595 | 2.675 | 2.755 | V  |

| K <sub>OVPH</sub>                       | The Difference between $V_{OVP2}$ and $V_{OVP1}$ over $V_{PREF}$ ((V_{OVP2} - V_{OVP1})/V_{PREF}) | -     | -     | 2     | -     | %  |

| t <sub>DELOVP2</sub>                    | External Latched OVP Integrating Filter Time Constant                                             | -     | -     | 20    | -     | μs |

| I <sub>b,OVP2</sub>                     | Input Bias Current, OVP2                                                                          | 8     | -     | 10    | -     | nA |

| UNDER-VOLTA                             | GE PROTECTION                                                                                     |       |       |       |       |    |

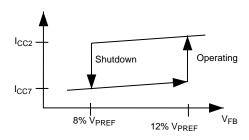

| V <sub>UVP(on)</sub> /V <sub>PREF</sub> | UVP Activate Threshold Ratio                                                                      | 9     | 4     | 8     | 12    | %  |

|                                         |                                                                                                   |       |       |       |       |    |

| V <sub>UVP(off)</sub> /V <sub>PREF</sub> | UVP Deactivate Threshold Ratio                               | 9    | 6 | 12 | 18 | %  |

|------------------------------------------|--------------------------------------------------------------|------|---|----|----|----|

| V <sub>UVP(H)</sub>                      | UVP Lockout Hysteresis                                       | 9    | - | 4  | -  | %  |

| t <sub>UVP</sub>                         | Propagation Delay ( $V_{FB}$ < 8 % $V_{PREF}$ ) to Drive Low | 9–18 | _ | 7  | _  | μs |

| PFC ABNORMA                              | L                                                            |      |   |    |    |    |

| t <sub>PFCabnormal</sub> PFC Abnormal Delay Time<br>(V <sub>CTRL</sub> = V <sub>CTRL(max)</sub> or V <sub>CTRL</sub> = V <sub>CTRL(min)</sub> - 0.1 V) | - | 1 | 1.5 | 2.1 | sec |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-----|-----|-----|

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-----|-----|-----|

## LLC CONTROL SECTION

OSCILLATOR

| F <sub>Lsw,min</sub> | Minimum Switching Frequency, Rt = 70 k $\Omega$ on R <sub>t</sub> Pin | 2 | 24.25 | 25 | 25.75 | kHz |

|----------------------|-----------------------------------------------------------------------|---|-------|----|-------|-----|

|                      | -                                                                     | - |       |    |       |     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

In normal operation, when the power supply is un-plugged, the bulk voltage goes down. At a first crossed level, the PG pin opens. Later, when the bulk crosses a second level, the LLC turns off. There is no timing link between these events, except the bulk capacitor discharge slope. However, if for an unknown reason the PFC is disabled (fault, short-circuit), the PG pin immediately opens and if sufficient voltage is still present on the bulk (e.g. in high line condition), the LLC will be disabled after a typical time of 5 ms.

### ELECTRICAL CHARACTERISTICS (continued)

(For typical values  $T_J = 25^{\circ}$ C, for min/max values  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, Max  $T_J = 150^{\circ}$ C,  $V_{CC} = 12$  V unless otherwise noted)

| Symbol | Rating | Pin | Min | Тур | Max | Unit |

|--------|--------|-----|-----|-----|-----|------|

|--------|--------|-----|-----|-----|-----|------|

### LLC CONTROL SECTION

OSCILLATOR

| OCOLES (I OI)           |                                                                                  |            |      |     |      |     |

|-------------------------|----------------------------------------------------------------------------------|------------|------|-----|------|-----|

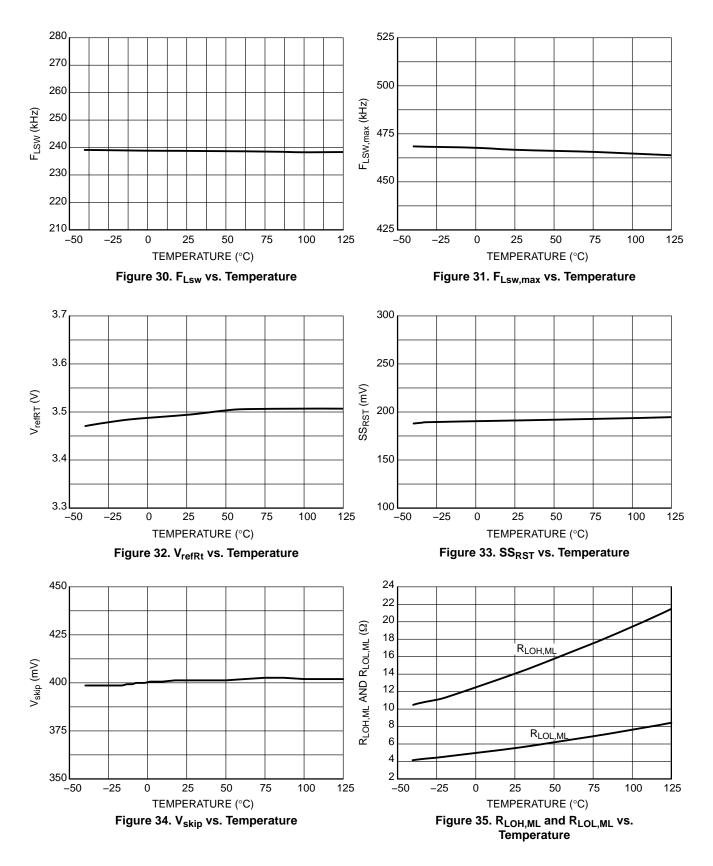

| F <sub>Lsw</sub>        | Switching Frequency, $DT_L = 300$ ns, $Rt = 7 k\Omega$ on $R_t$ Pin              | 2          | 208  | 245 | 282  | kHz |

| F <sub>Lsw,max</sub>    | Maximum Switching Frequency, $DT_L = 300$ ns, $Rt = 3.5$ k $\Omega$ on $R_t$ Pin | 2          | 424  | 500 | 575  | kHz |

| DCL                     | Operating Duty-Cycle Symmetry                                                    | 23, 20     | 48   | 50  | 52   | %   |

| V <sub>refRt</sub>      | Reference Voltage for Oscillator Charging Current Generation                     | 2          | 3.33 | 3.5 | 3.67 | V   |

| R <sub>SS</sub>         | Discharge Switch Resistance                                                      | 1          | -    | 70  | -    | Ω   |

| SS <sub>RST</sub>       | Soft-Start Reset Voltage                                                         | 1          | -    | 200 | -    | mV  |

| V <sub>Skip</sub>       | Skip Cycle Threshold, B Version Only                                             | 16         | 350  | 400 | 450  | mV  |

| V <sub>skip,hyste</sub> | Hysteresis Level on Skip Cycle Comparator, B Version Only                        | 16         | -    | 50  | -    | mV  |

| DRIVE OUTPU             | Т                                                                                |            |      |     |      |     |

| T <sub>Lr</sub>         | Output Voltage Rise-Time @ C <sub>L</sub> = 1 nF, 10–90% of Output Signal        | 23, 20     | _    | 40  | -    | ns  |

| T <sub>Lf</sub>         | Output Voltage Fall-Time @ C <sub>L</sub> = 1 nF, 10–90% of Output Signal        | 23, 20     | _    | 20  | -    | ns  |

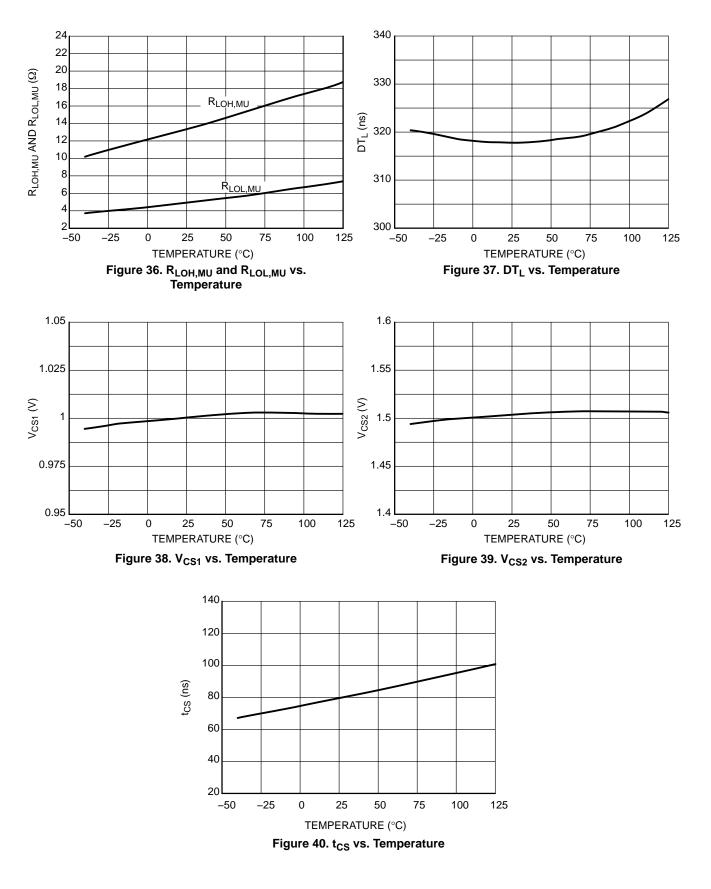

| R <sub>LOH</sub>        | Source Resistance                                                                | 23, 20     | _    | 12  | 26   | Ω   |

| R <sub>LOL</sub>        | Sink Resistance                                                                  | 23, 20     | -    | 5   | 11   | Ω   |

| DTL                     | Dead Time, Measured between 50% of the Rise and Fall Edge                        | 23, 20     | 268  | 327 | 386  | ns  |

| I <sub>HV,leak</sub>    | Leakage Current on High Voltage Pins to GND (600 Vdc)                            | 22, 23, 24 | -    | -   | 5    | μΑ  |

| PROTECTION              | 8                                                                                |            |      |     |      |     |

| I <sub>BOadj</sub>      | Input Bias Current, BOadj Pin                                                    | 5          | -    | 15  | -    | nA  |

| V <sub>BOadjH</sub>     | BO Comparator Hysteresis                                                         | 5          | _    | 100 | -    | mV  |

| t <sub>BOK</sub>        | BO Comparator Integrating Filter Time Constant from High to Low                  | 5          | -    | 150 | -    | μs  |

| t <sub>BONOTOK</sub>    | BO Comparator Integrating Filter Time Constant from Low to High                  | 5          | -    | 20  | -    | μs  |

| V <sub>CS1</sub>        | Current-Sense Pin Level that Resets the Soft-Start Capacitor                     | 15         | 0.95 | 1   | 1.05 | V   |

| V <sub>CS2</sub>        | Current-Sense Pin Level that Permanently Latches Off the Circuit                 | 15         | 1.42 | 1.5 | 1.58 | V   |

|                         |                                                                                  | 1          |      |     |      |     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

15

\_

500

ns

Propagation Delay from VCS1/2 Activation to Respective Action

In normal operation, when the power supply is un-plugged, the bulk voltage goes down. At a first crossed level, the PG pin opens. Later, when the bulk crosses a second level, the LLC turns off. There is no timing link between these events, except the bulk capacitor discharge slope. However, if for an unknown reason the PFC is disabled (fault, short-circuit), the PG pin immediately opens and if sufficient voltage is still present on the bulk (e.g. in high line condition), the LLC will be disabled after a typical time of 5 ms.

4. Guaranteed by design.

t<sub>CS</sub>

## **APPLICATION INFORMATION**

The NCP1910 represents a new generation of control circuit, associating two individual cores performing the functions of Continuous Conduction Mode (CCM) Power Factor Correction (PFC) and LLC resonant control. These cores interact together and implement handshake functions in normal operating conditions but also when a fault appears. Based on the ON Semiconductor proprietary high-voltage technology, the LLC section can drive the high-side MOSFET of the LLC half-bridge without the need of a gate-drive transformer.

## **Power Factor Correction**

- **Compactness and Flexibility**: the NCP1910 requires a minimum of external components to perform a CCM PFC operation. In particular, the circuit scheme simplifies the PFC stage design. In addition, the circuit offers some functions like the line brown-out detection or true power limiting capability that enable the optimization of the PFC design.

- Low Consumption and Shutdown Capability: the NCP1910 is optimized to consume a small current in all operation modes. The consumed current is particularly reduced during the start-up phase and in shutdown mode so that the power losses are minimized when the circuit is disabled. This feature helps meet stringent stand-by low power specifications. Grounding the Feed-back pin can force the circuit to enter standby but the on/off pin can also serve this purpose.

- Maximum Current Limit: the circuit permanently senses the inductor current and immediately turns off the power switch if it is higher than the set current limit. The NCP1910 also prevents any turn on of the power switch as long as the inductor current is not below its maximum permissible level. This feature protects the MOSFET from possible excessive stress that could result from the switching of a current higher than the one the power switch is dimensioned for. In particular, this scheme effectively protects the PFC stage during the start-up phase when large in-rush currents charge the bulk capacitor.

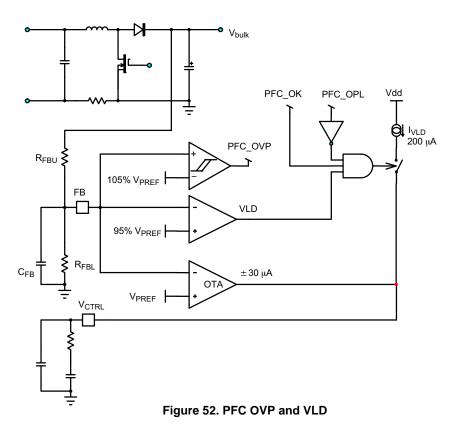

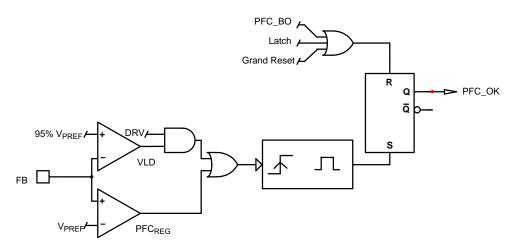

- Under-Voltage Protection for Open Loop Protection: the circuit detects when the feed-back voltage goes below than about 8% of the regulation level. In this case, the circuit turns off and its consumption drops to a very low value. This feature protects the PFC stage from starting operation in case of low ac line conditions or in case of a failure in the feed-back network (i.e. bad connection). In case the UVP circuitry is activated, the Power Good signal is disabled and the LLC circuit stops immediately.

- Fast Transient Response: given the low bandwidth of the regulation block, the output voltage of PFC stages may exhibit excessive over or under-shoots because of

abrupt load or input voltage variations (e.g. at start up). If the bulk voltage is too far from the regulation level:

- **Over-Voltage Protection**: NCP1910 turns off the power switch as soon as V<sub>bulk</sub> exceeds the OVP threshold (105% of the regulation level). This is an auto-recovery function.

- Dynamic Response Enhancer: NCP1910 drastically speeds up the regulation loop by its internal 200 μA current source, activated when the bulk voltage drops below 95% of its regulation level.

- Line Brown-Out Detection: the circuit detects low ac line conditions and disables the PFC stage in this case. This protection mainly protects the power switch from the excessive stress that could damage it in such conditions.

- Over-Power Limitation: the NCP1910 computes the maximum permissible current in dependence of the average input voltage measured by the brown-out block. It is the second OCP with a threshold that is line dependent. When the circuit detects an excessive power transfer, it resets the driver output immediately.

- **Redundant Over-Voltage Protection**: As a redundant safety feature, the NCP1910 offers a second latched OVP whose input is available on OVP2 pin. If the voltage on this pin is above the maximum allowable voltage, the PFC and the LCC are latched off.

- **PFC Abnormal Protection**: When PFC faces an abnormal situation so that the bulk voltage is under regulation longer than the allowable timing, the PFC and LLC are latched off.

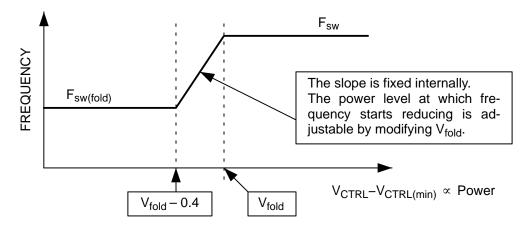

- Frequency Foldback: in light output loading conditions, the user has the ability to program a point on the V<sub>CTRL</sub> pin where the oscillator frequency is gradually reduced. This helps to maintain an adequate efficiency on the PFC power stage alone.

- Soft-Start: to offer a clean start-up sequence and limit both the stress on the power MOSFET and the bulk voltage overshoot, a 30 μA current source charges the compensation network installed on V<sub>CTRL</sub> pin and makes V<sub>CTRL</sub> raise gradually.

- **Output Stage Totem Pole**: the NCP1910 incorporates a ±1.0 A gate driver to efficiently drive TO220 or TO247 power MOSFETs.

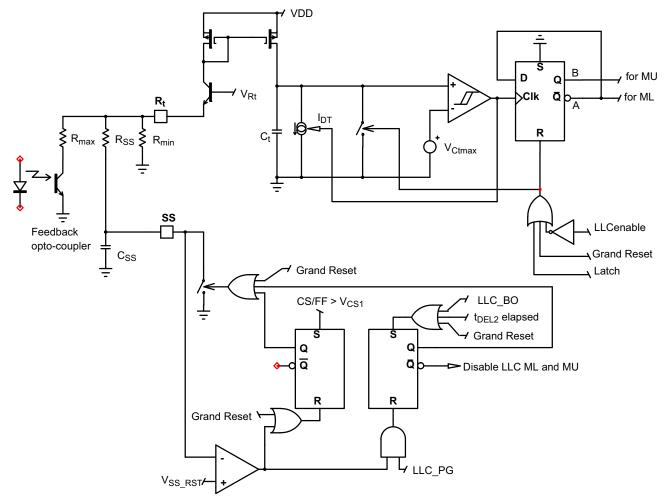

## LLC Controller

• Wide Frequency Operation: the part can operate to a frequency up to 500 kHz by connecting a resistive network from R<sub>t</sub> pin to ground. One resistor sets the maximum switching frequency whereas a second resistor set the minimum frequency.

- **On Board Dead Time**: to eliminate the shoot-through on the half-bridge leg, a dead time is included in the controller (see DT<sub>L</sub> parameter).

- **Soft-Start**: a dedicated pin discharges a capacitor to ground upon start-up to offer a smooth output voltage ramp up. The start-up frequency is the maximum set by the resistor connected between R<sub>t</sub> pin and SS pin. The capacitor connected from R<sub>t</sub> pin to ground fixes the soft start duration. In fault mode, when the voltage on CS/FF pin exceeds a typical value of 1 V, the soft-start pin is immediately discharged and a re-start at high frequency occurs.

- Skip Cycle Operation: to avoid any frequency runaway in light conditions but also to improve the standby power consumption, the NCP1910B welcomes a skip input (Skip pin) which permanently observes the opto-coupler collector. If this pin senses a low voltage, it cuts the LLC output pulses until the collector goes up again. The NCP1910A does not offer the skip capability and routes the analog ground on pin 16 instead.

- High-Soltage Drivers: capitalizing on ON Semiconductor technology, the LLC controller includes a high-voltage section allowing a direct connection to the high-voltage rail. The MOSFET leg can therefore be directly driven without using a gate-drive transformer.

- Fault Protection: as explained in the above lines, the CS/FF pin combines a two-level protection circuit. If the level crosses the first level (1 V), the LLC converter immediately increases its switching frequency to the maximum set by the external resistive divider connected on R<sub>t</sub> pin. This is an auto-recovery protection mode. In case the fault is more severe, the signal on the CS/FF pin crosses the second threshold (1.5 V) and latches off the whole combo controller. Reset occurs via an UVLO detection on V<sub>CC</sub>, a reset on the on/off pin or a brown-out detection on the PFC stage. This latter confirms that the user has unplugged and re-plugged the power supply.

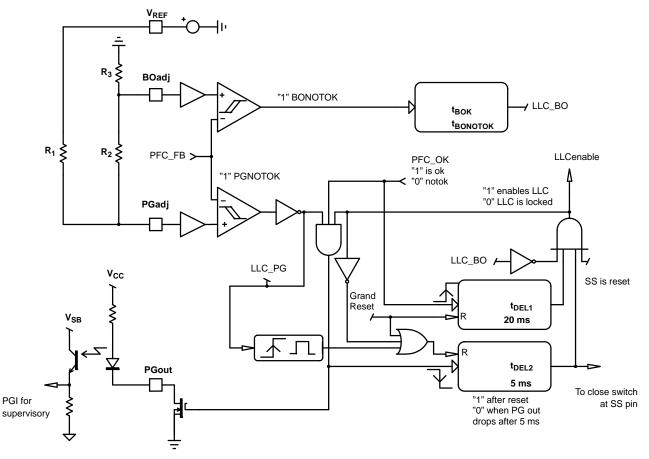

## **Combo Management**

• **Start-Up Delay**: the PFC start-up sequence often generates an output overshoot followed by damped oscillations. To make sure the PFC output voltage is fully stabilized before starting the LLC converter, a 20 ms delay is inserted after the internal PFC\_ok

signal is asserted. This delay is always reset when the combo is started from a  $V_{CC}$  ULVO, line brown-out condition or via the on/off pin.

- Power Good Signal: the power good signal (PG) is intended to instruct the downstream circuitry installed on the isolated secondary side that the combo is working. Once the PFC has started, an internal "PFC OK" signal is asserted. 20 ms later, the PG pin is brought low. This signal can now disappear in two cases: the bulk voltage decreases to an abnormal level, programmed by a reference voltage imposed on PGadi pin. This level is usually above the LLC turn-off voltage, programmed by BOadi pin. Therefore, in a normal turn-off sequence, PG first drops and signals the secondary side that it must be prepared for shutdown. The second event that can drop the PG signal is when the PFC experiences a fault: broken feedback path, severe overload. In this case, the PG signal is immediately asserted high and a 5 ms timer starts. Once this timer is elapsed, the LLC converter can be safely halted.

- Latched Event: in the event of a severe operating condition, the PFC can be latched (OVP2 pin) and/or the LLC controller also (CS/FF pin). In either case, the whole combo controller is locked and can only be reset via a V<sub>CC</sub> UVLO, line brown-out or a level transition on pin on/off.

- Thermal Shutdown: an internal thermal circuitry disables the circuit gate drive and then keeps the power switch off when the junction temperature exceeds 140°C typically. The circuit resumes operation once the temperature drops below about 110°C (30°C hysteresis).

## Principle of NCP1910 Scheme

## **PFC Section**

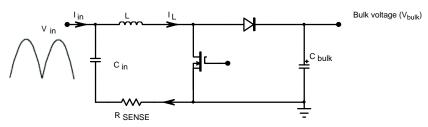

A CCM PFC boost converter is shown in Figure 41. The input voltage is a rectified 50 Hz or 60 Hz sinusoidal signal. The MOSFET is switching at a high frequency (typically 65 kHz in NCP1910) so that the inductor current  $I_L$  basically consists of high and low-frequency components.

Filter capacitor  $C_{in}$  is an essential and very small value capacitor in order to eliminate the high-frequency component of the inductor  $I_L$ . This filter capacitor cannot be too bulky because it can pollute the power factor by distorting the rectified sinusoidal input voltage.

Figure 41. CCM PFC Boost Converter

#### **PFC Methodology**

The NCP1910 uses a proprietary PFC methodology particularly designed for CCM operation. The PFC methodology is described in this section.

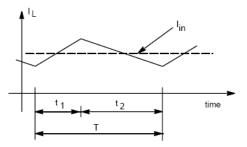

Figure 42. Inductor Current in CCM

As shown in Figure 42, the inductor current  $I_L$  in a switching period T includes a charging phase for duration  $t_1$  and a discharging phase for duration  $t_2$ . The voltage conversion ratio is obtained in Equation 1.

$$\begin{split} & \frac{V_{\text{bulk}}}{V_{\text{in}}} = \frac{t_1 + t_2}{t_2} = \frac{T}{T - t_1} \\ & V_{\text{in}} = \frac{T - t_1}{T} V_{\text{bulk}} \end{split} \tag{eq. 1}$$

Where:

- V<sub>bulk</sub> is the output voltage of PFC stage,

- V<sub>in</sub> is the rectified input voltage,

- T is the switching period,

- t<sub>1</sub> is the MOSFET on time, and

- t<sub>2</sub> is the MOSFET off time.

The input filter capacitor  $C_{in}$  and the front-ended EMI filter absorbs the high-frequency component of inductor current  $I_L$ . It makes the input current  $I_{in}$  a low-frequency signal only of the inductor current.

$$I_{in} = I_{L-50} \qquad (eq. 2)$$

Where:

- I<sub>in</sub> is the input AC current.

- $I_L$  is the inductor current.

- I<sub>L-50</sub> supposes a 50 Hz operation. The suffix 50 means it is with a 50 Hz bandwidth of the original I<sub>L</sub>.

From Equations 1 and 2, the input impedance  $Z_{in}$  is formulated.

$$Z_{in} = \frac{V_{in}}{I_{in}} = \frac{T - t_1}{T} \frac{V_{bulk}}{I_{L-50}}$$

(eq. 3)

where: Z<sub>in</sub> is input impedance.

Power factor is corrected when the input impedance  $Z_{in}$  in Equation 3 is constant or varies slowly in the 50 or 60 Hz bandwidth.

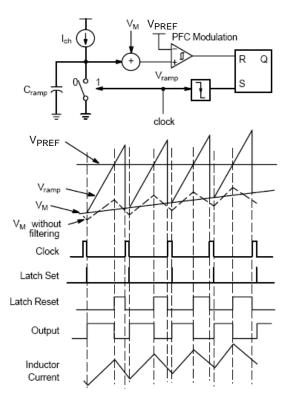

#### Figure 43. PFC Duty Modulation and Timing Diagram

The PFC modulation and timing diagram is shown in Figure 43. The MOSFET on time  $t_1$  is generated by the intersection of reference voltage  $V_{PREF}$  and ramp voltage  $V_{ramp}$ . A relationship in Equation 4 is obtained.

$$V_{ramp} = V_{M} + \frac{I_{ch}t_{1}}{C_{ramp}} = V_{PREF}$$

(eq. 4)

### Where:

- V<sub>ramp</sub> is the internal ramp voltage, the positive input of the PFC modulation comparator,

- V<sub>M</sub> is the multiplier voltage appearing on V<sub>M</sub> pin,

- I<sub>ch</sub> is the internal charging current,

- C<sub>ramp</sub> is the internal ramp capacitor, and

- V<sub>PREF</sub> is the internal reference voltage, the negative input of the PFC modulation comparator.

$I_{ch}$ ,  $C_{ramp}$ , and  $V_{PREF}$  also act as the ramp signal of switching frequency. Hence the charging current  $I_{ch}$  is specially designed as in Equation 5. The multiplier voltage  $V_M$  is therefore expressed in terms of  $t_1$  in Equation 6.

$$I_{ch} = \frac{C_{ramp}V_{PREF}}{T}$$

(eq. 5)

$$V_{M} = V_{PREF} - \frac{t_{1}}{C_{ramp}} \frac{C_{ramp}V_{PREF}}{T} = V_{PREF} \frac{T - t_{1}}{T} (eq. 6)$$

From Equation 3 and Equation 6, the input impedance  $Z_{in}$  is re-formulated in Equation 7.

$$Z_{in} = \frac{V_M}{V_{PREF}} \frac{V_{bulk}}{I_{L-50}}$$

(eq. 7)

Because  $V_{PREF}$  and  $V_{bulk}$  are roughly constant versus time, the multiplier voltage  $V_M$  is designed to be

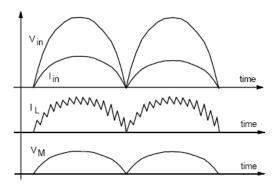

proportional to the  $I_{L-50}$  in order to have a constant  $Z_{in}$  for PFC purpose. It is illustrated in Figure 44.

Figure 44. Multiplier Voltage Timing Diagram

It can be seen in the timing diagram in Figure 43 that  $V_M$  originally consists of a switching frequency ripple coming from the inductor current  $I_L$ . The duty ratio can be inaccurately generated due to this ripple. This modulation is the so-called "peak current mode". Hence, an external capacitor  $C_M$  connected to the multiplier voltage  $V_M$  pin is essential to bypass the high-frequency component of  $V_M$ . The modulation becomes the so-called "average current mode" with a better accuracy for PFC.

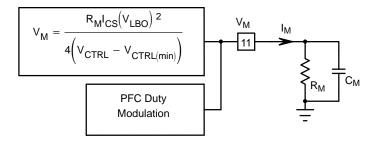

Figure 45. The Multiplier Voltage Pin Configuration

The multiplier voltage  $V_M$  is generated according to Equation 8.

$$V_{M} = \frac{R_{M}I_{CS}(V_{LBO})^{2}}{4(V_{CTRL} - V_{CTRL(min)})}$$

(eq. 8)

Where:

- R<sub>M</sub> is the external multiplier resistor connected to V<sub>M</sub> pin, which is constant.

- V<sub>LBO</sub> is the input voltage signal appearing on the LBO pin, which is proportional to the rms input voltage,

- I<sub>CS</sub> is the sense current proportional to the inductor current I<sub>L</sub> as described in Equation 13.

- V<sub>CTRL</sub> is the control voltage signal, the output voltage of Operational Trans-conductance Amplifier (OTA), as described in Equation 17.

- V<sub>CTRL(min)</sub> is not only the minimum operating voltage of V<sub>CTRL</sub> but also the offset voltage for the PFC current modulation.

$R_M$  directly limits the maximum input power capability. Also, due to the  $V_{in}^2$  feed-forward feature, where the  $V_{LBO}$  is squared, the transfer function and the power delivery is independent from the ac line level. The relationship between  $V_{CTRL}$  and power delivery will be depicted later on.

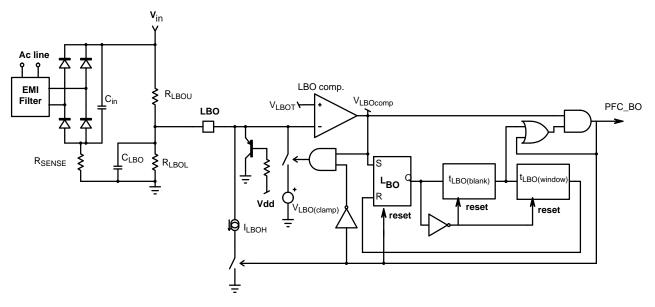

### Line Brown-Out Protection

Figure 46. The Line Brown-Out Configuration

As shown in Figure 46, the Line Brown-Out pin (represented LBO pin) as receives a portion of the input voltage ( $V_{in}$ ). As  $V_{in}$  is a rectified sinusoid, a capacitor must integrate the ac line ripple so that a voltage proportional to the average value of  $V_{in}$  is applied to the brown-out pin.

The main function of the LBO block is to detect too low input voltage conditions. A 7  $\mu$ A current source lowers the LBO pin voltage when a brown-out condition is detected. This is for hysteresis purpose as required by this function.

In nominal operation, the voltage applied to LBO pin must be above the internal reference voltage,  $V_{LBOT}$  (1 V typically). In this case, the output of the LBO comparator  $V_{LBOcomp}$  is low.

Conversely, if  $V_{LBO}$  goes below 1 V,  $V_{LBOcomp}$  turns high and a 980 mV voltage source,  $V_{LBO(clamp)}$ , is connected to the LBO pin to maintain the pin level near 1 V. Then a 50 ms blanking delay,  $t_{LBO(blank)}$ , is activated during which no fault is detected. The main goal of the 50 ms lag is to help meet the hold-up requirements. In case of a short mains interruption, no fault is detected and hence, both PFC and LLC keep operating. In addition, LBO pin being kept at 980 mV, there is almost no extra delay between the line recovery and the occurrence of a proper voltage applied to LBO pin, that otherwise would exist because of the large capacitor typically placed between LBO pin and ground to filter the input voltage ripple. As a result, the NCP1910 effectively "blanks" any mains interruption that is shorter than 25 ms (minimum guaranteed value of the 50 ms timer).

At the end of this blanking delay ( $t_{LBO(blank)}$ ), another timer is activated that sets a 50 ms window during which a fault can be detected. This is the role of the  $t_{LBO(window)}$  in Figure 46:

- If V<sub>LBOcomp</sub> is high during the second 50 ms delay (t<sub>LBO(window)</sub>), a line brown-out condition is confirmed and PFC\_BO signal is asserted high.

- If V<sub>LBOcomp</sub> remains low for the duration of the t<sub>LBO(window)</sub>, no fault is detected.

When the PFC\_BO signal is high:

- The PFC driver is disabled, and the V<sub>CTRL</sub> pin is grounded to recover operation with a soft-start when the fault has gone.

- The V<sub>LBO(clamp)</sub> voltage source is removed from LBO pin.

- The I<sub>LBOH</sub> current source (7 µA typically) is enabled that lowers the LBO pin voltage for hysteresis purpose.

At startup, a pnp transistor ensures that the LBO pin voltage remains below when:  $V_{CC} < UVLO$  or ON/OFF pin is released open or UVP or Thermal Shutdown. This is to guarantee that the circuit starts operation in the right state, which is "PFC\_BO" high. When the NCP1910 is ready to work, the pnp transistor turns off and the circuit enables the I<sub>LBOH</sub>.

Also,  $I_{LBOH}$  is enabled whenever the part is in off mode, but at startup,  $I_{LBOH}$  is disabled until  $V_{CC}$  reaches  $V_{CC(on)}$ .

## Line Brown-Out Network Calculation

If the line brown-out network is connected to the voltage after bridge diode, the monitored voltage can be very different depending on the phase:

• Before operation, the PFC stage is off and the input bridge acts as a peak detector. As a consequence, the input voltage is approximately flat and nearly equates the ac line amplitude:  $\langle V_{in} \rangle = \sqrt{2} V_{ac,rms}$ , where  $V_{ac,rms}$  is the rms voltage of the line. As depicted in previous section, the I<sub>LBOH</sub> turns on before PFC operates for the purpose of adjustable line brown-out hysteresis; hence, the average voltage applied to LBO pin is:

$$V_{LBO} = \sqrt{2} V_{ac,rms} \frac{R_{LBOL}}{R_{LBOU} + R_{LBOL}} - I_{LBOH}$$

$$\cdot \frac{R_{LBOU} \cdot R_{LBOL}}{R_{LBOU} + R_{LBOL}}$$

If R<sub>LBOL</sub> << R<sub>LBOU</sub>,

$$V_{LBO} \simeq \sqrt{2} V_{ac,rms} \frac{R_{LBOL}}{R_{LBOU} + R_{LBOL}} - I_{LBOH} R_{LBOL}^{(eq. 9)}$$

• After the PFC stage has started operation, the input voltage becomes a rectified sinusoid and the average voltage becomes  $\langle V_{in} \rangle = (2/\pi) \sqrt{2} V_{ac,rms}$ , which decays  $2/\pi$  of the peak value of rms input voltage. Hence, the average voltage applied to LBO pin is:  $\langle V_{LBO} \rangle = (2/\pi) \sqrt{2} V_{ac,rms} R_{LBOL}/(R_{LBOU} + R_{LBOL})$ . And because of the ripple on the LBO pin, the minimum value of  $V_{LBO}$  is around:

$$\begin{split} \mathsf{V}_{\mathsf{LBO}} &= \frac{2}{\pi} \sqrt{2} \ \mathsf{V}_{\mathsf{ac,rms}} \frac{\mathsf{R}_{\mathsf{LBOL}}}{\mathsf{R}_{\mathsf{LBOU}} + \mathsf{R}_{\mathsf{LBOL}}} \\ & \times \left( 1 - \frac{f_{\mathsf{LBO}}}{3f_{\mathsf{line}}} \right) \end{split} \tag{eq. 10}$$

Where:

•  $f_{\text{LBO}}$  is the sensing network pole frequency.

$$f_{\text{LBO}} = \frac{\mathsf{R}_{\text{LBOU}} + \mathsf{R}_{\text{LBOL}}}{2\pi\mathsf{R}_{\text{LBOU}}\mathsf{R}_{\text{LBOL}}\mathsf{C}_{\text{LBO}}}$$

- $f_{\text{line}}$  is the line frequency.

- R<sub>LBOL</sub> is low side resistor of the dividing resistors between LBO pin and ground.

- R<sub>LBOU</sub> is upper side resistor of the dividing resistors between V<sub>in</sub> and LBO pin.

The term  $1 - \frac{f_{LBO}}{3f_{line}}$  of Equation 10 enables to take into

account the LBO pin voltage ripple (first approximation).

If as a rule of the thumb, we will assume that  $f_{\text{LBO}} = \frac{f_{\text{line}}}{10}$

Re-arranging the Equation 9 and 10, the network connected to LBO pin can be calculated with the following equations:

$$R_{LBOL} = \left(\frac{1}{1 - \frac{f_{LBO}}{3f_{line}}} \cdot \frac{\pi}{2} \cdot \frac{V_{ac,on}}{V_{ac,off}} - 1\right) \cdot \frac{V_{LBOT}}{I_{LBOH}}$$

(eq. 11)

$$\cong \left(\frac{1}{0.967} \cdot \frac{\pi}{2} \cdot \frac{V_{ac,on}}{V_{ac,off}} - 1\right) \cdot \frac{V_{LBOT}}{I_{LBOH}}$$

$$R_{LBOU} = \left(\frac{\sqrt{2} \cdot V_{ac,on}}{I_{LBOH}R_{LBOL} + V_{LBOT}} - 1\right) R_{LBOL}^{(eq. 12)}$$

Where:

- V<sub>ac,on</sub> is the rms ac voltage to starts PFC operating.

- V<sub>ac,off</sub> the rms ac voltage for line brown-out detection.

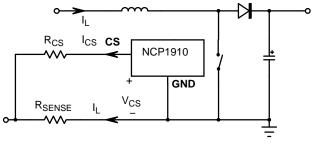

#### **PFC Current Sense**

Figure 47. PFC Current Sensing Configuration

The device senses the inductor current  $I_L$  by the current sense scheme in Figure 47. The device maintains the voltage at CS pin to be zero voltage, i.e.  $V_{CS} = 0$  V, so that

$$I_{CS} = \frac{R_{SENSE}}{R_{CS}}I_{L}$$

(eq. 13)

Where:

- $R_{SENSE}$  is the sense resistor to sense  $I_L$ .

- R<sub>CS</sub> is the offset resistor between CS pin and R<sub>SENSE</sub>.

This scheme has the advantage of the minimum number of components for current sensing. The sense current  $I_{CS}$ represents the inductor current  $I_L$  and will be used in the PFC duty modulation to generate the multiplier voltage  $V_M$ , Over-Power Limitation (OPL), and Over-Current Protection. Equation 13 would insist in the fact that it provides the flexibility in the  $R_{SENSE}$  choice and that it allows to detect in-rush currents.

#### PFC Over-Current Protection (OCP)

PFC Over-current Protection is reached when  $I_{CS}$  is larger than  $I_{S(OCP)}$  (200  $\mu$ A typical). The offset voltage of the CS pin is typical 10 mV and it is neglected in the calculation. Hence, the maximum OCP inductor current threshold  $I_{L(OCP)}$  is obtained in Equation 14.

$$I_{L(OCP)} = \frac{R_{CS}I_{S(OCP)}}{R_{SENSE}} = \frac{R_{CS}}{R_{SENSE}} \times 200 \ \mu\text{A} \text{ (eq. 14)}$$

When over-current protection threshold is reached, the PFC drive goes low. The device automatically resumes operation when the inductor current goes below the threshold.

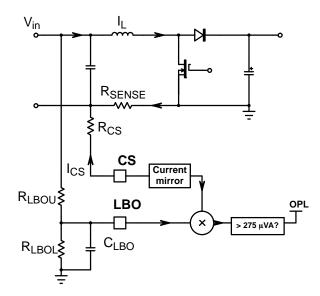

#### PFC Over-Power Limitation (OPL)

This is a second OCP with a threshold that is line dependent. Sense current  $I_{CS}$  represents the inductor current  $I_L$  and hence represents the input current approximately. Input voltage signal  $V_{LBO}$  represents the rms input voltage. The product ( $I_{CS} \times V_{LBO}$ ) represents an approximated input power ( $I_L \times V_{ac}$ ). It is illustrated in Figure 48.

Figure 48. PFC Over-Power Limitation Configuration

When the product  $(I_{CS} \times V_{LBO})$  is greater than a permissible level 275  $\mu$ VA, the device turns off the PFC driver so that the input power is limited. The OPL is automatically deactivated when the product  $(I_{CS} \times V_{LBO})$  is lower than the 275  $\mu$ VA level. This 275  $\mu$ VA level corresponds to the approximated input power  $(I_L \times Vac)$  to be smaller than the particular expression in Equation 15.

$$\begin{split} & \mathsf{I}_{\mathsf{CS}}\mathsf{V}_{\mathsf{LBO}} < 275\ \mu\mathsf{VA} \\ & \left(\mathsf{I}_{\mathsf{L}}\frac{\mathsf{R}_{\mathsf{SENSE}}}{\mathsf{R}_{\mathsf{CS}}}\right) \times \left(\frac{2\sqrt{2}\,\mathsf{K}_{\mathsf{LBO}}}{\pi}\cdot\mathsf{V}_{\mathsf{ac}}\right) < 275\ \mu\mathsf{VA} \end{split} \tag{eq. 15} \\ & \mathsf{I}_{\mathsf{L}}\cdot\mathsf{V}_{\mathsf{ac}} < \frac{\mathsf{R}_{\mathsf{CS}}\cdot\pi}{\mathsf{R}_{\mathsf{SENSE}}\cdot\mathsf{K}_{\mathsf{LBO}}} \cdot 97\ \mu\mathsf{VA} \end{split}$$

Where

$$\mathsf{K}_{\mathsf{LBO}} = \frac{\mathsf{K}_{\mathsf{LBOL}}}{\mathsf{R}_{\mathsf{LBOU}} + \mathsf{R}_{\mathsf{LBOL}}}$$

#### **PFC Reference Section**

The internal reference voltage ( $V_{PREF}$ ) is trimmed to be  $\pm 2\%$  accurate over the temperature range (the typical value is 2.5 V).  $V_{PREF}$  is the reference used for the regulation of PFC section.

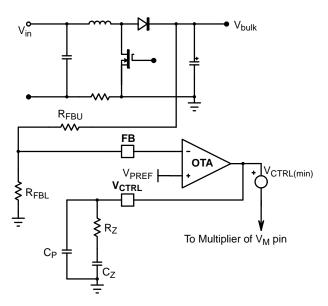

#### PFC Feedback and Compensation

Figure 49. V<sub>CTRL</sub> Type-2 Compensation

The output voltage  $V_{bulk}$  of the PFC circuits is sensed at FB pin via the resistor divider ( $R_{FBL}$  and  $R_{FBU}$ ) as shown in Figure 49.  $V_{bulk}$  is regulated as described in Equation 16.

$$V_{\text{bulk}} = V_{\text{PREF}} \frac{R_{\text{FBU}} + R_{\text{FBL}}}{R_{\text{FBI}}} \qquad (\text{eq. 16})$$

The feedback signal  $V_{FB}$  represents the output voltage  $V_{bulk}$  and will be used in the output voltage regulation, Over-Voltage Protection (OVP), fast transient response, and Under-Voltage Protection (UVP)

The Operational Trans-conductance Amplifier (OTA) constructs a control voltage,  $V_{CTRL}$ , depending on the output power and hence  $V_{bulk}$ . The operating range of  $V_{CTRL}$  is from  $V_{CTRL(min)}$  to  $V_{CTRL(max)}$ . The signal used for PFC duty modulation is after decreasing a offset voltage,  $V_{CTRL(min)}$ , i.e.  $V_{CTRL}$ – $V_{CTRL(min)}$ .

This control voltage  $V_{CTRL}$  is a roughly constant voltage that comes from the PFC output voltage  $V_{bulk}$  that is a slowly varying signal. The bandwidth of  $V_{CTRL}$  can be additionally limited by inserting the external type-2 compensation components (that are  $R_Z$ ,  $C_Z$ , and  $C_P$  as shown in Figure 49). It is recommended to limit cross over frequency of open loop system below 20 Hz typically if the input ac voltage is 50 Hz to achieve power factor correction purpose.

The transformer of  $V_{bulk}$  to  $V_{CTRL}$  is as described in Equation 16 if  $C_Z >> C_P$ .  $G_{EA}$  is the error amplifier gain.

$$\frac{V_{CTRL}}{V_{bulk}} = \frac{R_{FBL} \cdot G_{EA}R_Z}{R_{FBL} + R_{FBU}} \cdot \frac{1 + sR_ZC_Z}{sR_ZC_Z(1 + sR_ZC_P)} \quad (eq. 17)$$

### PFC Power Analysis and Vin<sup>2</sup> Feed-Forward

From Equation 7 through 13, the input impedance  $Z_{in}$  is re-formulated in Equation 18.

$$Z_{in} = \frac{2R_{M}R_{SENSE} \cdot K_{LBO}^{2} \cdot V_{ac}^{2} \cdot V_{bulk}I_{L}}{\pi^{2}R_{CS} \cdot \left(V_{CTRL} - V_{CTRL(min)}\right) \cdot V_{PREF}I_{L-50}}_{(eq. 18)}$$

When  $I_L$  is equal to  $I_{L-50}$ , Equation 18 is re-formulated in Equation 19.

$$Z_{in} = \frac{2R_{M}R_{SENSE} \cdot K_{LBO}^{2} \cdot V_{ac}^{2} \cdot V_{bulk}}{\pi^{2}R_{CS} \cdot \left(V_{CTRL} - V_{CTRL(min)}\right) \cdot V_{PREF}} \quad (eq. 19)$$

The multiplier capacitor  $C_M$  is the one to filter the high-frequency component of the multiplier voltage  $V_M$ . The high-frequency component is basically coming from the inductor current I<sub>L</sub>. On the other hand, the input filter capacitor  $C_{in}$  similarly removes the high-frequency component of inductor current I<sub>L</sub>. If the capacitors  $C_M$  and  $C_{in}$  match with each other in terms of filtering capability, I<sub>L</sub> becomes I<sub>L-50</sub>. Input impedance Z<sub>in</sub> is roughly constant over the bandwidth of 50 or 60 Hz and power factor is corrected.

Input and output power ( $P_{in}$  and  $P_{out}$ ) are derived in Equations 20 and 21 when the circuit efficiency  $\eta$  is obtained or assumed. The variable  $V_{ac}$  stands for the rms input voltage.

Because of the  $V_{in}^2$  feed-forward, the power delivery is independent from input voltage. Hence the transfer function of power stage is independent from input voltage, which easies the compensation loop design.

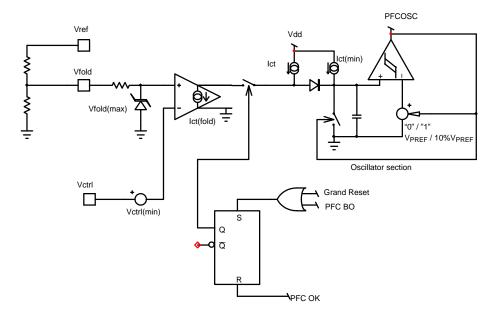

### PFC Frequency Foldback

NCP1910 implements frequency foldback feature on PFC section to improve the efficiency at light load. Thanks to  $V_{in}^2$  feed-forward feature, the output power is proportional to the ( $V_{CTRL} - V_{CTRL(min)}$ ). The PFC frequency foldback is hence done by comparing ( $V_{CTRL} - V_{CTRL(min)}$ ) with  $V_{fold}$ , the voltage on Fold pin.

The simplified block diagram of PFC frequency foldback feature is depicted in Figure 50.

Figure 50. The PFC Frequency Foldback Block

## Where:

- I<sub>Ct(min)</sub> limits the minimum operating frequency.

- I<sub>Ct</sub> and I<sub>Ct(min)</sub> provide the charging current for oscillator and hence control the nominal operating frequency.

- V<sub>fold</sub> determines the power level at which the frequency foldback starts.

- I<sub>Ct(fold)</sub> steals the I<sub>Ct</sub> and hence reduces the operating frequency according to the error information between V<sub>fold</sub> and (V<sub>CTRL</sub> − V<sub>CTRL</sub>(min)).

- The transient slope of frequency foldback vs. V<sub>CTRL</sub> is fixed inside.

V<sub>fold(max)</sub> is to limit the maximum power level of frequency foldback, which is around 2 V typically.

The frequency foldback is disabled at start-up, i.e. before the PFCok signal in Figure 50 is asserted high.

The user can adjust the power level at which the frequency foldback starts by adjust the resistor divider between  $V_{REF}$  pin and fold pin. Also, the frequency foldback can be disabled by grounding fold pin.

The relationship between operating frequency and  $V_{\text{CTRL}}$  is depicted in Figure 51.

Figure 51. The Relationship between Frequency and V<sub>CTRL</sub>

## **PFC Power Boost**