# Single-Wire, I/O Powered Serial EEPROM with a Unique, Factory Programmed 64-bit Serial Number 1-Kbit (128 x 8)

#### PRELIMINARY DATASHEET

#### **Features**

- Low voltage operation

- Device is self-powered via 1.7V to 3.6V pull-up voltage on the SI/O line

- Internally organized as 128 words of 8 bits each (1-Kbit)

- Single-Wire serial interface with I<sup>2</sup>C protocol structure

- Device communication is achieved through a single I/O pin

- Standard Speed and High Speed Mode options

- 15.4kbps in Standard Speed Mode and 125kbps in High Speed Mode

- 8-byte Page Write or single Byte Writes allowed

- Discovery Response feature for quick detection of devices on the bus

- ROM Zone support

- Device is segmented into four 256-bit zones, each of which can be permanently made read-only (ROM)

- Extended EEPROM region (256 bits in length)

- Lower 8 bytes contains a factory programmed, read-only, 64-bit Serial Number that is unique to all Atmel Single-Wire products

- Upper 16 bytes are user-programmable and permanently lockable

- Self-timed write cycle (5ms max)

- Manufacturer Identification support

- Device responds with unique value for Atmel as well as density and revision information

- High reliability

- Endurance: 1,000,000 write cycles

- Data retention: 100 years

- IEC 61000-4-2 Level 4 ESD Compliant (±8kV Contact, ±15kV Air Discharge)

- Green (Lead-free/Halide-free/RoHS Compliant) package options

- 8-lead SOIC, 3-lead SOT23, and 4-ball WLCSP

- Die sale options in wafer form and tape and reel

#### **Description**

The Atmel® AT21CS01 provides 1,024 bits of Serial Electrically Erasable and Programmable Read-Only Memory (EEPROM) organized as 128 words of eight bits each. The device's software addressing scheme allows up to eight devices to share a common Single-Wire bus. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. Some applications examples include analog sensor calibration and storage data, ink and toner print cartridge identification, and management of after-market consumables. The device is available in space-saving package options and operates with an external pull-up voltage from 1.7V to 3.6V on the SI/O line.

# 1. Table of Contents

| 1. | Table of Contents 2 |                                                             |     |  |  |  |  |

|----|---------------------|-------------------------------------------------------------|-----|--|--|--|--|

| 2. | Pin D               | Descriptions and Pinouts                                    | 4   |  |  |  |  |

| 3. | Devi                | ce Block Diagram                                            | 5   |  |  |  |  |

| 4. | Devi                | ce Operation and Communication                              | 6   |  |  |  |  |

|    | 4.1                 | Single Wire Bus Transactions                                | 6   |  |  |  |  |

|    |                     | 4.1.1 Device Reset / Power-up and Discovery Response        | . 6 |  |  |  |  |

|    |                     | 4.1.1.1 Resetting The Device                                | . 6 |  |  |  |  |

|    |                     | 4.1.1.2 Device Response Upon Reset or Power-Up              | . 7 |  |  |  |  |

|    |                     | 4.1.2 Data Input and Output Bit Frames                      |     |  |  |  |  |

|    |                     | 4.1.2.1 Data Input Bit Frames                               | . 8 |  |  |  |  |

|    |                     | 4.1.2.2 Start / Stop Condition                              | . 9 |  |  |  |  |

|    |                     | 4.1.2.3 Communication Interruptions                         | . 9 |  |  |  |  |

|    |                     | 4.1.2.4 Data Output Bit Frame                               | 10  |  |  |  |  |

| 5. | Devi                | ce Addressing and I <sup>2</sup> C Protocol Emulation       | 11  |  |  |  |  |

|    | 5.1                 | Memory Organization                                         | 11  |  |  |  |  |

| 6. | Δναί                | lable Opendes                                               | 42  |  |  |  |  |

| О. | 6.1                 | lable Opcodes                                               |     |  |  |  |  |

|    | 6.2                 | Main EEPROM Access (Opcode Ah)                              |     |  |  |  |  |

|    | 6.3                 | Lock Extended EEPROM (Opcode 2h)                            |     |  |  |  |  |

|    | 6.4                 | ROM Zone Register Access (Opcode 7h)                        |     |  |  |  |  |

|    | 6.5                 | Freeze ROM Zone State (Opcode 1h)                           |     |  |  |  |  |

|    | 6.6                 | Manufacturer ID Read (Opcode Ch)                            |     |  |  |  |  |

|    | 6.7                 | Standard Speed Mode (Opcode Ch)                             |     |  |  |  |  |

|    | 6.8                 | High Speed Mode (Opcode Eh)                                 |     |  |  |  |  |

| _  |                     |                                                             |     |  |  |  |  |

| 7. |                     | e Operations                                                |     |  |  |  |  |

|    | 7.1                 | Byte Write                                                  |     |  |  |  |  |

|    | 7.2                 | Page Write                                                  |     |  |  |  |  |

|    | 7.3                 | Writing to the Extended EEPROM                              |     |  |  |  |  |

|    | 7.4                 | Locking the Extended EEPROM                                 |     |  |  |  |  |

|    |                     | 7.4.1 Device Response to a Write Command on a Locked Device |     |  |  |  |  |

|    |                     | 7.4.2 Check Lock Command                                    |     |  |  |  |  |

|    | 7.5                 | Setting the Device Speed.                                   |     |  |  |  |  |

|    |                     | 7.5.1 Standard Speed Mode                                   |     |  |  |  |  |

|    |                     | 7.5.2 High Speed Mode                                       | 17  |  |  |  |  |

| 8. | Read                |                                                             | 18  |  |  |  |  |

|    | 8.1                 | Current Address Read within the Main EEPROM                 | 18  |  |  |  |  |

|    | 8.2                 | Random Read within the Main EEPROM                          | 19  |  |  |  |  |

|    | 8.3                 | Sequential Read within the Main EEPROM                      | 19  |  |  |  |  |

|    | 8.4                 | Read Operations in the Extended EEPROM Region               | 20  |  |  |  |  |

|    |                     | 8.4.1 Serial Number Read                                    |     |  |  |  |  |

|    | 8.5                 | Manufacturer ID Read                                        | 21  |  |  |  |  |

| 9.  | ROM   | Zones                                                         | 22 |

|-----|-------|---------------------------------------------------------------|----|

|     | 9.1   | ROM Zone Size and ROM Zone Registers                          | 22 |

|     |       | 9.1.1 ROM Zone Registers                                      |    |

|     | 9.2   | Programming and Reading the ROM Zone Registers                | 22 |

|     |       | 9.2.1 Reading the status of a ROM Zone Register               | 22 |

|     |       | 9.2.2 Writing to a ROM Zone Register                          | 23 |

|     |       | 9.2.3 Freeze ROM Zone Registers                               | 24 |

|     | 9.3   | Device Response to a Write Command Within an Enabled ROM Zone | 24 |

| 10. | Elect | rical Specifications                                          | 25 |

|     | 10.1  | Absolute Maximum Ratings                                      | 25 |

|     | 10.2  | DC and AC Operating Range                                     | 25 |

|     | 10.3  | DC Characteristics                                            | 25 |

|     | 10.4  | AC Characteristics                                            | 26 |

|     |       | 10.4.1 Reset and Discovery Response Timing                    | 26 |

|     |       | 10.4.2 Data Communication Timing                              | 26 |

|     | 10.5  | EEPROM Cell Performance Characteristics                       | 27 |

|     | 10.6  | Device Default Condition from Atmel                           | 27 |

| 11. | Orde  | ring Code Detail                                              | 28 |

| 12. | Orde  | ring Information                                              | 29 |

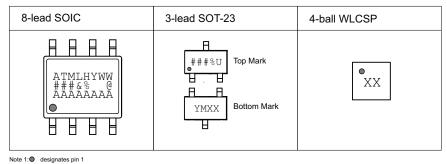

| 13. | Part  | Markings                                                      | 30 |

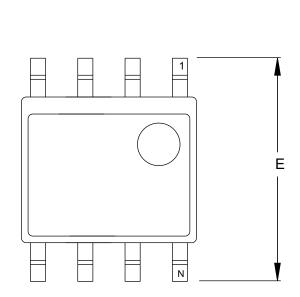

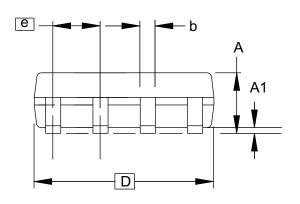

| 14. | Pack  | aging Information                                             | 31 |

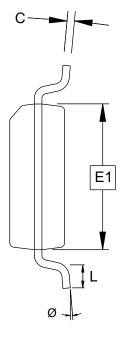

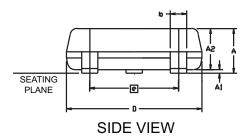

|     | 14.1  | 8S1 — 8-lead SOIC                                             |    |

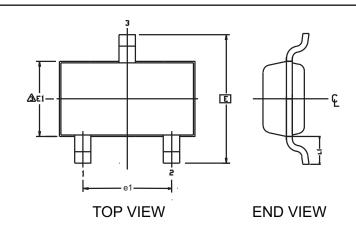

|     | 14.2  | 3ST1 — 3-lead SOT23                                           |    |

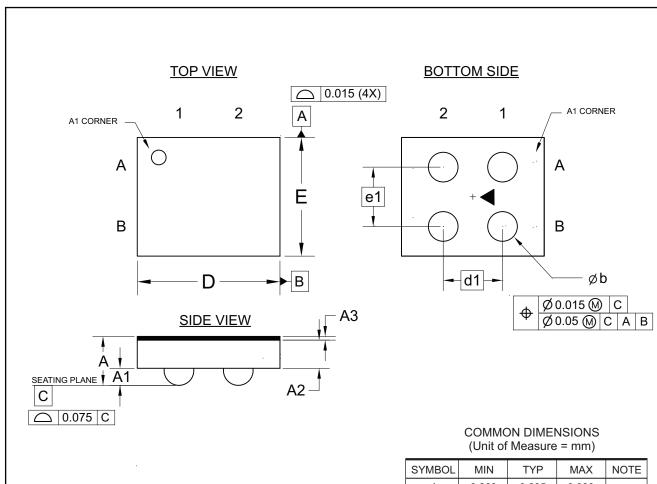

|     | 14.3  | 4U-6 — 4-ball WLCSP                                           |    |

| 15. | Revis | sion History                                                  | 34 |

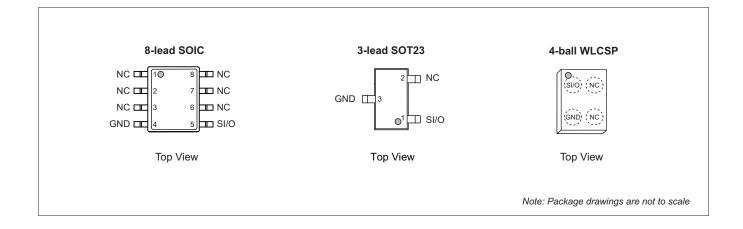

# 2. Pin Descriptions and Pinouts

Table 2-1. Pin Descriptions

| Pin<br>Symbol | Pin Name and Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Asserted<br>State | Pin<br>Type                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------|

| NC            | <b>No Connect:</b> The NC pins are not internally connected. These pins can be connected to GND or left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                 | _                          |

| GND           | <b>Ground:</b> The ground reference for the power supply. GND should be connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                 | Power                      |

| SI/O          | Serial Input & Output: The SI/O pin is an open-drain, bi-directional input/output pin used to serially transfer data to and from the device. The SI/O pin must be pulled-high using an external pull-up resistor (not to exceed $4K\Omega$ in value) and may be wire-ORed with any number of other open-drain or open-collector pins from other devices on the same bus. The device also uses the SI/O pin as its voltage source by drawing and storing power during the periods that the pin is pulled high to a voltage level between 1.7V and 3.6V. | _                 | Power,<br>Input/<br>Output |

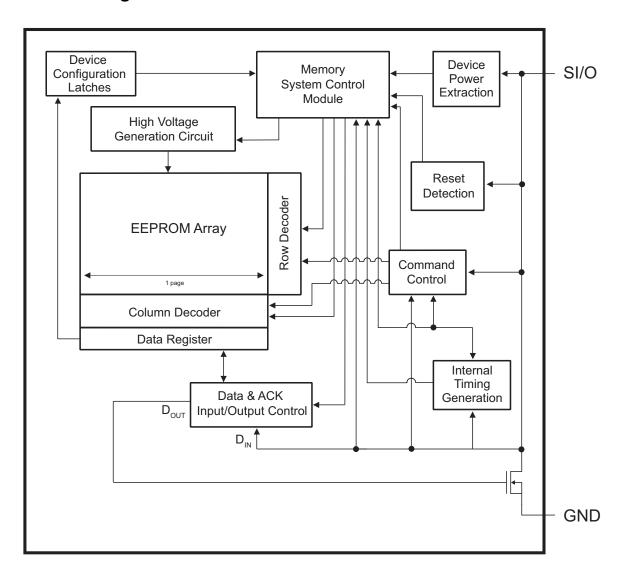

# 3. Device Block Diagram

# 4. Device Operation and Communication

The AT21CS01 operates as a Slave device and utilizes a single wire digital serial interface to communicate with a host controller, commonly referred to as the Bus Master. The Master controls all Read and Write operations to the Slave devices on the serial bus. The device has two speeds of operation, Standard Speed Mode and High Speed Mode.

The device utilizes an 8-bit data structure. Data is transferred to and from the device via a single-wire serial interface using the Serial Input/Output (SI/O) pin. Power to the device is also provided via the SI/O pin, thus, only the SI/O pin and the GND pin are required for device operation. Data sent to the device over the Single-Wire bus is interpreted by the state of the SI/O pin during specific time intervals or slots. Each time slot is referred to as a Bit Frame and lasts  $t_{BIT}$  in duration. The Master initiates all Bit Frames by driving the SI/O line low. All commands and data information are transferred with the Most-Significant Bit (MSB) first.

The software sequence sent to the device is an emulation of what would be sent to an I<sup>2</sup>C Serial EEPROM with the exception that typical 4-bit device address of '1010' is replaced by a 4-bit opcode. The device has been architected in this way to allow for rapid deployment and significant reuse of existing I<sup>2</sup>C firmware. Please refer to Section 5., "Device Addressing and I<sup>2</sup>C Protocol Emulation" for more details about the way the device operates.

During bus communication, one data bit is transmitted in every Bit Frame, and after eight bits (one byte) of data has been transferred, the receiving device must respond with either an acknowledge (ACK) or a no-acknowledge (NACK) response bit during a ninth bit window. There are no unused clock cycles during any Read or Write operation, so there must not be any interruptions or breaks in the data stream during each data byte transfer and ACK or NACK clock cycle.

#### 4.1 Single Wire Bus Transactions

Data transmitted over the SI/O line can be one of five possible types:

- Reset and Discovery Response

- Logic 0 or Acknowledge (ACK)

- Logic 1 or No Acknowledge (NACK)

- Start Condition

- Stop Condition

The Reset and Discovery Response is not considered to be part of the data stream to the device, whereas the remaining four transactions are all required in order to send data to and receive data from the device. The difference between the different types of data stream transactions is the duration that SI/O is driven low within the Bit Frame.

#### 4.1.1 Device Reset / Power-up and Discovery Response

#### 4.1.1.1 Resetting The Device

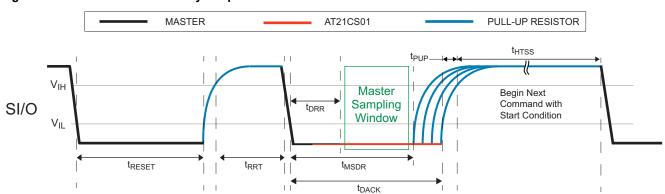

A Reset and Discovery Response sequence is used by the Master to reset the device as well as to perform a general bus call to determine if any devices are present on the bus.

To begin the Reset portion of the sequence, the Master must drive SI/O low for a minimum time of  $t_{RESET}$ . The length of  $t_{RESET}$  differs for Standard Speed Mode and for High Speed Mode. The duration of  $t_{RESET}$  is the longest low level the part can receive. Reset is used to force any internal charge storage within the device to be consumed, causing the device to lose all remaining standby power available internally.

Upon SI/O being released for a sufficient amount of time to allow the device time to power up and initialize, the Master must then always request a Discovery Response Acknowledge from the AT21CS01 prior to any commands being sent to the device. The Master can then determine if an AT21CS01 is present by sampling for the Discovery Response Acknowledge from the device.

#### 4.1.1.2 Device Response Upon Reset or Power-Up

After the device has been powered up or after the Master has reset the device by holding the SI/O line low for  $t_{RESET}$ , the Master must then release the line which will be pulled high by an external pull-up resistor. The Master must then wait an additional minimum time of  $t_{RRT}$  before the Master can request a Discovery Response Acknowledge from the device.

The Discovery Response Acknowledge sequence begins by the Master driving the SI/O line low which will start the AT21CS01's internal timing circuits. The Master must continue to drive the line low for t<sub>DRR</sub>.

During the  $t_{DRR}$  time, the AT21CS01 will respond by concurrently driving SI/O low. The device will continue to drive the low for a total time of  $t_{DACK}$ . The Master should sample the state of the SI/O line at  $t_{MSDR}$  past the initiation of  $t_{DRR}$ . By definition, the  $t_{DACK}$  minimum is longer than the  $t_{MSDR}$  maximum time, thereby ensuring the Master can always correctly sample the SI/O for a level less than  $V_{IL}$ . After the  $t_{DACK}$  time has elapsed, the AT21CS01 will release SI/O which will then be pulled high by the external pull-up resistor.

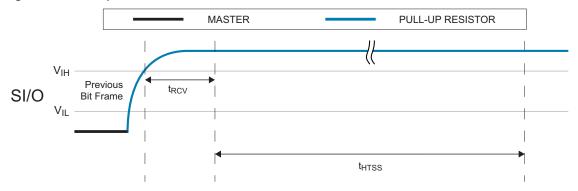

The Master must then wait  $t_{HTSS}$  before continuing which creates a Start condition for the device (see Section 4.1.2.2 for more details about Start conditions). After waiting at least  $t_{HTSS}$  after SI/O has been pulled above  $V_{IH}$ , the device is ready to accept data transactions on the bus. By default, the device will come out of reset in High Speed Mode. Changing the device to Standard Speed Mode is covered in Section 6.7 on page 13. The AT21CS01 will power up with its internal address pointer set to zero.

The timing requirements for the Reset and Discovery Response sequence for both Standard Speed and High Speed Mode can be found in Section 10.4, "AC Characteristics" on page 26.

Figure 4-1. Reset and Discovery Response Waveform

#### 4.1.2 Data Input and Output Bit Frames

Communication with the AT21CS01 is conducted in time intervals referred to as a Bit Frame and last  $t_{BIT}$  in duration. Each Bit Frame contains a single binary data value. Input Bit Frames are used to transmit data from the Master to the AT21CS01 and can either be a Logic 0 or a Logic 1. An output Bit Frame carries data from the AT21CS01 to the Master. In all input and output cases, the Master initiates the Bit Frame by driving the SI/O line low. Once the AT21CS01 detects the SI/O being driven below the  $V_{IL}$  level, its internal timing circuits begin to run.

The duration of each Bit Frame is allowed to vary from bit to bit as long as the variation does not cause the  $t_{BIT}$  length to exceed the specified minimum and maximum values (see Section 10.4 on page 26). The  $t_{BIT}$  requirements will vary depending on whether the device is set for Low Speed or High Speed Mode. For more information about setting the speed of the device, please refer to Section 7.5, "Setting the Device Speed" on page 17.

#### 4.1.2.1 Data Input Bit Frames

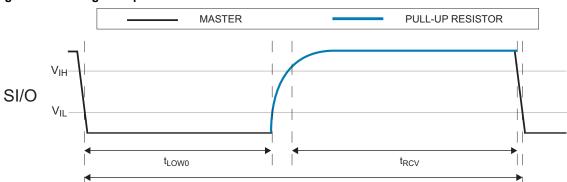

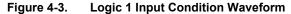

A data input Bit Frame can be used by the Master to transmit either a Logic 0 or Logic 1 data bit to the AT21CS01. The input Bit Frame is initiated when the Master drives the SI/O line low. The length of time that the SI/O line is held low will dictate whether the Master is transmitting a Logic 0 or a Logic 1 for that Bit Frame. For a Logic 0 input, the length of time that the SI/O line must be held low is defined as  $t_{LOW0}$ . Similarly, for a Logic 1 input, the length of time that the SI/O line must be held low is defined as  $t_{LOW1}$ .

The AT21CS01 will sample the state of the SI/O line after the maximum  $t_{LOW1}$  but prior to the minimum  $t_{LOW0}$  after SI/O was driven below the  $V_{IL}$  threshold to determine if the data input is a Logic 0 or a Logic 1. If the Master is still driving the line low at the sample time, the AT21CS01 will decode that Bit Frame as a Logic 0 as SI/O will be at a voltage less than  $V_{IL}$ . If the Master has already released the SI/O line, the AT21CS01 will see a voltage level greater than or equal to  $V_{IH}$  because of the external pull-up resistor, and that Bit Frame will be decoded as a Logic 1. The timing requirements for these parameters can be found in Section 10.4, "AC Characteristics" on page 26.

A Logic 0 condition has multiple uses in the I<sup>2</sup>C emulation sequences. It is used to signify a '0' data bit, and it also is used for an Acknowledge (ACK) response. Additionally, a Logic 1 condition is also is used for a No Acknowledge (NACK) response in addition to the nominal '1' data bit.

Below, Figure 4-2 and Figure 4-3 depict the Logic 0 and Logic 1 input Bit Frames.

**t**BIT

Figure 4-2. Logic 0 Input Condition Waveform

#### 4.1.2.2 Start / Stop Condition

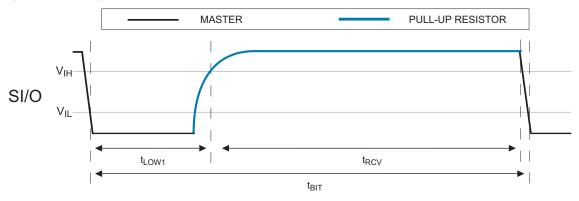

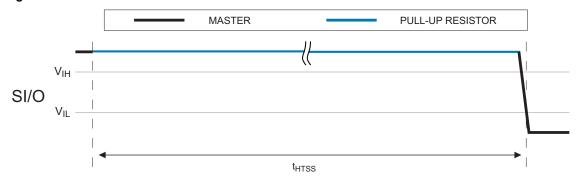

All transactions to the AT21CS01 begin with a Start condition; therefore, a Start can only be transmitted by the Master to the Slave. Likewise, all transactions are terminated with a Stop condition and thus a Stop condition can only be transmitted by the Master to the Slave.

The Start and Stop conditions require identical biasing of the SI/O line. The Start / Stop condition is created by holding the SI/O line at a voltage of V<sub>PUP</sub> for a duration of t<sub>HTSS</sub>. Refer to Section 10.4 on page 26 for timing minimums and maximums.

Figures Figure 4-4 and Figure 4-5 depict the Start and Stop Conditions.

Figure 4-4. Start Condition Waveform

Figure 4-5. Stop Condition Waveform

#### 4.1.2.3 Communication Interruptions

In the event that a protocol sequence is interrupted midstream, this sequence can be resumed at the breakpoint if the following conditions are met:

- 1. The resumption in protocol occurs prior to the maximum t<sub>BIT</sub> time elapsing. The maximum allowed value will differ if the device is High Speed Mode or Low Speed Mode (see Section 7.5 on page 17).

- 2. The break in protocol did not occur during a write operation immediately after the Logic 0 "ACK" response from the device when sending data to the device.

- In this case, the break is interpreted as a Stop condition and will cause an internal write cycle to begin.

If the protocol sequence is interrupted for longer than the maximum  $t_{BIT}$ , the Master must then wait at least the minimum  $t_{HTSS}$  before continuing. This minimum time will be influenced by the speed the device is set to (see Section 7.5 on page 17).

By waiting the minimum t<sub>HTSS</sub> time, a new Start condition is created and the device is ready to receive a new command. If desired, the Master can begin the transaction that was interrupted midstream over again.

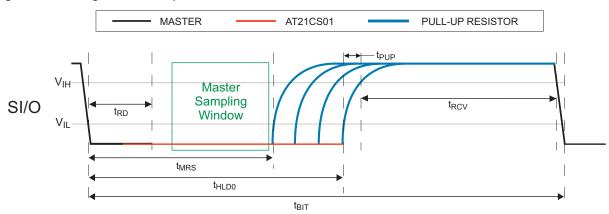

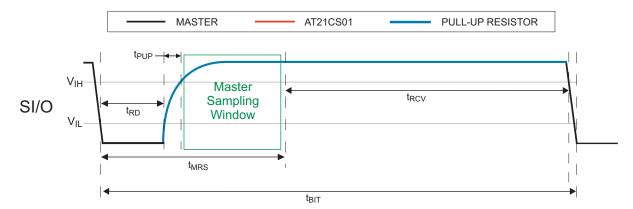

#### 4.1.2.4 Data Output Bit Frame

A data output Bit Frame is used when the Master is to receive communication back from the AT21CS01. Data output Bit Frames are used when reading any data out as well as any ACK or NACK responses from the device. Just as in the input Bit Frame, the Master initiates the sequence by driving the SI/O line below the V<sub>IL</sub> threshold which engages the AT21CS01's internal timing generation circuit.

Within the output Bit Frame is the critical timing parameter  $t_{RD}$ , which is defined as the amount of time the Master must continue to drive the SI/O line low after crossing the below  $V_{IL}$  threshold to request a data bit back from the AT21CS01. Once the  $t_{RD}$  duration has expired, the Master must release the SI/O line.

If the AT21CS01 is responding with a Logic 0 (for either a "0" data bit or an ACK response), it will begin to pull the SI/O line low concurrently during the  $t_{RD}$  window and continue to hold it low for a duration of  $t_{HLD0}$ , after which it will release the line to be pulled back up to  $V_{PUP}$  (see Figure 4-6). Thus, when the Master samples SI/O within the  $t_{MRS}$  window, it will see a voltage less than  $V_{IL}$  and decode this event as a Logic 0. By definition, the  $t_{HLD0}$  time is longer than the  $t_{MRS}$  time and therefore the Master is guaranteed to sample while the AT21CS01 is still driving the SI/O line low.

Figure 4-6. Logic 0 Data Output Bit Frame Waveform

If the AT21CS01 intends to respond with a Logic 1 (for either a "1" data bit or a NACK response), it will not drive the SI/O line low at all. Once the Master releases the SI/O line after the maximum  $t_{RD}$  has elapsed, the line will be pulled up to  $V_{PUP}$ . Thus when the Master samples the SI/O line within the  $t_{MRS}$  window, it will detect a voltage greater than  $V_{IH}$  and decode this event as a Logic 1.

The data output Bit Frame is shown in greater detail below in Figure 4-7.

Figure 4-7. Logic 1 Data Output Bit Frame Waveform

Note: AT21CS01 will not drive the SI/O line during a Logic 1 output Bit Frame.

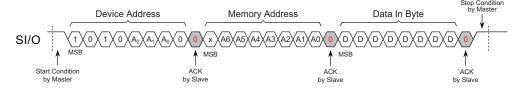

# 5. Device Addressing and I<sup>2</sup>C Protocol Emulation

Accessing the device requires a Start condition followed by an 8-bit Device Address word. The AT21CS01 protocol sequence emulates what would be required for an I<sup>2</sup>C Serial EEPROM, with the exception that the beginning four bits of the device address are used as an opcode for the different commands and actions that the device can perform.

Since multiple Slave devices can reside on the bus, each Slave device must have its own unique address so that the Master can access each device independently. After the 4-bit opcode, the following three bits of the Device Address Byte are comprised of the slave address bits. The three slave address bits are pre-programmed by Atmel prior to shipment and are read-only. Obtaining devices with different slave address bit values is done by a purchasing a specific ordering code. Please refer to Section 11., "Ordering Code Detail" on page 28 for explanation of which ordering code corresponds with a specific slave address value.

Following the three slave address bits is a Read/Write select bit where a Logic 1 indicates a Read and a Logic 0 indicates a Write. Upon the successful comparison of the Device Address, the EEPROM will return an ACK (Logic 0). If the 4-bit opcode is invalid or the three bits of slave address do not match what is preprogrammed in the device, the device will not respond on the SI/O line and will return to a standby state.

Table 5-1. Device Address Byte

| 4-bit Opcode        |       |       |                | Pre-progra     | mmed Slave A   | ddress Bits | Read/ Write |

|---------------------|-------|-------|----------------|----------------|----------------|-------------|-------------|

| Bit 7               | Bit 6 | Bit 5 | Bit 4          | Bit 3          | Bit 2          | Bit 1       | Bit 0       |

| Refer to Section 6. |       |       | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | R/W         |             |

Following the Device Address Byte, a Memory Address Byte must be transmitted to the device immediately. The Memory Address Byte contains a 7-bit memory array address to specify which location in the EEPROM to start reading or writing. Please refer to Table 5-2 to review these bit positions.

Table 5-2. Memory Address Byte

| Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| Don't Car | e A6  | A5    | A4    | A3    | A2    | A1    | A0    |

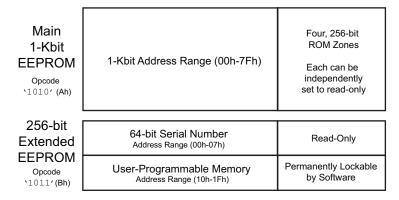

#### 5.1 Memory Organization

The AT21CS01 internal memory array is partitioned into two regions. The main 1-Kbit EEPROM is organized as 16 pages of 8 bytes each. The Extended EEPROM region is 32 bytes, organized as four pages of 8 bytes each. The lower two pages of the Extended EEPROM region are read-only and have a factory programmed, 64-bit Serial Number that is unique across all Atmel AT21CS series Serial EEPROMs. The upper two pages of the Extended EEPROM region are user-programmable and can be subsequently locked (see Section 7.4).

Figure 5-1. Memory Architecture Diagram

# 6. Available Opcodes

Table 6-1 outlines available opcodes for the AT21CS01.

Table 6-1. Opcodes used by the AT21CS01

| Command                  | 4-bit Opcode | Brief Description of Functionality                           |

|--------------------------|--------------|--------------------------------------------------------------|

| Main EEPROM Access       | 1010 (Ah)    | Read/Write the contents of the main memory array             |

| Extended EEPROM Access   | 1011 (Bh)    | Read/Write the contents of the Extended EEPROM region        |

| Lock Extended EEPROM     | 0010 (2h)    | Permanently lock the contents of the Extended EEPROM         |

| ROM Zone Register Access | 0111 (7h)    | Inhibit further modification to a zone of the EEPROM array   |

| Freeze ROM Zone State    | 0001 (1h)    | Permanently lock the current state of the ROM Zone Registers |

| Manufacturer ID Read     | 1100 (Ch)    | Query manufacturer and density of device                     |

| Standard Speed Mode      | 1101 (Dh)    | Switch to standard speed mode operation                      |

| High Speed Mode          | 1110 (Eh)    | Switch to high speed mode operation (power-on default)       |

## 6.1 Main EEPROM Access (Opcode Ah)

The opcode Ah is used to read data from and write data to the main EEPROM. Please refer to See Section 8., "Read Operations" on page 18 for more details about reading data from the device. For details about writing to the Main EEPROM, please refer to Section 7., "Write Operations" on page 14.

## 6.2 Extended EEPROM Access (Opcode Bh)

The opcode Bh is used to read data from and write data to the Extended EEPROM region. Please refer to Section 8.4, "Read Operations in the Extended EEPROM Region" on page 20 for more details about reading data from the Extended EEPROM. For details about writing to the user-programmable portion of the Extended EEPROM, please refer to section 7.3, "Writing to the Extended EEPROM" on page 15.

# 6.3 Lock Extended EEPROM (Opcode 2h)

The opcode 2h is used to permanently lock the user-programmable portion of the Extended EEPROM. Please refer to Section 7.4, "Locking the Extended EEPROM" on page 16.

# 6.4 ROM Zone Register Access (Opcode 7h)

The AT21CS01 is partitioned into four, 256-bit zones, each of which can be independently and permanently made read-only (ROM). The state of each zone is stored in a configuration register which can be read from or written to using the opcode 7h. The ROM Zone functionality is explained in greater detail in Section 9., "ROM Zones" on page 22.

# 6.5 Freeze ROM Zone State (Opcode 1h)

The opcode 1h is used to permanently freeze the current state of the ROM Zone Registers. Once set, the ROM Zone Registers are read-only; therefore, any zone that is not already read-only cannot be subsequently converted to ROM. Please refer to Section 9.2.3, "Freeze ROM Zone Registers" on page 24 for additional details.

#### 6.6 Manufacturer ID Read (Opcode Ch)

Manufacturer identification, device density, and device revision information can be read from the device using the opcode Ch. The full details of the format of the data returned by this command are found in Section 8.5, "Manufacturer ID Read" on page 21.

## 6.7 Standard Speed Mode (Opcode Dh)

The AT21CS01 can be set to Standard Speed Mode or checked to see whether or not it is in Standard Speed Mode with the use of the Dh opcode. Further details are covered in Section 7.5.1, "Standard Speed Mode" on page 17.

#### 6.8 High Speed Mode (Opcode Eh)

The AT21CS01 can be set to High Speed Mode or checked to see whether or not it is in High Speed Mode with the use of the Eh opcode. Further details are covered in Section 7.5.2, "High Speed Mode" on page 17.

# 7. Write Operations

All Write operations for the AT21CS01 begin with the Master sending a Start condition, followed by a Device Address Byte (opcode Ah for the main EEPROM and opcode Bh for the Extended EEPROM) with the  $R/\overline{W}$  bit set to '0' and then by the Memory Address Byte. The data value(s) to be written to the device immediately follow the Memory Address Byte.

The AT21CS01 allows single Byte Writes, partial Page Writes and full Page Writes.

#### 7.1 Byte Write

The AT21CS01 supports writing of single 8-bit bytes and requires a 7-bit Memory Word address to select which byte to write.

Upon receipt of the proper Device Address Byte (with opcode of Ah specified) and Memory Address Byte, the EEPROM will send a Logic 0 to signify an ACK. The device will then be ready to receive the data byte. Following receipt of the data byte, the EEPROM will respond with an ACK. A Stop condition must then occur; however, since a Stop condition is just defined as a null Bit Frame with SI/O pulled high, the Master does not need to drive the SI/O line to accomplish this. After the Stop condition is complete, the EEPROM will enter an internally self-timed write cycle, which will complete within a time of  $t_{WR}$ , while the data is being programmed into the nonvolatile EEPROM. The SI/O pin must be pulled high via the external pull-up resistor during the entire  $t_{WR}$  cycle.

Warning:

Sending a Reset and Discovery Response sequence to the device during the  $t_{WR}$  time period will interrupt the internal write cycle and may cause the byte being programmed to be corrupted. Other memory locations within the memory array will not be affected.

After the maximum t<sub>WR</sub> time has elapsed, the Master may begin a new bus transaction.

Figure 7-1. Byte Write

Note: x = Don't care bit in the place of A7 as this bit falls outside the 1-Kbit addressable range.

# 7.2 Page Write

A Page Write operation allows up to eight bytes to be written in the same write cycle, provided all bytes are in the same row (address bits A6 through A3 are the same) of the memory array. Partial Page Writes of less than eight bytes are allowed.

A Page Write is initiated the same way as a Byte Write, but the Bus Master does not send a Stop condition after the first data byte is clocked in. Instead, after the EEPROM acknowledges receipt of the first data byte, the Bus Master can transmit up to an additional seven data bytes. The EEPROM will respond with an ACK after each data byte is received. Once all data bytes have been sent, the device requires a Stop condition to begin the write cycle. However, since a Stop condition is defined as a null Bit Frame with SI/O pulled high, the Master does not need to drive the SI/O line to accomplish this. After the Stop condition is complete, the internally self-timed write cycle will begin. The SI/O pin must be pulled high via the external pull-up resistor during the entire t<sub>WR</sub> cycle. Therefore, in a multi-slave environment, communication to other devices on the Single-Wire bus should not be executed while any devices are in a self-timed, internal write cycle.

The lower three bits of the memory address are internally incremented following the receipt of each data byte. The higher order address bits are not incremented, and the device retains the memory row location. Page Write operations are limited to writing bytes within a single physical page, regardless of the number of bytes actually

being written. When the incremented word address reaches the page boundary, the address counter will "roll over" to the beginning of the same page. Nevertheless, creating a roll over event should be avoided as previously loaded data in the page could become unintentionally altered.

**Warning:** Sending a Reset and Discovery Response sequence to the device during the t<sub>WR</sub> time period will interrupt the internal write cycle and may cause the bytes being programmed to be corrupted. Other memory locations within the memory array will not be affected.

After the maximum t<sub>WR</sub> time has elapsed, the Master may begin a new bus transaction.

Figure 7-2. Page Write

Note: x = Don't care bit in the place of A7 as this bit falls outside the 1-Kbit addressable range.

#### 7.3 Writing to the Extended EEPROM

The Extended EEPROM region supports Bytes Writes, Page Writes, and Partial Page Writes in the upper 16 bytes (upper two pages of 8 bytes each) of the region. Page Writes and Partial Page Writes in the Extended EEPROM have the same page boundary restrictions and behavior as they do in the main EEPROM region (see Section 7.2 "Page Write" on page 14).

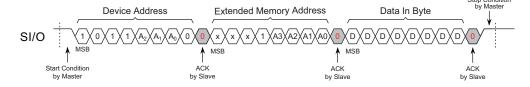

Upon receipt of the proper Device Address Byte (with opcode of Bh specified) and Memory Address Byte, the EEPROM will send a Logic 0 to signify an ACK. The device will then be ready to receive the first data byte. Following receipt of the data byte, the EEPROM will respond with an ACK and the Master can send up to an additional seven bytes if desired. The EEPROM will respond with an ACK after each data byte is successfully received. Once all of the data bytes have been sent, the device requires a Stop condition to begin the write cycle. However, since a Stop condition is defined as a null Bit Frame with SI/O pulled high, the Master does not need to drive the SI/O line to accomplish this. After the Stop condition is complete, the EEPROM will enter an internally self-timed write cycle, which will complete within a time of  $t_{WR}$ , while the data is being programmed into the nonvolatile EEPROM. The SI/O pin must be pulled high via the external pull-up resistor during the entire  $t_{WR}$  cycle. Figure 7-3 is included below as an example of a Byte Write operation in the Extended EEPROM region.

Figure 7-3. Byte Write in the Extended EEPROM Region

Note: x = Don't care bit in the place of A7 as this bit falls outside the 1-Kbit addressable range.

Warning: Sending a Reset and Discovery Response sequence to the device during the t<sub>WR</sub> time period will interrupt the internal write cycle and may cause the bytes being programmed to be corrupted. Other memory locations within the memory array will not be affected.

#### 7.4 Locking the Extended EEPROM

The Lock command is an irreversible sequence that will permanently prevent all future writing to the upper 16 bytes of the Extended EEPROM on the AT21CS01. Once the Lock command has been executed, the entire 32 byte Extended EEPROM region becomes read-only. Once the region has been locked, *it is not possible to unlock it.*

The Lock command protocol emulates a Byte Write operation to the Extended EEPROM, however, the opcode '0010' (2h) is required along with the A7 through A4 bits of the Memory Address being set to '0110' (6h). The remaining bits of the Memory Address, as well as the Data Byte are don't care bits. Even though these bits are don't cares, they still must be transmitted to the device. An ACK response to the Memory Address and Data Byte indicates the Extended EEPROM is not currently locked. A NACK response indicates the Extended EEPROM region is already locked. Please refer to Section 7.4.2 for details about determining the Lock status of the Extended EEPROM region.

The sequence completes with a Stop condition to initiate a self-timed internal write cycle. However, since a Stop condition is defined as a null Bit Frame with SI/O pulled high, the Master does not need to drive the SI/O line to accomplish this. Upon completion of that write cycle, which will complete with a time of  $t_{WR}$ , the Lock operation will complete and the Extended EEPROM will become permanently read-only.

Figure 7-4. Lock Command

#### 7.4.1 Device Response to a Write Command on a Locked Device

A locked device will respond differently to a write command to the Extended EEPROM compared to a device that has not been locked. Writing to the Extended EEPROM is accomplished by sending a Start condition followed by a Device Address Byte with the opcode of '1011' (Bh), the appropriate slave address combination, and the Read/Write bit set as a Logic 0. Both a locked device and a device that has not been locked will return an ACK. Next the 8-bit Word Address is sent and again, both devices will return an ACK. However, upon sending the Data Input byte, a device that has already been locked will return a NACK and be immediately ready to accept a new command, whereas a device that has not been locked will return an ACK to the Data Input byte as per normal operation for a write command as described in Section 7. on page 14.

#### 7.4.2 Check Lock Command

The Check Lock command follows the same sequence as the Lock command (including `0110' in the A7 through A4 bits of the Memory Address Byte) with the exception that only the Device Address Byte and Memory Address Byte need to be transmitted to the device. An ACK response to the Memory Address Byte indicates that the Lock has not been set while a NACK response indicates that the Lock has been set. If the Lock has already been enabled, it cannot be reversed. The Check Lock command is completed by the Master sending a Stop bit to the device (defined as a null Bit Frame).

Figure 7-5. Check Lock Command

#### 7.5 Setting the Device Speed

The AT21CS01 can be set to Standard Speed Mode (15.4kbps max) or High Speed Mode (125kbps max) through a software sequence. Upon executing a Reset and Discovery Response sequence (see Section 4.1.1 on page 6), the device will default to High Speed Mode.

#### 7.5.1 Standard Speed Mode

The device can be set to Standard Speed Mode or checked to see whether or not it is in Standard Speed Mode with the use of the Dh opcode. This transaction only requires eight bits.

To set the device to Standard Speed Mode, the Master must send a Start condition, followed by the Device Address Byte with the opcode of `1101' (Dh) specified, along with the appropriate slave address combination and the Read/Write bit set to a Logic 0. The device will return an ACK (Logic 0) and will be immediately ready to receive commands for Standard Speed Operation.

To determine if the device is already set to Standard Speed Mode, the Device Address Byte with the opcode of `1101' (Dh) must be sent to the device, along with the appropriate slave address combination and the Read/Write bit set to a Logic 1. The device will return an ACK (Logic 0) if it was set for Standard Speed Mode. It will return a NACK (Logic 1) if the device was not currently set for Standard Speed Mode.

#### 7.5.2 High Speed Mode

The device can be set to High Speed Mode or checked to see whether or not it is in High Speed Mode with the use of the Eh opcode. This transaction only requires eight bits. The power-on default for the device is High Speed Mode.

To set the device to High Speed Mode, the Master must send a Start condition, followed by the Device Address Byte with the opcode of `1110' (Eh) specified, along the appropriate slave address combination and the Read/Write bit set to a Logic 0. The device will return an ACK (Logic 0) and will be immediately ready to receive commands for High Speed Operation.

To determine if the device is already set to High Speed Mode, the Device Address Byte with the opcode of '1110' (Eh) specified, must be sent to the device, along with the appropriate slave address combination and the Read/Write bit set to a Logic 1. The device will return an ACK (Logic 0) if it was set for High Speed Mode. It will return a NACK (Logic 1) if the device was not currently set for High Speed Mode.

# 8. Read Operations

Read operations are initiated in a similar way as Write operations with the exception that the Read/Write select bit in the Device Address Byte must be set to a Logic 1. There are multiple Read operations supported by the device:

- Current Address Read within the Main EEPROM

- Random Read within the Main EEPROM

- Seguential Read within the Main EEPROM

- Read from the Extended EEPROM

- Manufacturer ID Read

Warning:

The AT21CS01 contains a single, shared memory address pointer that maintains the address of the next byte in the main EEPROM or Extended EEPROM region to be accessed. For example, if the last byte read or written was memory location 0Dh of the main EEPROM, then the address pointer will be pointing to memory location 0Eh of the main EEPROM. As such, when changing from a Read in one region to the other, the first read operation in the new region should begin with a Random Read instead of a Current Address Read to ensure the address pointer is set to a known value within the desired region.

If the end of the main EEPROM or the Extended EEPROM region is reached, then the address pointer will "roll over" back to the beginning (address 00h) of that region. The address pointer retains its value between operations as long as the pull-up voltage on the SI/O pin is maintained or as long as the device has not been reset. If the device has been power cycled or reset, then the internal address pointer will default to 00h.

#### 8.1 Current Address Read within the Main EEPROM

The internal address pointer must be pointing to a memory location within the main EEPROM in order to perform a Current Address Read from the main EEPROM. To initiate the operation, the Master must send a Start condition, followed by the Device Address Byte with the opcode of `1010' (Ah) specified, along with the appropriate slave address combination and the Read/Write bit set to a Logic 1. After the Device Address Byte has been sent, the AT21CS01 will return an ACK (Logic 0).

Following the ACK, the device is ready to output one byte (eight bits) of data. The Master initiates the all bits of data by driving the SI/O line low to start. The AT21CS01 will hold the line low after the Master releases it to indicate a Logic 0. If the data is Logic 1, the AT21CS01 will not hold the SI/O line low at all, causing it to be pulled high by the pull-up resistor one the Master releases it. This sequence repeats for eight bits.

After the Master has read the first data byte and no further data is desired, the Master must return a NACK (Logic 1) response to end the Read operation and return the device to the standby mode. Figure 8-1 depicts this sequence.

If the Master would like the subsequent byte, it would return an ACK (Logic 0) and the device will be ready output the next byte in the memory array. Please refer to Section 8.3, "Sequential Read within the Main EEPROM" for details about continuing to read beyond one byte.

**Warning:** If the last operation to the device was an access to the Extended EEPROM, then a Random Read should be performed to ensure that the address pointer is set to a known memory location within the main EEPROM.

Figure 8-1. Current Address Read

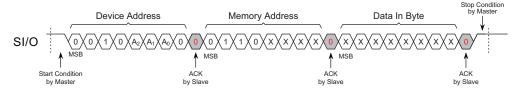

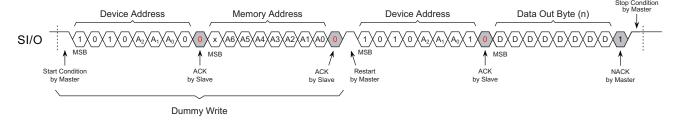

#### 8.2 Random Read within the Main EEPROM

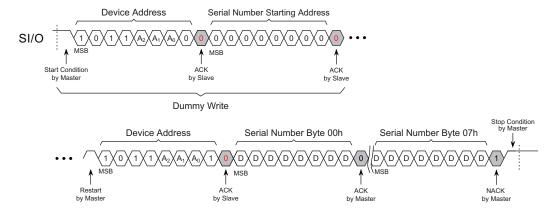

A Random Read begins in the same way as a Byte Write operation which will load a new main EEPROM memory address into the address pointer. However, instead of sending the Data byte and Stop condition of the Byte Write, a repeated Start condition is sent to the device. This sequence is referred to as a "dummy write". After the Device Address and Memory Address Bytes of the "dummy write" have been sent, the AT21CS01 will return an ACK response. The Master can then initiate a Current Address Read, beginning with a new Start condition, to read data from the main EEPROM. Please refer to Section 8.1 for details on how to perform a Current Address Read.

Figure 8-2. Random Read

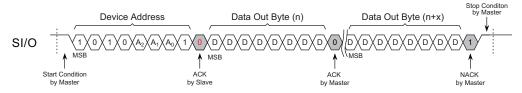

#### 8.3 Sequential Read within the Main EEPROM

Sequential Reads start as either a Current Address Read or as a Random Read. However, instead of the Master sending a NACK (Logic 1) response to end a Read operation after a single byte of data has been read, the Master sends an ACK (Logic 0) to instruct the AT21CS01 to output another byte of data. As long as the device receives an ACK from the Master after each byte of data has been output, it will continue to increment the address counter and output the next byte data from the main EEPROM. If the end of the main EEPROM is reached, then the address pointer will "roll over" back to the beginning (address 00h) of the main EEPROM region. To end the Sequential Read operation, the Master must send a NACK response after the device has output a complete byte of data. After the device receives the NACK, it will end the Read operation and return to the standby mode.

**Warning:** If the last operation to the device accessed the Extended EEPROM, then a Random Read should be performed to ensure that the address pointer is set to a known memory location within the main EEPROM.

Figure 8-3. Sequential Read from a Current Address Read

Figure 8-4. Sequential Read from a Random Read

#### 8.4 Read Operations in the Extended EEPROM Region

The Extended EEPROM can be read by using either a Random Read or a Sequential Read operation. Due to the fact that the Main EEPROM and Extended EEPROM share a single address pointer register, a "dummy write" must be performed to correctly set the address pointer in the Extended EEPROM region. This is why a Random Read or Sequential Read must be used as these sequences include a "dummy write." Current Address Reads of the Extended EEPROM are not supported.

In order to read the Extended EEPROM, the Device Address Byte must be specified with the opcode `1011' (Bh) instead of the opcode `1010' (Ah). The Extended EEPROM can be read to read the 64-bit Serial Number or the remaining user-programmable data.

#### 8.4.1 Serial Number Read

The lower 8 bytes of the Extended EEPROM region contain a factory programmed, guaranteed unique, 64-bit Serial Number. In order to guarantee a unique value, the entire 64-bit Serial Number must be read starting at Extended EEPROM address location 00h. Therefore, it is recommended that a Sequential Read started with a Random Read operation be used, ensuring that the Random Read sequence uses a Device Address Byte with opcode `1011' (Bh) specified in addition to the Memory Address Byte being set to 00h.

The first byte read out of the 64-bit Serial Number is the Product Identifier (A0h). Following the Product Identifier, a 48-bit unique number is contained in bytes 1 though 6. The last byte of the serial number contains a cyclic redundancy check (CRC) of the other 56 bits. The CRC is generated using the polynomial  $X^8 + X^5 + X^4 + 1$ . The structure of the 64-bit Serial Number is depicted in Table 8-1.

Table 8-1. 64-bit Factory Programmed Serial Number Organization

| Byte 7             | Byte 6 | Byte 5 | Byte 4      | Byte 3    | Byte 2 | Byte 1 | Byte 0                                  |

|--------------------|--------|--------|-------------|-----------|--------|--------|-----------------------------------------|

| 8-bit<br>CRC Value |        |        | 48-bit Uniq | ue Number |        |        | 8-bit<br>Product<br>Identifier<br>(A0h) |

After all 8 bytes of the Serial Number have been read, the Master can return a NACK (Logic 1) response to end the Read operation and return the device to the standby mode. If the Master sends an ACK (Logic 0) instead of a NACK, then the next byte (address location 08h) in the Extended EEPROM will be output. If the end of the Extended EEPROM region is reached, then the address pointer will "roll over" back to the beginning (address location 00h) of the Extended EEPROM region.

Figure 8-5. Serial Number Read

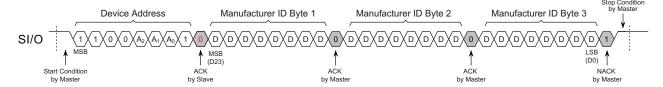

#### 8.5 Manufacturer ID Read

The AT21CS01 offers the ability to query the device for manufacturer, density, and revision information. By using a specific opcode and following the format of a Current Address Read, the device will return a 24-bit value that corresponds with the I<sup>2</sup>C identifier value reserved for Atmel, along with further data to signify a 1-Kbit density and the device revision.

To read the Manufacturer ID data, the Master must send a Start condition, followed by the Device Address Byte with the opcode of `1100' (Ch) specified, along the appropriate slave address combination and the Read/Write bit set to a Logic 1. After the Device Address Byte has been sent, the AT21CS01 will return an ACK (Logic 0). If the Read/Write bit is set to a Logic 0 to indicate a write, the device will NACK (Logic 1) since the Manufacturer ID data is read-only.

After the device has returned an ACK, it will then send the first byte of Manufacturer ID data which contains the eight most significant bits (D23 — D16) of the 24-bit data value. The Master can then return an ACK (Logic 0) to indicate it successfully received the data, upon which the device will send the second byte (D15 — D8) of Manufacturer ID data. The process repeats until all three bytes have been read out and the Master sends a NACK (Logic 1) to complete the sequence. Figure 8-6 depicts this sequence below. If the Master ACKs (Logic 0) the third byte, the internal pointer will roll over back to the first byte of Manufacturer ID data.

Figure 8-6. Manufacturer ID Read

Table 8-2 below provides the format of the Manufacturer ID data.

Table 8-2. Manufacturer ID Data Format

|                 |             | Bit Position within | AT21CS01 Response |           |                          |  |

|-----------------|-------------|---------------------|-------------------|-----------|--------------------------|--|

| Data Type       | Field Width | 24-bit value        | Binary Value      | Hex Value | Indication               |  |

| Manufacturer    | 12 bits     | D23 — D12           | 0000-0000-1101    | 00Dh      | Reserved Value for Atmel |  |

| Device Density  | 9 bits      | D11 — D3            | 0010-0000-0       | 200h      | Single Wire, 1Kb         |  |

| Device Revision | 3 bits      | D2 — D0             | 000               | 20011     | Revision 1               |  |

The Manufacturer Identifier portion of the ID is returned in the 12 most significant bits of the three bytes read out. The value reserved for Atmel is 0000-0000-1101' (00Dh). Therefore, the first byte read out by the device will be 00h. The upper nibble of the second byte read out is Dh.

The least significant 12 bits of the 24-bit ID is comprised of an Atmel defined value that indicates the device density and revision. Bits D11 through D3 indicate the device density and bits D2 through D0 indicate the device revision. The output is shown more specifically in Table 8-2.

The overall 24-bit value returned by the AT21CS01 is 00D200h.

#### 9. ROM Zones

#### 9.1 ROM Zone Size and ROM Zone Registers

Certain applications require that portions of the EEPROM memory array be permanently protected against malicious attempts at altering program code, data modules, security information, or encryption/decryption algorithms, keys, and routines. To address these applications, the memory array is segmented into four different memory zones of 256 bits each. A ROM Zone mechanism has been incorporated that allows any combination of individual memory zones to be permanently locked so that they become read-only (ROM). Once a memory zone has been converted to ROM, it can never be erased or programmed again, and it can never be unlocked from the ROM state. Table 9-2 shows the address range of each of the four memory zones.

#### 9.1.1 ROM Zone Registers

Each 256-bit memory zone has a corresponding single-bit ROM Zone Register that is used to control the ROM status of that zone. These registers are nonvolatile and will retain their state even after a device power cycle or reset operation. The following table outlines the two states of the ROM Zone Registers. Each ROM Zone Register has specific ROM Zone Register Address that is reserved for read or write access.

Table 9-1. ROM Zone Register Values

| Value | ROM Zone Status                                                                                |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------|--|--|--|--|

| 0     | ROM Zone is not enabled and that memory zone can be programmed and erased (the default state). |  |  |  |  |

| 1     | ROM Zone is enabled and that memory zone can never be programmed or erased again.              |  |  |  |  |

Issuing the ROM Zone command to a particular ROM Zone Register Address will set the corresponding ROM Zone Register to the Logic 1 state. Each ROM Zone Register can only be set once; therefore, once set to the Logic 1 state, a ROM Zone cannot be reset back to the Logic 0 state.

Table 9-2. ROM Zone Address Ranges

| Memory Zone | Starting Memory Address | Ending Memory Address | ROM Zone<br>Register Address |

|-------------|-------------------------|-----------------------|------------------------------|

| 0           | 0h                      | 1Fh                   | 01h                          |

| 1           | 20h                     | 3Fh                   | 02h                          |

| 2           | 40h                     | 5Fh                   | 04h                          |

| 3           | 60h                     | 7Fh                   | 08h                          |

## 9.2 Programming and Reading the ROM Zone Registers

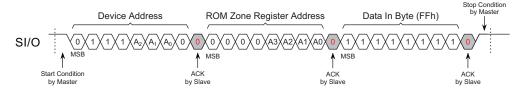

#### 9.2.1 Reading the status of a ROM Zone Register

To check the current status of a ROM Zone Register, the Master must emulate a Random Read sequence with the exception that the opcode '0111' (7h) will be used. The dummy write portion of the Random Read sequence is needed to specify which ROM Zone Register address is to be read.

This sequence begins by the Master sending a Start condition, followed by a Device Address Byte with the opcode of 7h in the four most significant bits, along with the appropriate slave address combination and the Read/Write bit set to a Logic 0. The AT21CS01 will respond with an ACK. Next, the ROM Zone Register address intended to be read is transmitted to the device, and the device will ACK this byte as well. Then an additional Start condition is

sent to the device with the same Device Address Byte as before, but now with the Read/Write bit set to a Logic 1, to which the device will return an ACK.

Following this Device Address Byte is an 8-bit ROM Zone Register Address byte. The four most significant bits are not used and are therefore don't care bits. The address sent to the device must match one of the ROM Zone Register Addresses specified in Table 9-2. After the ROM Zone Register Address has been sent, the AT21CS01 will return an ACK (Logic 0).

After the AT21CS01 has sent the ACK, the device will output either 00h or FFh data byte. A 00h data byte indicates that the ROM Zone Register is 0, meaning the zone has not been set as ROM. If the device outputs FFh data, then the memory zone has been set to ROM and cannot be altered.

Table 9-3. Read ROM Zone Register – Output Data

| Output Data | ROM Zone Register Value                                        |

|-------------|----------------------------------------------------------------|

| 00h         | ROM Zone Register value is 0 (zone is not set as ROM).         |

| FFh         | ROM Zone Register value is 1 (zone is permanently set as ROM). |

Figure 9-1. Reading the State of a ROM Zone Register

#### 9.2.2 Writing to a ROM Zone Register

A ROM Zone Register can only be written to a Logic 1 which will set the corresponding memory zone to a ROM state. Once a ROM Zone Register has been written, it can never be altered again.

To write to a ROM Zone Register, the Master must send a Start condition, followed by the Device Address Byte with the opcode of '0111' (7h) specified, along with the appropriate slave address combination and the Read/Write bit set to a Logic 0. The device will return an ACK. After the Device Address Byte has been sent, the AT21CS01 will return an ACK.

Following the Device Address Byte is an 8-bit ROM Zone Register Address byte. The address sent to the device must match one of the ROM Zone Register Addresses specified in Table 9-2. After the ROM Zone Register Address has been sent, the AT21CS01 will return an ACK.

After the AT21CS01 has sent the ACK, the Master must send an FFh data byte in order to set the appropriate ROM Zone Register to the Logic 1 state. The device will then return an ACK and, after a Stop condition is executed, the device will enter a self-time internal write cycle, lasting  $t_{WR}$ . The device will not respond till any commands until the  $t_{WR}$  time has completed. This sequence is depicted in Figure 9-2.

Figure 9-2. Writing to a ROM Zone Register

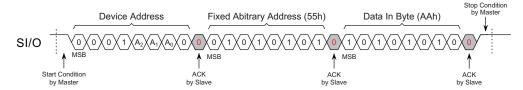

#### 9.2.3 Freeze ROM Zone Registers

The current ROM Zone state can be frozen so that no further modifications to the ROM Zone Registers can be made. Once frozen, this event cannot be reversed.

To freeze the state of the ROM Zone Registers, the Master must send a Start condition, followed by the Device Address Byte with the opcode of `0001' (1h) specified, along with the appropriate slave address combination and the Read/Write bit set to a Logic 0. The device will return either an ACK (Logic 0) response if the ROM Zone Registers have not been previously frozen or a NACK (Logic 1) response if the registers have already been frozen.

If the AT21CS01 returns an ACK, the Master must send a fixed arbitrary address byte value of 55h, to which the device will return an ACK (Logic 0). Following the 55h Address byte, a Data byte of AAh must be sent by the Master. The device will ACK after the AAh data byte. If an Address byte other than 55h or a Data byte other than AAh is sent, the device will NACK (Logic 1) and the freeze operation will not be performed.

To complete the Freeze ROM Zone Register sequence, a Stop condition is required. However, since a Stop condition is defined as a null Bit Frame with SI/O pulled high, the Master does not need to drive the SI/O line to accomplish this. After the Stop condition is complete, the internally self-timed write cycle will begin. The SI/O pin must be pulled high via the external pull-up resistor during the entire  $t_{WR}$  cycle.

Figure 9-3. Freezing the ROM Zone Registers

**Warning:** Sending a Reset and Discovery Response sequence to the device during the t<sub>WR</sub> time period will interrupt the internal write cycle and may cause the freeze operation to not complete correctly.

#### 9.3 Device Response to a Write Command Within an Enabled ROM Zone

The AT21CS01will respond differently to a write command in a memory zone that has been set to ROM compared to write command in a memory zone that has not been set to ROM. Writing to the Main EEPROM is accomplished by sending a Start condition followed by a Device Address Byte with the opcode of '1010' (Ah), the appropriate slave address combination, and the Read/Write bit set as a Logic 0. Since a memory address has not been input at this point in the sequence, the device return an ACK. Next, the 8-bit Word Address is sent which will result in an ACK from the device, regardless if that address is in a memory zone that has been set to ROM. However, upon sending the Data Input byte, a write command to an address that was in a memory zone that was set to ROM will result in a NACK response from the AT21CS01 and the device will be immediately ready to accept a new command. If the address being written was in a memory zone that had not been set to ROM, the device will return an ACK to the Data Input byte as per normal operation for write operations as described in Section 7. on page 14.

# 10. Electrical Specifications

#### 10.1 Absolute Maximum Ratings

Functional operation at the "Absolute Maximum Ratings" or any other conditions beyond those indicated in Section 10.2 is not implied or guaranteed. Stresses beyond those listed under "Absolute Maximum Ratings" and/or exposure to the "Absolute Maximum Ratings" for extended periods may affect device reliability and cause permanent damage to the device.

The voltage extremes referenced in the "Absolute Maximum Ratings" are intended to accommodate short duration undershoot/overshoot pulses that the device may be subjected to during the course of normal operation and does not imply or guarantee functional device operation at these levels for any extended period of time.

### 10.2 DC and AC Operating Range

|                                       |                              | AT21CS01       |

|---------------------------------------|------------------------------|----------------|

| Operating Temperature (Case)          | Industrial Temperature Range | –40°C to +85°C |

| V <sub>PUP</sub> Voltage tied to SI/O | Low Voltage Grade            | 1.7V to 3.6V   |

#### 10.3 DC Characteristics

Parameters are applicable over the operating range in Section 10.2, unless otherwise noted.

| Symbol           | Parameter                       | Test Condition          | 1                       | Min                    | Typical <sup>(1)</sup> | Max                    | Units |

|------------------|---------------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|-------|

| V <sub>PUP</sub> | Pull-up Voltage                 | High Speed Mo           | High Speed Mode         |                        |                        | 3.6                    | V     |

| ▼ PUP            | r un-up voltage                 | Standard Spee           | d Mode                  | 2.7                    |                        | 3.6                    | V     |

|                  |                                 | V <sub>PUP</sub> = 1.7V |                         | 130                    |                        | 200                    | Ω     |

| R <sub>PUP</sub> | Pull-up Resistance              | V <sub>PUP</sub> = 2.7V |                         | 0.2                    |                        | 1.8                    | kΩ    |

|                  |                                 | V <sub>PUP</sub> = 3.6V |                         | 0.33                   |                        | 4                      | kΩ    |

| I <sub>A1</sub>  | Active Current, Read            | V <sub>PUP</sub> = 3.6V | SI/O = V <sub>PUP</sub> | _                      | 0.08                   | 0.3                    | mA    |

| I <sub>A2</sub>  | Active Current, Write           | V <sub>PUP</sub> = 3.6V |                         | _                      | 0.20                   | 0.5                    | mA    |

| I <sub>SB</sub>  | Standby Current                 | $V_{PUP} = 1.8V^{(2)}$  | SI/O = V <sub>PUP</sub> | _                      | 0.5                    | 1.0                    | μA    |

| 'SB              | Standby Current                 | V <sub>PUP</sub> = 3.6V | _                       | 0.6                    | 1.5                    | μA                     |       |

| V <sub>IL</sub>  | Input Low Level <sup>(2)</sup>  |                         |                         | -0.6                   |                        | V <sub>PUP</sub> x 0.3 | V     |

| V <sub>IH</sub>  | Input High Level <sup>(2)</sup> |                         |                         | V <sub>PUP</sub> x 0.7 |                        | V <sub>PUP</sub> + 0.5 | V     |

| V <sub>HYS</sub> | SI/O Hysteresis                 |                         |                         | 0.128                  |                        | 1.17                   | V     |

| V <sub>OL</sub>  | Output Low Level                | I <sub>OL</sub> = 4mA   |                         | 0                      |                        | 0.4                    | V     |

| C <sub>BUS</sub> | Bus Capacitance                 |                         |                         | _                      |                        | 1000                   | pF    |

Notes: 1. Typical values characterized at  $T_A = +25$ °C unless otherwise noted.

2. This parameter is characterized but is not 100% tested in production.

#### 10.4 AC Characteristics

#### 10.4.1 Reset and Discovery Response Timing

Parameters applicable over operating range in Section 10.2, unless otherwise noted. Test conditions shown in Note 3.

|                    |                                           | Standard | l Speed <sup>(1)</sup> | High | Speed                               |       |

|--------------------|-------------------------------------------|----------|------------------------|------|-------------------------------------|-------|

| Symbol             | Parameter and Condition                   | Min      | Max                    | Min  | Max                                 | Units |

| t <sub>RESET</sub> | Reset Low Time                            | 480      | _                      | 48   | _                                   | μs    |

| t <sub>RRT</sub>   | Reset Recovery time                       | n/a      | n/a                    | 8    | _                                   | μs    |

| t <sub>DRR</sub>   | Discovery Response Request                | n/a      | n/a                    | 1    | 2 - t <sub>PUP</sub> <sup>(2)</sup> | μs    |

| t <sub>DACK</sub>  | Discovery Response Acknowledge Time       | n/a      | n/a                    | 8    | 24                                  | μs    |

| t <sub>MSDR</sub>  | Master Strobe Discovery Response Time     | n/a      | n/a                    | 2    | 6                                   | μs    |

| t <sub>HTSS</sub>  | SI/O High Time for Start / Stop Condition | n/a      | n/a                    | 150  | _                                   | μs    |

- Notes: 1. Due to the fact that the device will default to High Speed mode upon reset, the Reset and Discovery Response Timing after t<sub>RESET</sub> does not apply for Standard Speed Mode. High Speed Mode timing applies in all cases after

- 2.  $t_{PLIP}$  is the time required once the SI/O line is released to be pulled up from  $V_{IL}$  to  $V_{IH}$ . This value is application specific and is a function of the loading capacitance on the SI/O line as well as the R<sub>PUP</sub> chosen. Limits for these values are provided in Section 10.3.

- 3. AC measurement conditions for the table above:

- Loading capacitance on SI/O: 100pF

- $R_{PUP}$  (bus line pull-up resistor to  $V_{PUP}$ ):  $1k\Omega$ ;  $V_{PUP}$ : 2.7V

#### 10.4.2 Data Communication Timing

Parameters applicable over operating range in Section 10.2, unless otherwise noted. Test conditions shown in Note 1.

|                    |                                              |                               | Standar                  | d Speed                             | High S                                                    | Speed                               |       |

|--------------------|----------------------------------------------|-------------------------------|--------------------------|-------------------------------------|-----------------------------------------------------------|-------------------------------------|-------|

| Symbol             | Parameter and Condition                      | Frame Type                    | Min                      | Max                                 | Min                                                       | Max                                 | Units |

| t <sub>BIT</sub>   | Bit Frame Duration                           | Input and Output<br>Bit Frame | 40                       | 100                                 | $t_{\text{LOW0}} + t_{\text{PUP}}^{(2)} + t_{\text{RCV}}$ | 25                                  | μs    |

| t <sub>HTSS</sub>  | SI/O High Time for Start / Stop<br>Condition | Input Bit Frame               | 600                      | _                                   | 150                                                       | _                                   | μs    |

| t <sub>LOW0</sub>  | SI/O Low Time, Logic 0 Condition             | Input Bit Frame               | 24                       | 64                                  | 6                                                         | 16                                  | μs    |

| t <sub>LOW1</sub>  | SI/O Low Time, Logic 1 Condition             | Input Bit Frame               | 4                        | 8                                   | 1                                                         | 2                                   | μs    |

| t <sub>RD</sub>    | Master SI/O Low Time During Read             | Output Bit Frame              | 4                        | 8 - t <sub>PUP</sub> <sup>(2)</sup> | 1                                                         | 2 - t <sub>PUP</sub> <sup>(2)</sup> | μs    |

| t <sub>MRS</sub>   | Master Read Strobe Time                      | Output Bit Frame              | $t_{RD} + t_{PUP}^{(2)}$ | 8                                   | $t_{RD} + t_{PUP}^{(2)}$                                  | 2                                   | μs    |

| t <sub>HLD0</sub>  | Data Output Hold Time (Logic 0)              | Output Bit Frame              | 8                        | 24                                  | 2                                                         | 6                                   | μs    |

| t <sub>RCV</sub>   | Slave Recovery Time                          | Input and Output<br>Bit Frame | 8                        | _                                   | <b>2</b> <sup>(3)</sup>                                   | _                                   | μs    |

| t <sub>NOISE</sub> | Noise filtering capability on SI/O           | Input Bit Frame               | 0.5                      | _                                   | _                                                         | _                                   | μs    |

Notes: 1. AC measurement conditions for the table above:

- Loading capacitance on SI/O: 100pF

- $R_{PUP}$  (bus line pull-up resistor to  $V_{PUP}$ ):  $1k\Omega$ ;  $V_{PUP}$ : 2.7V

- 2.  $t_{PUP}$  is the time required once the SI/O line is released to be pulled up from  $V_{IL}$  to  $V_{IH}$ . This value is application specific and is a function of the loading capacitance on the SI/O line as well as the R<sub>PUP</sub> chosen. Limits for these values are provided in Section 10.3.

- 3. The system designer must select an combination of  $R_{PUP}$ ,  $C_{BUS}$ , and  $t_{BIT}$  such that the minimum  $t_{RCV}$  is satisfied. The relationship of  $t_{RCV}$  within the bit frame can be expressed by the following formula:  $t_{BIT} = t_{LOW0} + t_{PUP} + t_{RCV}$ .

#### 10.5 EEPROM Cell Performance Characteristics

| Operation                      | Test Condition                                                                                                       | Min       | Max | Units        |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------|-----|--------------|

| Write Cycle Time               | T <sub>A</sub> = 25°C, V <sub>PUP</sub> (min) < V <sub>PUP</sub> < V <sub>PUP</sub> (max)<br>Byte or Page Write Mode | _         | 5   | ms           |

| Write Endurance <sup>(1)</sup> | T <sub>A</sub> = 25°C, V <sub>PUP</sub> (min) < V <sub>PUP</sub> < V <sub>PUP</sub> (max)<br>Byte or Page Write Mode | 1,000,000 | _   | Write Cycles |

| Data Retention <sup>(2)</sup>  | $T_A = 55^{\circ}C$ , $V_{PUP}(min) < V_{PUP} < V_{PUP}(max)$                                                        | 100       | _   | Years        |

Notes: 1. Write endurance performance is determined through characterization and the qualification process.

2. The data retention capability is determined through qualification and checked on each device in production.

#### 10.6 Device Default Condition from Atmel

The AT21CS01 is delivered with the EEPROM array set to Logic 1 state resulting in FFh data in all locations.

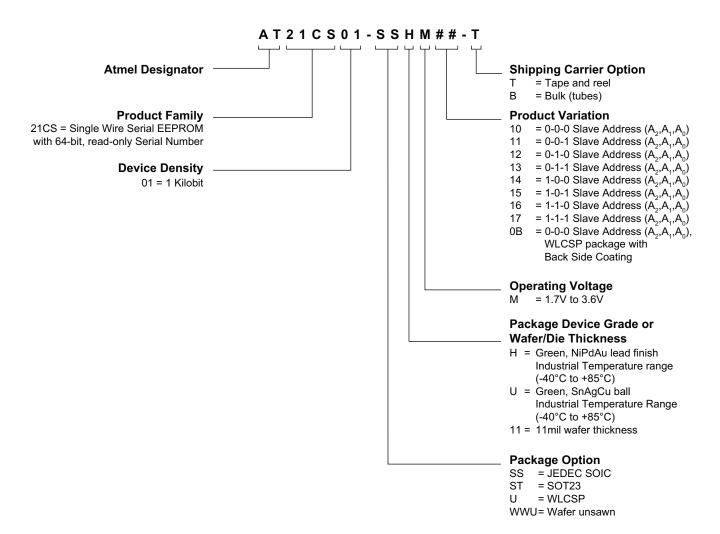

# 11. Ordering Code Detail

# 12. Ordering Information

|                                 |                                       | Delivery Informa |               | Delivery Information |                                        |

|---------------------------------|---------------------------------------|------------------|---------------|----------------------|----------------------------------------|

| Atmel Ordering Code             | Lead Finish                           | Package          | Form          | Quantity             | Operation<br>Range                     |

| AT21CS01-SSHM##-T               | NiPdAu                                | 8S1              | Tape and Reel | 4,000 per Reel       |                                        |

| AT21CS01-SSHM##-B               | (Lead-free/Halogen-free)              | 001              | Bulk (Tubes)  | 100 per Tube         |                                        |

| AT21CS01-STUM##-T               | Matte Tin<br>(Lead-free/Halogen-free) | 3TS1             | Tape and Reel | 5,000 per Reel       | Industrial Temperature (–40°C to 85°C) |

| AT21CS01-UUM0B-T <sup>(1)</sup> | SnAgCu<br>(Lead-free/Halogen-free)    | 4U-6             | Tape and Reel | 5,000 per Reel       |                                        |

| AT21CS01-WWU11M <sup>(2)</sup>  | N/A                                   | Wafer Sale       | Note 2        |                      |                                        |

#### Notes: 1. WLCSP Package

- This device includes a backside caoting to increase product robustness.

- CAUTION: Exposure to ultraviolet (UV) light can degrade the data stored in EEPROM cells. Therefore, customers who use a WLCSP product must ensure that exposure to ultraviolet light does not occur.

- 2. For wafer sales, please contact Atmel Sales.

|      | Package Type                                                                          |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| 8S1  | 8-lead, 0.15" wide, Plastic Gull Wing Small Outline Package (JEDEC SOIC)              |  |  |  |  |  |

| 3TS1 | 3-lead, 1.30mm body, Plastic Thin Shrink Small Outline Package (SOT23)                |  |  |  |  |  |