# LMH0394 3G HD/SD SDI Low Power Extended Reach Adaptive Cable Equalizer

Check for Samples: LMH0394

### **FEATURES**

- SMPTE 424M, SMPTE 292M, SMPTE 344M, SMPTE 259M, and DVB-ASI Compliant

- Equalized Cable Lengths (Belden 1694A):

200m at 2.97 Gbps, 220m at 1.485 Gbps, and

400m at 270 Mbps

- Ultra Low Power Consumption: 115 mW (Normal Operation)

- Power Save Mode with Auto Sleep Control (17 mW Typical Power Consumption in Power Save Mode)

- Designed for Crosstalk Immunity

- Output De-Emphasis to Compensate for FR4 Board Trace Losses

- Digital and Analog Programmable MUTE<sub>REF</sub> Threshold

- Optional SPI Register Access

- Input Data Rates: 125 Mbps to 2.97 Gbps

- Internally Terminated 100Ω LVDS Outputs with Programmable Output Common Mode Voltage and Swing

- Programmable Launch Amplitude Optimization

- Cable Length Indicator

- Single 2.5V Supply Operation

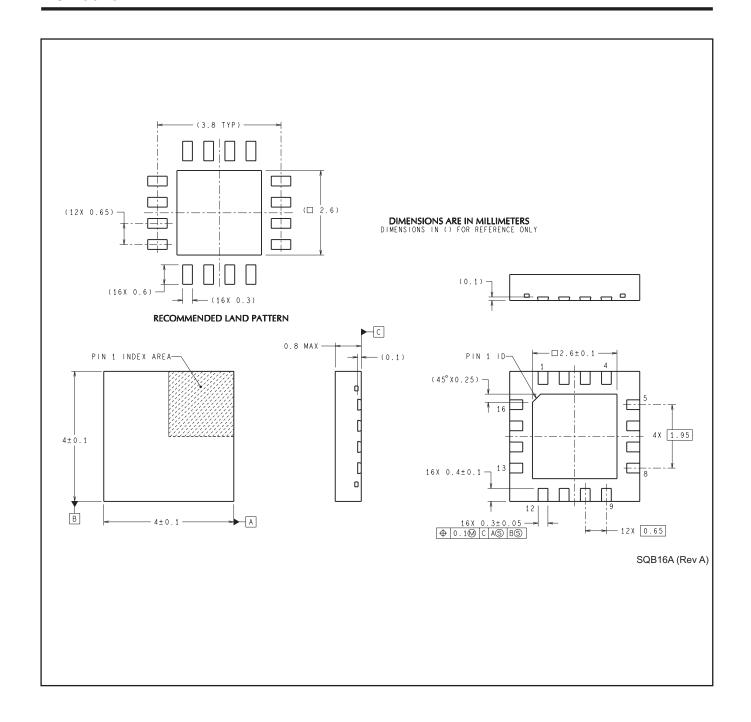

- 16-pin WQFN Package

- Industrial Temperature Range: -40°C to +85°C

- Footprint Compatible with the LMH0384 and also the LMH0344, LMH0044, and LMH0074 in Pin Mode

### **APPLICATIONS**

- SMPTE 424M, SMPTE 292M, SMPTE 344M, and SMPTE 259M Serial Digital Interfaces

- Broadcast Video Routers, Switchers, and Distribution Amplifiers

#### DESCRIPTION

The LMH0394 3 Gbps HD/SD SDI Low Power Extended Reach Adaptive Cable Equalizer is designed to equalize data transmitted over cable (or any media with similar dispersive loss characteristics). The equalizer operates over a wide range of data rates from 125 Mbps to 2.97 Gbps and supports SMPTE 424M, SMPTE 292M, SMPTE 344M, SMPTE 259M, and DVB-ASI standards.

The LMH0394 provides extended cable reach with improved immunity to crosstalk and ultra low power consumption. The equalizer includes active sensing circuitry that ensures robust performance and enhanced immunity to variations in the input signal launch amplitude. The output driver offers programmable de-emphasis for up to 40" of FR4 trace losses. The LMH0394 includes power management to further reduce power consumption when no input signal is present.

The LMH0394 supports two modes of operation. In pin mode, the LMH0394 operates with control pins to set its operating state, and is footprint compatible with the LMH0384, LMH0344, and legacy SDI equalizers. In SPI mode, an optional SPI serial interface can be used to access and configure multiple LMH0394 devices in a daisy-chain configuration. This allows programming the output common mode voltage and swing, output de-emphasis level, input launch amplitude, and power management settings, as well as access to a cable length indicator and all pin mode features.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

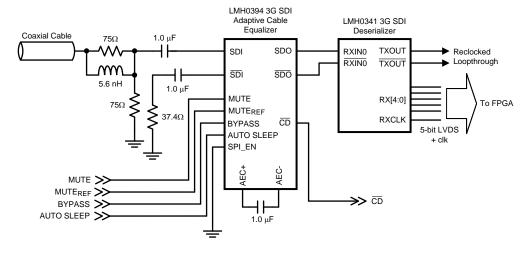

## **Typical Application (Pin Mode)**

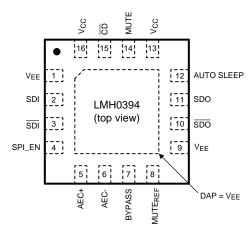

## **Connection Diagram**

Pin Mode (non-SPI) / SPI\_EN = GND / LMH0344 Compatible

The exposed die attach pad is a negative electrical terminal for this device. It should be connected to the negative power supply voltage.

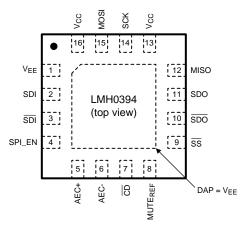

SPI Mode / SPI\_EN = V<sub>CC</sub> 16-Pin WQFN (See Package RUM0016A)

www.ti.com

## Pin Descriptions - Pin Mode (non-SPI) / SPI\_EN = GND / LMH0344 Compatible

| Pin | Name                | I/O, Type   | Description                                                                                                                                                                                                                                                                                      |

|-----|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>EE</sub>     | Ground      | Negative power supply (ground).                                                                                                                                                                                                                                                                  |

| 2   | SDI                 | I, SDI      | Serial data true input.                                                                                                                                                                                                                                                                          |

| 3   | SDI                 | I, SDI      | Serial data complement input.                                                                                                                                                                                                                                                                    |

| 4   | SPI_EN              | I, LVCMOS   | SPI register access enable. This pin has an internal pulldown. H = SPI register access mode. L = Pin mode.                                                                                                                                                                                       |

| 5   | AEC+                | I/O, Analog | AEC loop filter external capacitor (1µF) positive connection (capacitor is optional).                                                                                                                                                                                                            |

| 6   | AEC-                | I/O, Analog | AEC loop filter external capacitor (1µF) negative connection (capacitor is optional).                                                                                                                                                                                                            |

| 7   | BYPASS              | I, LVCMOS   | Equalization bypass. This pin has an internal pulldown.  H = Equalization is bypassed (no equalization occurs).  L = Normal operation.                                                                                                                                                           |

| 8   | MUTE <sub>REF</sub> | I, Analog   | Mute reference input. Sets the threshold for $\overline{\text{CD}}$ and (with $\overline{\text{CD}}$ tied to MUTE) determines the maximum cable to be equalized before muting. MUTE <sub>REF</sub> may be either unconnected or connected to ground for normal $\overline{\text{CD}}$ operation. |

| 9   | V <sub>EE</sub>     | I, LVCMOS   | Connect this pin to ground or drive it logic low.                                                                                                                                                                                                                                                |

| 10  | SDO                 | O, LVDS     | Serial data complement output.                                                                                                                                                                                                                                                                   |

| 11  | SDO                 | O, LVDS     | Serial data true output.                                                                                                                                                                                                                                                                         |

| 12  | AUTO SLEEP          | I, LVCMOS   | Auto Sleep. AUTO SLEEP has precedence over MUTE and BYPASS. This pin has an internal pullup.  H = Device will power down when no input is detected. L = Normal operation (device will not enter auto power down).                                                                                |

| 13  | V <sub>CC</sub>     | Power       | Positive power supply (+2.5V).                                                                                                                                                                                                                                                                   |

| 14  | MUTE                | I, LVCMOS   | Output mute. $\overline{\text{CD}}$ may be tied to this pin to inhibit the output when no input signal is present. MUTE has precedence over BYPASS. This pin has an internal pulldown. H = Outputs forced to a muted state. L = Outputs enabled.                                                 |

| 15  | CD                  | O, LVCMOS   | Carrier detect. H = No input signal detected. L = Input signal detected.                                                                                                                                                                                                                         |

| 16  | V <sub>CC</sub>     | Power       | Positive power supply (+2.5V).                                                                                                                                                                                                                                                                   |

| DAP | V <sub>EE</sub>     | Ground      | Connect exposed DAP to negative power supply (ground).                                                                                                                                                                                                                                           |

## Pin Descriptions - SPI Mode / SPI\_EN = V<sub>CC</sub>

| Pin | Name                | I/O, Type   | Description                                                                                                                                                                                                                                                                                      |

|-----|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>EE</sub>     | Ground      | Negative power supply (ground).                                                                                                                                                                                                                                                                  |

| 2   | SDI                 | I, SDI      | Serial data true input.                                                                                                                                                                                                                                                                          |

| 3   | SDI                 | I, SDI      | Serial data complement input.                                                                                                                                                                                                                                                                    |

| 4   | SPI_EN              | I, LVCMOS   | SPI register access enable. This pin has an internal pulldown. H = SPI register access mode. L = Pin mode.                                                                                                                                                                                       |

| 5   | AEC+                | I/O, Analog | AEC loop filter external capacitor (1µF) positive connection (capacitor is optional).                                                                                                                                                                                                            |

| 6   | AEC-                | I/O, Analog | AEC loop filter external capacitor (1µF) negative connection (capacitor is optional).                                                                                                                                                                                                            |

| 7   | CD                  | O, LVCMOS   | Carrier detect. H = No input signal detected. L = Input signal detected.                                                                                                                                                                                                                         |

| 8   | MUTE <sub>REF</sub> | I, Analog   | Mute reference input. Sets the threshold for $\overline{\text{CD}}$ and (with $\overline{\text{CD}}$ tied to MUTE) determines the maximum cable to be equalized before muting. MUTE <sub>REF</sub> may be either unconnected or connected to ground for normal $\overline{\text{CD}}$ operation. |

| 9   | SS (SPI)            | I, LVCMOS   | SPI slave select. This pin has an internal pullup.                                                                                                                                                                                                                                               |

| 10  | SDO                 | O, LVDS     | Serial data complement output.                                                                                                                                                                                                                                                                   |

| 11  | SDO                 | O, LVDS     | Serial data true output.                                                                                                                                                                                                                                                                         |

| 12  | MISO (SPI)          | O, LVCMOS   | SPI Master Input / Slave Output. LMH0394 control data transmit.                                                                                                                                                                                                                                  |

| 13  | V <sub>CC</sub>     | Power       | Positive power supply (+2.5V).                                                                                                                                                                                                                                                                   |

| 14  | SCK (SPI)           | I, LVCMOS   | SPI serial clock input.                                                                                                                                                                                                                                                                          |

| 15  | MOSI (SPI)          | I, LVCMOS   | SPI Master Output / Slave Input. LMH0394 control data receive. This pin has an internal pulldown.                                                                                                                                                                                                |

| 16  | V <sub>CC</sub>     | Power       | Positive power supply (+2.5V).                                                                                                                                                                                                                                                                   |

| DAP | V <sub>EE</sub>     | Ground      | Connect exposed DAP to negative power supply (ground).                                                                                                                                                                                                                                           |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings(1)

| Supply Voltage             |                                   | 3.1V                           |  |  |

|----------------------------|-----------------------------------|--------------------------------|--|--|

| Input Voltage (all inputs) |                                   | -0.3V to V <sub>CC</sub> +0.3V |  |  |

| Storage Temperature Range  | −65°C to +150°C                   |                                |  |  |

| Junction Temperature       | +125°0                            |                                |  |  |

| Barbara Thomas Baristana   | θ <sub>JA</sub> 16-pin WQFN (RUM) | +40°C/W                        |  |  |

| Package Thermal Resistance | θ <sub>JC</sub> 16-pin WQFN (RUM) | +6°C/W                         |  |  |

| ESD Rating (HBM)           | •                                 | ≥±6 kV                         |  |  |

| ESD Rating (MM)            |                                   | ≥±300V                         |  |  |

| ESD Rating (CDM)           | ≥±2 kV                            |                                |  |  |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" are those parameter values beyond which the life and operation of the device cannot be ensured. The stating herein of these maximums shall not be construed to imply that the device can or should be operated at or beyond these values. The table of "Electrical Characteristics" specifies acceptable device operating conditions.

# **Recommended Operating Conditions**

| Supply Voltage (V <sub>CC</sub> – V <sub>EE</sub> ) | 2.5V ±5%       |

|-----------------------------------------------------|----------------|

| Input Coupling Capacitance                          | 1.0 μF         |

| Operating Free Air Temperature (T <sub>A</sub> )    | -40°C to +85°C |

#### **DC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (1)(2).

| Symbol             | Parameter                                                              | Conditions                                                    | Reference           | Min             | Тур  | Max             | Units             |

|--------------------|------------------------------------------------------------------------|---------------------------------------------------------------|---------------------|-----------------|------|-----------------|-------------------|

| V <sub>IH</sub>    | Input Voltage High Level                                               |                                                               | Lasia lasarta       | 1.7             |      | V <sub>CC</sub> | V                 |

| V <sub>IL</sub>    | Input Voltage Low Level                                                |                                                               | Logic Inputs        | V <sub>EE</sub> |      | 0.7             | V                 |

| V <sub>SDI</sub>   | Input Voltage Swing                                                    | 0m cable length (3)                                           | CDI CDI             | 720             | 800  | 880             | mV <sub>P-P</sub> |

| V <sub>CMIN</sub>  | Input Common Mode Voltage                                              |                                                               | SDI, SDI            |                 | 1.65 |                 | V                 |

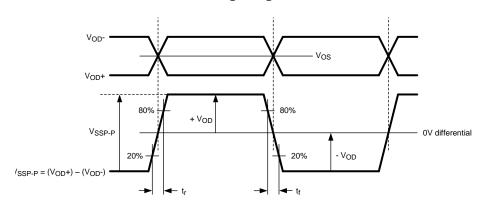

| V <sub>SSP-P</sub> | Differential Output Voltage, P-P                                       |                                                               |                     | 500             | 700  | 900             | $mV_{P-P}$        |

| V <sub>OD</sub>    | Differential Output Voltage                                            |                                                               |                     | 250             | 350  | 450             | mV                |

| $\Delta V_{OD}$    | Change in Magnitude of V <sub>OD</sub> for Complimentary Output States | 100Ω load, default register settings, Figure 1 <sup>(4)</sup> | CDO <u>CDO</u>      |                 |      | 50              | mV                |

| Vos                | Offset Voltage                                                         | Settings, Figure 1                                            | SDO, SDO            | 1.1             | 1.2  | 1.35            | V                 |

| ΔV <sub>OS</sub>   | Change in Magnitude of V <sub>OS</sub> for Complimentary Output States |                                                               |                     |                 |      | 50              | mV                |

| Ios                | Output Short Circuit Current                                           |                                                               |                     |                 |      | 30              | mA                |

|                    | MUTE <sub>REF</sub> DC Voltage (floating)                              |                                                               | MUTE                |                 | 1.3  |                 | V                 |

|                    | MUTE <sub>REF</sub> Range                                              |                                                               | MUTE <sub>REF</sub> |                 | 0.8  |                 | V                 |

| V <sub>OH</sub>    | Output Voltage High Level                                              | I <sub>OH</sub> = -2 mA                                       | CD MICO             | 2.0             |      |                 | V                 |

| V <sub>OL</sub>    | Output Voltage Low Level                                               | I <sub>OL</sub> = +2 mA                                       | CD, MISO            |                 |      | 0.2             | V                 |

| I <sub>CC</sub>    | Supply Current                                                         | Normal operation <sup>(5)</sup>                               |                     |                 | 45   | 65              | mA                |

|                    | Supply Current                                                         | Power save mode                                               |                     |                 | 7    | 10              | mA                |

<sup>(1)</sup> Current flow into device pins is defined as positive. Current flow out of device pins is defined as negative. All voltages are stated referenced to  $V_{EE}=0$  Volts. Typical values are stated for  $V_{CC}=+2.5V$  and  $T_A=+25^{\circ}C$ . The LMH0394 can be optimized for different launch amplitudes via the SPI. The differential output voltage and offset voltage are adjustable via the SPI.

Typical I<sub>CC</sub> is measured with a 2.97 Gbps input signal.

### **AC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (1).

| Symbol            | Parameter                        | Conditions                                                | Reference      | Min | Тур  | Max  | Units |

|-------------------|----------------------------------|-----------------------------------------------------------|----------------|-----|------|------|-------|

| BR <sub>MIN</sub> | Minimum Input Data Rate          |                                                           | CDI CDI        |     | 125  |      | Mbps  |

| BR <sub>MAX</sub> | Maximum Input Data Rate          |                                                           | SDI, SDI       |     |      | 2970 | Mbps  |

|                   |                                  | 2.97 Gbps, Belden 1694A,<br>0-100 meters <sup>(2)</sup>   |                |     |      | 0.2  | UI    |

|                   |                                  | 2.97 Gbps, Belden 1694A,<br>100-140 meters <sup>(2)</sup> |                |     |      | 0.3  | UI    |

|                   |                                  | 2.97 Gbps, Belden 1694A,<br>140-180 meters <sup>(2)</sup> |                |     |      | 0.5  | UI    |

|                   | Jitter for Various Cable Lengths | 2.97 Gbps, Belden 1694A,<br>180-200 meters                |                |     | 0.55 |      | UI    |

|                   |                                  | 1.485 Gbps, Belden 1694A,<br>0-200 meters <sup>(2)</sup>  |                |     |      | 0.2  | UI    |

|                   |                                  | 1.485 Gbps, Belden 1694A,<br>200-220 meters               |                |     | 0.3  |      | UI    |

|                   |                                  | 270 Mbps, Belden 1694A,<br>0-400 meters <sup>(2)</sup>    |                |     |      | 0.3  | UI    |

| $t_r$ , $t_f$     | Output Rise Time, Fall Time      | 20% – 80%, 100Ω load, Figure 1 $^{(3)}$                   |                |     | 90   | 130  | ps    |

|                   | Mismatch in Rise/Fall Time       | See <sup>(3)</sup>                                        | SDO, SDO       |     | 2    | 15   | ps    |

| tos               | Output Overshoot                 | See <sup>(3)</sup>                                        |                |     | 1    | 5    | %     |

| RL <sub>IN</sub>  | Innuit Deturn Leas               | 5 MHz - 1.5 GHz <sup>(4)</sup>                            |                | 15  |      |      | dB    |

|                   | Input Return Loss                | 1.5 GHz - 3.0 GHz <sup>(4)</sup>                          | eni <u>eni</u> | 10  |      |      | dB    |

| R <sub>IN</sub>   | Input Resistance                 | single-ended                                              | SDI, SDI       |     | 1.5  |      | kΩ    |

| C <sub>IN</sub>   | Input Capacitance                | single-ended                                              |                |     | 0.7  |      | pF    |

<sup>(1)</sup> Typical values are stated for  $V_{CC} = +2.5V$  and  $T_A = +25$ °C.

<sup>(2)</sup> Based on design and characterization data over the full range of recommended operating conditions of the device. Jitter is measured in accordance with SMPTE RP 184, SMPTE RP 192, and the applicable serial data transmission standard: SMPTE 424M, SMPTE 292M, or SMPTE 259M.

<sup>(3)</sup> Specification is ensured by characterization.

<sup>(4)</sup> Input return loss is dependent on board design. The LMH0394 exceeds this specification on the SD394 evaluation board with a return loss network consisting of a 5.6 nH inductor in parallel with a 75Ω series resistor on the input.

## **SPI Interface AC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (1).

| Symbol            | Parameter                     | Conditions          | Reference | Min | Тур | Max | Units         |

|-------------------|-------------------------------|---------------------|-----------|-----|-----|-----|---------------|

| Recomm            | ended Input Timing Requireme  | ents                | 1         |     | '   |     | •             |

| f <sub>SCK</sub>  | SCK Frequency                 |                     |           |     |     | 20  | MHz           |

| t <sub>PH</sub>   | SCK Pulse Width High          | Figure 0. Figure 0. | SCK       | 40  |     |     | % SCK period  |

| t <sub>PL</sub>   | SCK Pulse Width Low           | Figure 2, Figure 3  |           | 40  |     |     | % SCK period  |

| t <sub>SU</sub>   | MOSI Setup Time               | Figure 2 Figure 2   | MOCI      | 4   |     |     | ns            |

| t <sub>H</sub>    | MOSI Hold Time                | Figure 2, Figure 3  | MOSI      | 4   |     |     | ns            |

| t <sub>SSSU</sub> | SS Setup Time                 |                     |           | 14  |     |     | ns            |

| t <sub>SSH</sub>  | SS Hold Time                  | Figure 2, Figure 3  | SS        | 4   |     |     | ns            |

| t <sub>SSOF</sub> | SS Off Time                   | rigure 2, rigure 0  | 33        | 1   |     |     | SCK<br>period |

| Switchin          | g Characteristics             | <u>.</u>            |           |     |     |     |               |

| t <sub>ODZ</sub>  | MISO Driven-to-TRI-STATE Time |                     |           |     |     | 20  | ns            |

| t <sub>OZD</sub>  | MISO TRI-STATE-to-Driven Time | Figure 3            | MISO      |     |     | 10  | ns            |

| t <sub>OD</sub>   | MISO Output Delay Time        |                     |           |     |     | 15  | ns            |

(1) Typical values are stated for  $V_{CC}$  = +2.5V and  $T_A$  = +25°C.

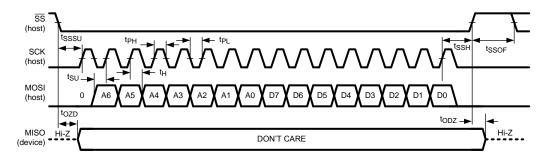

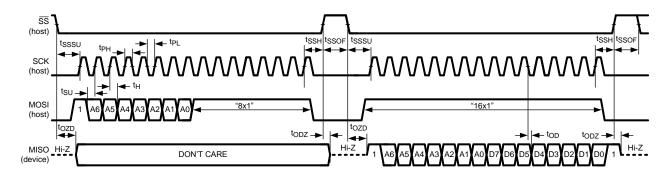

## **Timing Diagrams**

Figure 1. LVDS Output Voltage, Offset, and Timing Parameters

Figure 2. SPI Write

Copyright © 2010–2012, Texas Instruments Incorporated Product Folder Links: LMH0394

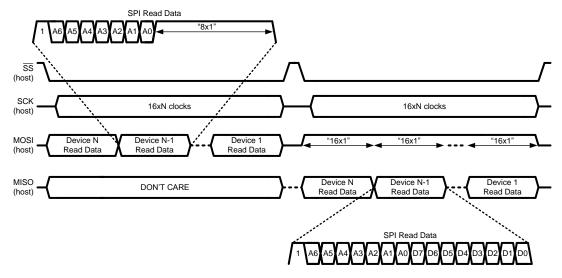

Figure 3. SPI Read

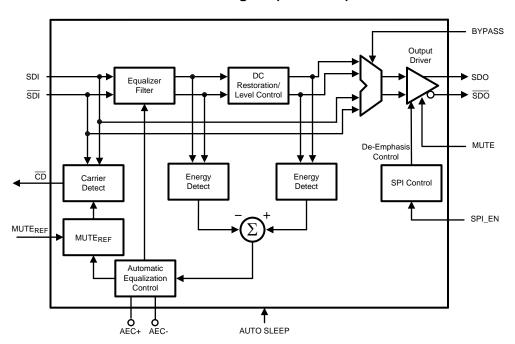

# **Block Diagram(Pin Mode)**

Submit Documentation Feedback

### **Device Operation**

### **BLOCK DESCRIPTION**

The **Equalizer Filter** block is a multi-stage adaptive filter. If Bypass is high, the equalizer filter is disabled.

The **DC Restoration / Level Control** block receives the differential signals from the equalizer filter block. This block incorporates a self-biasing DC restoration circuit to fully DC restore the signals. If Bypass is high, this function is disabled.

The signals before and after the DC Restoration / Level Control block are used to generate the **Automatic Equalization Control (AEC)** signal. This control signal sets the gain and bandwidth of the equalizer filter.

The Carrier Detect block generates the carrier detect signal based on the SDI input and an adjustment from the Mute Reference block.

The **SPI Control** block uses the MOSI, MISO, SCK, and  $\overline{SS}$  signals in SPI mode to control the SPI registers. SPI\_EN selects between SPI mode and pin mode. In pin mode, SPI\_EN is driven logic low.

The **Output Driver** produces SDO and SDO.

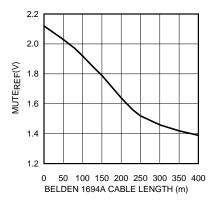

## MUTE REFERENCE (MUTE<sub>REF</sub>)

The mute reference sets the threshold for  $\overline{\text{CD}}$  and (with  $\overline{\text{CD}}$  tied to MUTE) determines the amount of cable to equalize before automatically muting the outputs. This is set by applying a voltage inversely proportional to the length of cable to equalize. The applied voltage must be greater than the MUTE<sub>REF</sub> floating voltage (typically 1.3V) in order to change the  $\overline{\text{CD}}$  threshold. As the applied MUTE<sub>REF</sub> voltage is increased, the amount of cable that can be equalized before carrier detect is de-asserted and the outputs are muted is decreased. MUTE<sub>REF</sub> may be left unconnected or connected to ground for normal  $\overline{\text{CD}}$  operation. Optionally, the LMH0394 allows the mute reference to be set digitally via SPI register 03h.

Figure 4 shows the minimum MUTE<sub>REF</sub> input voltage required to force carrier detect to inactive vs. Belden 1694A cable length. The results shown are valid for Belden 1694A cable lengths of 0-200m at 2.97 Gbps, 0-220m at 1.485 Gbps, and 0-400m at 270 Mbps.

Figure 4. MUTE<sub>REF</sub> vs. Belden 1694A Cable Length

# CARRIER DETECT (CD) AND MUTE

Carrier detect  $\overline{\text{CD}}$  indicates if a valid signal is present at the LMH0394 input. This signal is logical OR operation of the internal energy detector and MUTE<sub>REF</sub> setting (if used). The internal energy detector detects energy across different data rates. If MUTE<sub>REF</sub> is used, the carrier detect threshold will be altered accordingly.  $\overline{\text{CD}}$  provides a high voltage when no signal is present at the LMH0394 input.  $\overline{\text{CD}}$  is low when a valid input signal is detected.

MUTE can be used to manually mute or enable SDO and SDO. Applying a high input to MUTE will mute the LMH0394 outputs by forcing the output to a logic 1. Applying a low input will force the outputs to be active.

In pin mode,  $\overline{\text{CD}}$  and MUTE may be tied together to automatically mute the output when no input signal is present.

#### **AUTO SLEEP**

The auto sleep mode allows the LMH0394 to power down when no input signal is detected. If the AUTO SLEEP pin is set high, the LMH0394 goes into a deep power save mode when no signal is detected. The device powers on again once an input signal is detected. The auto sleep functionality can be turned off by setting AUTO SLEEP low or tying this pin to ground. An additional auto sleep setting available in SPI mode can be used to force the equalizer to power down regardless of whether there is an input signal or not. Auto sleep has precedence over mute and bypass modes.

In auto sleep mode, the time to power down the equalizer when the input signal is removed is less than 200 µs and should not have any impact on the system timing requirements. The device will wake up automatically once an input signal is detected, and the delay between signal detection and full functionality of the equalizer is negligible (about 5 ms). The overall system will be limited only by the settling time constant of the equalizer adaptation loop.

#### INPUT INTERFACING

The LMH0394 accepts either differential or single-ended input. The input must be AC coupled. The Typical Application (Pin Mode) diagram on the front page shows the typical configuration for a single-ended input. The unused input must be properly terminated as shown.

The LMH0394 can be optimized for different launch amplitudes via the SPI (see LAUNCH AMPLITUDE OPTIMIZATION in the SPI Register Access section).

The LMH0394 correctly handles equalizer pathological signals for standard definition and high definition serial digital video, as described in SMPTE RP 178 and RP 198, respectively.

### **OUTPUT INTERFACING**

SDO and  $\overline{\text{SDO}}$  together are internally terminated 100 $\Omega$  LVDS outputs. These outputs can be DC coupled to most common differential receivers.

The default output common mode voltage ( $V_{OS}$ ) is 1.2V. The output common mode voltage may be adjusted via the SPI in 200 mV increments, from 0.8V to 1.2V (see OUTPUT DRIVER ADJUSTMENTS AND DE-EMPHASIS SETTING in the SPI Register Access section). When the output common mode is supply referenced, the common mode voltage is about 1.35V (for 700 mV<sub>P-P</sub> differential swing). This adjustable output common mode voltage offers flexibility for interfacing to many types of receivers.

The default differential output swing ( $V_{SSP-P}$ ) is 700 m $V_{P-P}$ . The differential output swing may be adjusted via the SPI. Valid options are 400, 600, 700, or 800 m $V_{P-P}$  (see OUTPUT DRIVER ADJUSTMENTS AND DE-EMPHASIS SETTING in the SPI Register Access section).

The LMH0394 output should be DC coupled to the input of the receiving device where possible.  $100\Omega$  differential transmission lines should be used to connect between the LMH0394 outputs and the input of the receiving device.

The LMH0394 output should not be DC coupled to CML inputs. If there are strong pullup resistors (i.e.  $50\Omega$ ) at the receiving device, AC coupling should be used. The value of these AC-coupling capacitors should be large enough (typically 4.7  $\mu$ F) to accommodate for the SD pathological video pattern.

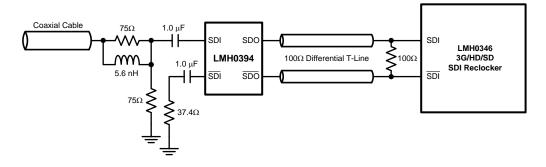

Figure 5 shows an example of a DC-coupled interface between the LMH0394 and LMH0346 SDI reclocker. The differential transmission line should be terminated with a  $100\Omega$  resistor at the receiving device as shown. The resistor should be placed as close as possible to the LMH0346 input. If desired, this network may be terminated with two  $50\Omega$  resistors and a center-tap capacitor to ground in place of the single  $100\Omega$  resistor.

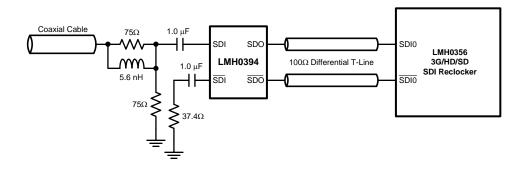

Figure 6 shows an example of a DC-coupled interface between the LMH0394 and LMH0356 SDI reclocker. The LMH0356 inputs have internal  $50\Omega$  terminations ( $100\Omega$  differential) to terminate the transmission line, so no additional components are required.

The LMH0394 output driver is equipped with programmable output de-emphasis to minimize inter-symbol interference caused by the loss dispersion from driving signals across PCB traces (see OUTPUT DRIVER ADJUSTMENTS AND DE-EMPHASIS SETTING in the SPI Register Access section). De-emphasis works with all combinations of output common mode voltage and output voltage swing settings to support DC coupling to the receiving device.

Figure 5. DC Output Interface to LMH0346 Reclocker

Figure 6. DC Output Interface to LMH0356 Reclocker

## **SPI Register Access**

Setting SPI\_EN high enables the optional SPI register access mode. In SPI mode, the LMH0394 provides register access to all of its features along with a cable length indicator, programmable output de-emphasis, programmable output common mode voltage and swing, digital MUTE<sub>REF</sub>, and launch amplitude optimization. There are eight supported 8-bit registers in the device (see Table 1). The LMH0394 supports SPI daisy-chaining among an unlimited number of LMH0394 devices. With SPI\_EN set low, the device operates in pin mode and is footprint compatible with the LMH0384, LMH0344, LMH0044, and LMH0074.

#### **SPI Transaction Overview**

Each SPI transaction to a single device is 16-bits long. The transaction is initiated by driving  $\overline{SS}$  low, and completed by returning  $\overline{SS}$  high. The 16-bit MOSI payload consists of the read/write command ("1" for reads and "0" for writes), the seven address bits of the device register (MSB first), and the eight data bits (MSB first). The LMH0394 MOSI input data is latched on the rising edge of SCK, and the MISO output data is sourced on the falling edge of SCK.

In order to facilitate daisy-chaining, the prior SPI command, address, and data are shifted out on the MISO output as the current command, address, and data are shifted in on the MOSI input. For SPI writes, the MISO output is typically ignored as "Don't Care" data. For SPI reads, the MISO output provides the requested read data (after 16 periods of SCK). The MISO output is active when SS low, and tri-stated when SS is high.

#### **SPI Write**

The SPI write is shown in Figure 2. The SPI write is 16 bits long. The 16-bit MOSI payload consists of a "0" (write command), seven address bits, and eight data bits. The  $\overline{SS}$  signal is driven low, and the 16 bits are sent to the LMH0394's MOSI input. After the SPI write,  $\overline{SS}$  must return high. The prior SPI command, address, and data shifted out on the MISO output during the SPI write is shown as "Don't Care" on the MISO output in Figure 2.

#### **SPI Read**

The SPI read is shown in Figure 3. The SPI read is 32 bits long, consisting of a 16-bit read transaction followed by a 16-bit dummy read transaction to shift out the read data on the MISO output. The first 16-bit MOSI payload consists of a "1" (read command), seven address bits, and eight "1"s which are ignored. The second 16-bit MOSI payload consists of 16 "1"s which are ignored but necessary in order to shift out the requested read data on the MISO output. The \$\overline{SS}\$ signal is driven low, and the first 16 bits are sent to the LMH0394's MOSI input. The prior SPI command, address, and data are shifted out on the MISO output during the first 16-bit transaction, and are typically ignored (this is shown as "Don't Care" on the MISO output in Figure 3. \$\overline{SS}\$ must return high and then is driven low again before the second 16 bits (all "1"s) are sent to the LMH0394's MOSI input. Once again, the prior SPI command, address, and data are shifted out on the MISO output, but this data now includes the requested read data. The read data is available on the MISO output during the second 8 bits of the 16-bit dummy read transaction, as shown by D7-D0 in Figure 3.

#### **SPI Daisy-Chain Operation**

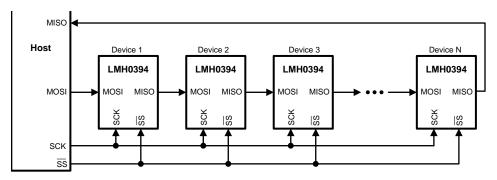

The LMH0394 SPI controller supports daisy-chaining the serial data between an unlimited number of LMH0394 devices. Each LMH0394 device is directly connected to the SCK and SS pins on the host. However, only the first LMH0394 device in the chain is connected to the host's MOSI pin, and only the last device in the chain is connected to the host's MISO pin. The MISO pin of each intermediate LMH0394 device in the chain is connected to the MOSI pin of the next LMH0394 device, creating a serial shift register. This daisy-chain architecture is shown in Figure 7.

Figure 7. SPI Daisy Chain System Architecture

In a daisy-chain configuration of N LMH0394 devices, the host conceptually sees a shift register of length 16xN. Therefore the length of SPI transactions (as previously described) is 16xN bits, and  $\overline{SS}$  must be asserted for 16xN clock cycles for each SPI transaction.

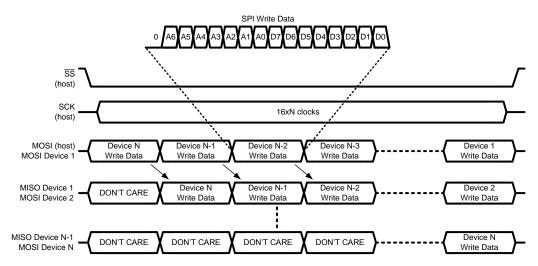

#### **SPI Daisy-Chain Write**

Figure 8 shows the SPI daisy-chain write for a daisy-chain of N devices. The  $\overline{SS}$  signal is driven low and SCK is toggled for 16xN clocks. The 16xN bit MOSI payload (sent to Device 1 in the daisy-chain) consists of the 16-bit SPI write data for Device N (the last device in the chain), followed by the write data for Device N-1, Device N-2, etc., ending with the write data for Device 1 (the first device in the chain). The 16-bit SPI write data for each device consists of a "0" (write command), seven address bits, and eight data bits. After the SPI daisy-chain write,  $\overline{SS}$  must return high and then the write occurs for all devices in the daisy-chain.

Figure 8. SPI Daisy-Chain Write

### **SPI Daisy-Chain Read**

Figure 9 shows the SPI daisy-chain read for a daisy-chain of N devices. The SPI daisy-chain read is 32xN bits long, consisting of 16xN bits for the read transaction followed by 16xN bits for the dummy read transaction (all "1"s) to shift out the read data on the MISO output. The SS signal is driven low and SCK is toggled for 16xN clocks. The first 16xN bit MOSI payload (sent to Device 1 in the daisy-chain) consists of the 16-bit SPI read data for Device N (the last device in the chain), followed by the read data for Device N-1, Device N-2, etc., ending with the read data for Device 1 (the first device in the chain). The 16-bit SPI read data for each device consists of a "1" (read command), seven address bits, and eight "1"s (which are ignored). After the first 16xN bit transaction, SS must return high (to latch the data) and then is driven low again before the second 16xN bit transaction of all "1"s is sent to the MOSI input. The requested read data is shifted out on MISO starting with the data for Device N and ending with the data for Device 1. After this transaction, SS must return high.

Figure 9. SPI Daisy-Chain Read

Submit Documentation Feedback

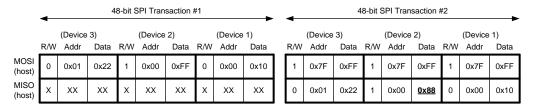

### SPI Daisy-Chain Read and Write Example

The following example further clarifies LMH0394 SPI daisy-chain operation. Assume a daisy-chain of three LMH0394 devices (Device 1, Device 2, and Device 3), with Device 1 as the first device in the chain and Device 3 as the last device in the chain, as shown by the first three devices in Figure 7. Since there are three devices in the daisy-chain, each SPI transaction is 48-bits long.

This example shows an SPI operation combining SPI reads and writes in order to accomplish the following three tasks:

- 1. Write 0x22 to register 0x01 of Device 1 in order to set the output swing to 400 mV<sub>P-P</sub>.

- 2. Read the contents of register 0x00 of Device 2.

- 3. Write 0x10 to register 0x00 of Device 3 in order to force the sleep mode.

Figure 10 shows the two 48-bit SPI transactions required to complete these tasks (the bits are shifted in left to right).

Figure 10. SPI Daisy-Chain Read and Write Example

The following occurs at the end of the first transaction:

- 1. Write 0x22 to register 0x01 of Device 1.

- 2. Latch the data from register 0x00 of Device 2.

- 3. Write 0x10 to register 0x00 of Device 3.

In the second transaction, three dummy reads (each consisting of 16 "1"s) are shifted in, and the read data from Device 2 (with value 0x88) appears on MISO in the 25th through 32nd clock cycles.

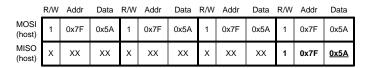

#### **SPI Daisy-Chain Length Detection**

A useful operation for the host may be to detect the length of the daisy-chain. This is a simple matter of shifting in a series of dummy reads with a known data value (such as 0x5A). For an SPI daisy-chain of N LMH0394 devices, the known data value will appear on the host's MISO pin after N+1 writes. Assuming a daisy-chain of three LMH0394 devices, the result of this operation is shown in Figure 11.

Figure 11. SPI Daisy-Chain Length Detection

### **OUTPUT DRIVER ADJUSTMENTS AND DE-EMPHASIS SETTING**

The output driver swing (amplitude), offset voltage (common mode voltage), and de-emphasis level are adjustable via SPI register 01h.

The output swing is adjustable via bits [7:6] of SPI register 01h. The default value for these register bits is "10" for a peak to peak differential output voltage of 700 mV<sub>P-P</sub>. The output swing can be set for 400 mV<sub>P-P</sub>, 600 mV<sub>P-P</sub>,  $_{P}$ , 700 mV<sub>P-P</sub>, or 800 mV<sub>P-P</sub>.

The offset voltage is adjustable via bits [5:4] of SPI register 01h. The default value for these register bits is "10" for an output offset of 1.2V. The output common mode voltage may be adjusted in 200 mV increments, from 0.8V to 1.2V. It can be set to "11" for the maximum offset voltage. At this maximum offset voltage setting, the outputs are referenced to the positive supply and the offset voltage is around 1.35V.

The output de-emphasis is turned on or off by bit 3 of SPI register 01h, and the de-emphasis level is set by bits [2:1] of SPI register 01h. The output de-emphasis level may be set for 0 dB (for driving up to 10" FR4), 3 dB (for driving 10-20" FR4), 5 dB (for driving 20-30" FR4), or 7 dB (for driving 30-40" FR4).

#### LAUNCH AMPLITUDE OPTIMIZATION

The LMH0394 can compensate for attenuation of the input signal prior to the equalizer. This compensation is useful for applications with a passive splitter at the equalizer input or a non-ideal input termination network, and is controlled by SPI register 02h.

Bit 7 of SPI register 02h is used for the launch amplitude setting. At the default setting of "0", the LMH0394 operates normally and expects a launch amplitude of 800 mV<sub>P-P</sub>. Bit 7 may be set to "1" to optimize the LMH0394 for input signals with 6 dB of attenuation (400 mV<sub>P-P</sub>).

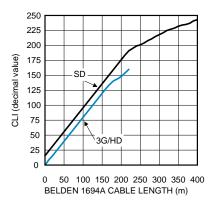

### **CABLE LENGTH INDICATOR (CLI)**

The cable length indicator (CLI) provides an indication of the length of the cable attached to input. CLI is accessible via bits [7:0] of SPI register 06h. The 8-bit setting ranges in decimal value from 0 to 247 ("00000000" to "11110111" binary), corresponding to 0 to 400m of Belden 1694A cable. For 3G and HD input, CLI is 1.25m per step. For SD input, CLI is 1.25m per step, less 20m, from 0 to 191 decimal, and 3.5m per step from 192 to 247 decimal.

To calculate the Belden 1694A cable length (in meters) from the CLI decimal value for 3G or HD input:

To calculate the Belden 1694A cable length (in meters) from the CLI decimal value for SD input:

For CLI≤191.

Cable Length =  $(CLI \times 1.25) - 20$

For CLI > 191.

Cable Length =

$$((191 \times 1.25) - 20) + ((CLI - 191) \times 3.5)$$

(2)

Figure 12 shows typical CLI values vs. Belden 1694A cable length. CLI is valid for Belden 1694A cable lengths of 0-200m at 2.97 Gbps, 0-220m at 1.485 Gbps, and 0-400m at 270 Mbps. Note: Given the continuous adaptive nature of the equalizer, this setting changes by some steps constantly.

Figure 12. CLI vs. Belden 1694A Cable Length

#### APPLICATION INFORMATION

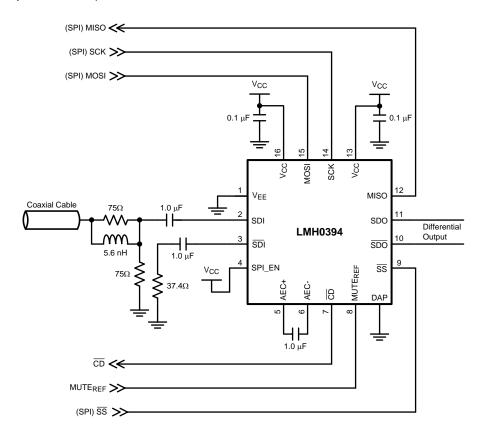

### **APPLICATION CIRCUIT (SPI MODE)**

Figure 13 shows the application circuit for the LMH0394 in SPI mode. (Note: The application circuit shows an external capacitor connected between the AEC+ and AEC- pins as commonly configured in legacy equalizers. This capacitor is optional and not necessary for the LMH0394; the AEC+ and AEC- pins may be left unconnected with no change in performance.)

Figure 13. Application Circuit (SPI Mode)

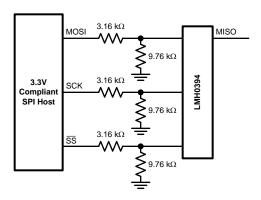

#### **INTERFACING TO 3.3V SPI**

The LMH0394 may be controlled via optional SPI register access. The LMH0394 SPI pins support 2.5V LVCMOS logic levels and are compliant with JEDEC JESD8-5 (see DC Electrical Characteristics). Care must be taken when interfacing the SPI pins to other voltage levels.

The 2.5V LMH0394 SPI pins may be interfaced to a 3.3V compliant SPI host by using a voltage divider or level translator. One implementation is a simple resistive voltage divider as shown in Figure 14.

Figure 14. 3.3V SPI Interfacing

#### **CROSSTALK IMMUNITY**

Single-ended SDI signals are susceptible to crosstalk and good design practices should be employed to minimize its effects. Most crosstalk originates through capacitive coupling from adjacent signals routed closely together via traces and connectors. To reduce capacitive coupling, SDI signals should be appropriately spaced apart or insulated from one another. This can be accomplished by physically isolating signal traces in the layout and by providing additional ground pins between signal traces in connectors as necessary. These techniques help to reduce crosstalk but do not eliminate it.

The LMH0394 was designed specifically with crosstalk in mind and incorporates advanced circuit design techniques that help to isolate and minimize the effects of cross-coupling in high-density system designs. Lab evaluations and customer testimonials have shown other adaptive cable equalizers are much more susceptible to crosstalk, resulting in significant cable reach degradation. The LMH0394's enhanced design results in minimal degradation in cable reach in the presence of crosstalk and overall superior immunity against cross-coupling from neighboring channels.

### **PCB LAYOUT RECOMMENDATIONS**

For information on layout and soldering of the WQFN package, pease refer to the following application note: *AN-1187 Leadless Leadframe Package (LLP) Application Report* (literature number SNOA401).

The SMPTE 424M, 292M, and 259M standards have stringent requirements for the input return loss of receivers, which essentially specify how closely the input must resemble a  $75\Omega$  network. Any non-idealities in the network between the BNC and the equalizer will degrade the input return loss. Care must be taken to minimize impedance discontinuities between the BNC and the equalizer to ensure that the characteristic impedance of this trace is  $75\Omega$ . Please consider the following PCB recommendations:

- Use surface mount components, and use the smallest components available. In addition, use the smallest size component pads.

- Select trace widths that minimize the impedance mismatch between the BNC and the equalizer.

- Select a board stack up that supports both  $75\Omega$  single-ended traces and  $100\Omega$  loosely-coupled differential traces.

- Place return loss components closest to the equalizer input pins.

- Maintain symmetry on the complimentary signals.

- Route 100Ω traces uniformly (keep trace widths and trace spacing uniform along the trace).

- Avoid sharp bends in the signal path; use 45° or radial bends.

- Place bypass capacitors close to each power pin, and use the shortest path to connect equalizer power and ground pins to the respective power or ground planes.

- Remove ground plane under input/output components to minimize parasitic capacitance.

# **SPI Registers**

# Table 1. SPI Registers

| Address | R/W | Name            | Bits | Field                          | Default | Description                                                                                                                                                                                                                                                                                           |

|---------|-----|-----------------|------|--------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h     | R/W | General Control | 7    | Carrier Detect                 |         | Read only. 0: No carrier detected. 1: Carrier detected.                                                                                                                                                                                                                                               |

|         |     |                 | 6    | Mute                           | 0       | Mute has precedence over Bypass. 0: Normal operation. 1: Outputs muted.                                                                                                                                                                                                                               |

|         |     |                 | 5    | Bypass                         | 0       | Normal operation.     Equalizer bypassed.                                                                                                                                                                                                                                                             |

|         |     |                 | 4:3  | Sleep Mode                     | 01      | Sleep mode control. Sleep has precedence over Mute and Bypass. 00: Disable sleep mode (force equalizer to stay enabled). 01: Sleep mode active when no input signal detected. 10: Force equalizer into sleep mode (powered down) regardless of whether there is an input signal or not. 11: Reserved. |

|         |     |                 | 2    | Reserved                       | 0       | Reserved as 0. Always write 0 to this bit.                                                                                                                                                                                                                                                            |

|         |     |                 | 1    | Master Reset                   | 0       | Reset registers and state machine. (This bit is self-clearing.) 0: Normal operation. 1: Reset registers and state machine.                                                                                                                                                                            |

|         |     |                 | 0    | Acquisition Reset              | 0       | Reset state machine. (This bit is self-clearing.) 0: Normal operation. 1: Reset state machine.                                                                                                                                                                                                        |

| 01h     | R/W | Output Driver   | 7:6  | Output Swing                   | 10      | Output driver swing (V <sub>SSP-P</sub> ). 00: V <sub>SSP-P</sub> = 400 mV <sub>P-P</sub> . 01: V <sub>SSP-P</sub> = 600 mV <sub>P-P</sub> . 10: V <sub>SSP-P</sub> = 700 mV <sub>P-P</sub> . 11: V <sub>SSP-P</sub> = 800 mV <sub>P-P</sub> .                                                        |

|         |     |                 | 5:4  | Offset Voltage                 | 10      | Output driver offset voltage (common mode voltage).  00: V <sub>OS</sub> = 0.8V.  01: V <sub>OS</sub> = 1.0V.  10: V <sub>OS</sub> = 1.2V.  11: V <sub>OS</sub> referenced to positive supply.                                                                                                        |

|         |     |                 | 3    | De-Emphasis                    | 0       | Output driver de-emphasis control. 0: De-emphasis disabled. 1: De-emphasis enabled.                                                                                                                                                                                                                   |

|         |     |                 | 2:1  | De-Emphasis Amplitude<br>Level | 01      | Output driver de-emphasis level. 00: 0 dB (no de-emphasis). 01: 3 dB de-emphasis. 10: 5 dB de-emphasis. 11: 7 dB de-emphasis.                                                                                                                                                                         |

|         |     |                 | 0    | Reserved                       | 0       | Reserved (read only).                                                                                                                                                                                                                                                                                 |

# Table 1. SPI Registers (continued)

| 02h | D/M |                                |     |                                     |         | Description                                                                                                                                                                                                               |

|-----|-----|--------------------------------|-----|-------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | R/W | Launch Amplitude<br>Control    | 7   | Launch Amplitude Control            | 0       | Launch amplitude optimization setting. 0: Normal optimization with no external attenuation (800 mV <sub>P-P</sub> launch amplitude). 1: Optimized for 6 dB external attenuation (400 mV <sub>P-P</sub> launch amplitude). |

|     |     |                                | 6:0 | Reserved                            | 1101000 | Reserved as 1101000. Always write 1101000 to these bits.                                                                                                                                                                  |

| 03h | R/W | MUTE <sub>REF</sub>            | 7:6 | Reserved                            | 00      | Reserved as 00. Always write 00 to these bits.                                                                                                                                                                            |

|     |     |                                | 5   | MUTE <sub>REF</sub> Mode            | 0       | 0: Use MUTE <sub>REF</sub> pin.<br>1: Use digital MUTE <sub>REF</sub> .                                                                                                                                                   |

|     |     |                                | 4:0 | Digital MUTE <sub>REF</sub> Setting | 11111   | Digital MUTE <sub>REF</sub> (10m per step). 00000: Mute when cable (EQ boost) ≥ 10m 01111: Mute when cable (EQ boost) ≥ 160m 11111: Never mute.                                                                           |

| 04h | R   | Device ID                      | 7:6 | Reserved                            | 00      | Reserved.                                                                                                                                                                                                                 |

|     |     |                                | 5:4 | EQ ID                               | 01      | 00: LMH0384 device.<br>01: LMH0394 device.<br>10: LMH0395 device.<br>11: Reserved.                                                                                                                                        |

|     |     |                                | 3:0 | Die Revision                        | 0011    | Die revision.                                                                                                                                                                                                             |

| 05h | R   | Rate Indicator                 | 7:6 | Reserved                            | 00      | Reserved.                                                                                                                                                                                                                 |

|     |     |                                | 5   | Rate Indicator                      |         | 0: SD.<br>1: 3G/HD.                                                                                                                                                                                                       |

|     |     |                                | 4:0 | Reserved                            | 11000   | Reserved.                                                                                                                                                                                                                 |

| 06h | R   | Cable Length Indicator         | 7:0 | Cable Length Indicator              |         | Cable Length Indicator (CLI), with 10% accuracy. 00000000: Short cable 11110111: Maximum cable. 11111000: Reserved 11111111: Reserved.                                                                                    |

| 07h | R   | Launch Amplitude<br>Indication | 7:2 | Launch Amplitude Indication         |         | Indication of launch amplitude: 1% or 0.08 dB per step with 5% accuracy. 000000: Nominal -32% 011111: Nominal -1%. 100000: Nominal. 100001: Nominal +1% 111111: Nominal +31%. Reserved.                                   |

## PACKAGE OPTION ADDENDUM

24-.lan-2013

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type | Package | Pins | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|-------------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      |             | (2)                        |                  | (3)                 |              | (4)               |         |

| LMH0394SQ/NOPB   | ACTIVE | WQFN         | RUM     | 16   | 1000        | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR | -40 to 85    | L0394             | Samples |

| LMH0394SQE/NOPB  | ACTIVE | WQFN         | RUM     | 16   | 250         | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR | -40 to 85    | L0394             | Samples |

| LMH0394SQX/NOPB  | ACTIVE | WQFN         | RUM     | 16   | 4500        | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR | -40 to 85    | L0394             | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 26-Mar-2013

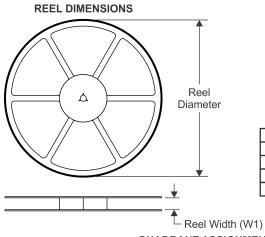

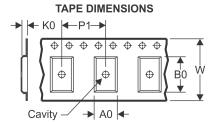

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

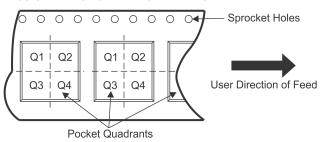

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMH0394SQ/NOPB  | WQFN            | RUM                | 16 | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LMH0394SQE/NOPB | WQFN            | RUM                | 16 | 250  | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LMH0394SQX/NOPB | WQFN            | RUM                | 16 | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 26-Mar-2013

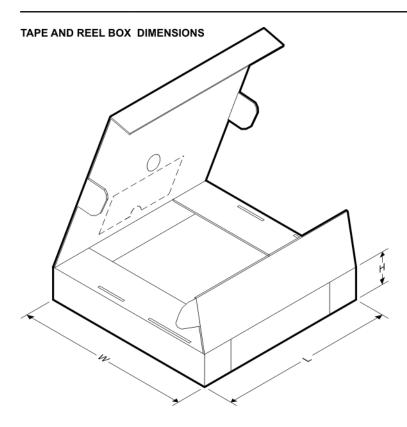

#### \*All dimensions are nominal

| 7 till dillitorionorio di o mominidi |              |                 |      |      |             |            |             |

|--------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                               | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| LMH0394SQ/NOPB                       | WQFN         | RUM             | 16   | 1000 | 213.0       | 191.0      | 55.0        |

| LMH0394SQE/NOPB                      | WQFN         | RUM             | 16   | 250  | 213.0       | 191.0      | 55.0        |

| LMH0394SQX/NOPB                      | WQFN         | RUM             | 16   | 4500 | 367.0       | 367.0      | 35.0        |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

Мы молодая и активно развивающаяся компания в области поставок электронных компонентов. Мы поставляем электронные компоненты отечественного и импортного производства напрямую от производителей и с крупнейших складов мира.

Благодаря сотрудничеству с мировыми поставщиками мы осуществляем комплексные и плановые поставки широчайшего спектра электронных компонентов.

Собственная эффективная логистика и склад в обеспечивает надежную поставку продукции в точно указанные сроки по всей России.

Мы осуществляем техническую поддержку нашим клиентам и предпродажную проверку качества продукции. На все поставляемые продукты мы предоставляем гарантию.

Осуществляем поставки продукции под контролем ВП МО РФ на предприятия военно-промышленного комплекса России, а также работаем в рамках 275 ФЗ с открытием отдельных счетов в уполномоченном банке. Система менеджмента качества компании соответствует требованиям ГОСТ ISO 9001.

Минимальные сроки поставки, гибкие цены, неограниченный ассортимент и индивидуальный подход к клиентам являются основой для выстраивания долгосрочного и эффективного сотрудничества с предприятиями радиоэлектронной промышленности, предприятиями ВПК и научноисследовательскими институтами России.

С нами вы становитесь еще успешнее!

#### Наши контакты:

Телефон: +7 812 627 14 35

Электронная почта: sales@st-electron.ru

Адрес: 198099, Санкт-Петербург,

Промышленная ул, дом № 19, литера Н,

помещение 100-Н Офис 331