# Mixed-Signal Front-End (MxFE™) Processor for Broadband Communications

# AD9860/AD9862\*

#### **FEATURES**

Mixed-Signal Front-End Processor with Dual Converter Receive and Dual Converter Transmit Signal Paths Receive Signal Path Includes:

Two 10-/12-Bit, 64 MSPS Sampling A/D Converters with Internal or External Independent References, Input Buffers, Programmable Gain Amplifiers, Low-Pass Decimation Filters, and a Digital Hilbert Filter Transmit Signal Path Includes:

Two 12-/14-Bit, 128 MSPS D/A Converters with Programmable Full-Scale Output Current, Channel Independent Fine Gain and Offset Control, Digital Hilbert and Interpolation Filters, and Digitally Tunable Real or Complex Up-Converters

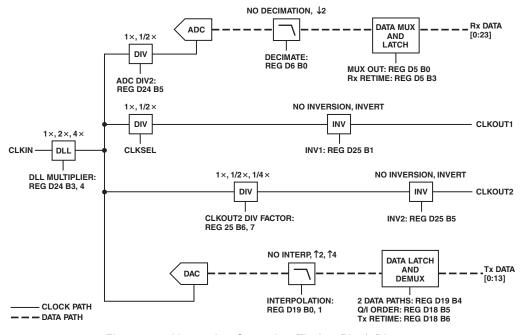

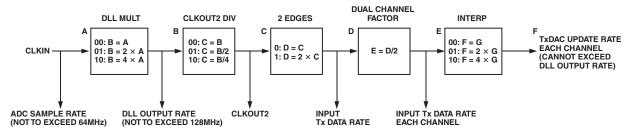

Delay-Locked Loop Clock Multiplier and Integrated Timing Generation Circuitry Allow for Single Crystal or Clock Operation

Programmable Output Clocks, Serial Programmable Interface, Programmable Sigma-Delta, Three Auxiliary DAC Outputs and Two Auxiliary ADCs with Dual Multiplexed Inputs

#### **APPLICATIONS**

Broadband Wireless Systems Fixed Wireless, WLAN, MMDS, LMDS Broadband Wireline Systems Cable Modems, VDSL, PowerPlug Digital Communications Set-Top Boxes, Data Modems

#### **GENERAL DESCRIPTION**

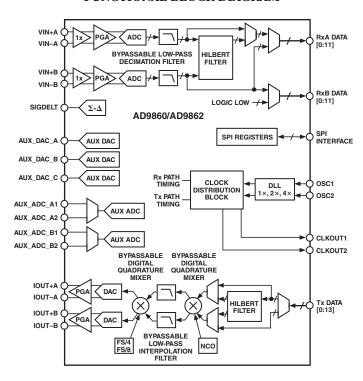

The AD9860 and AD9862 (AD9860/AD9862) are versatile integrated mixed-signal front-ends (MxFE) that are optimized for broadband communication markets. The AD9860/AD9862 are cost effective, mixed signal solutions for wireless or wireline standards based or proprietary broadband modem systems where dynamic performance, power dissipation, cost, and size are all critical attributes. The AD9860 has 10-bit ADCs and 12-bit DACs; the AD9862 has 12-bit ADCs and 14-bit DACs.

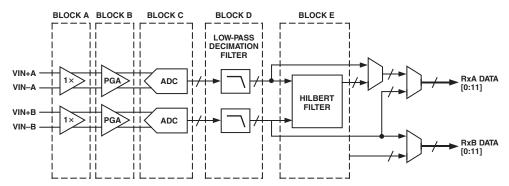

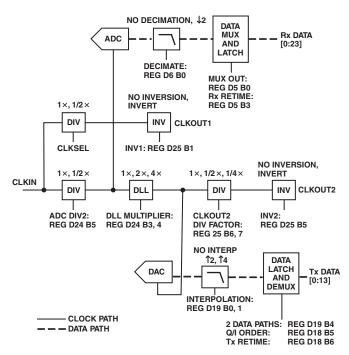

The AD9860/AD9862 receive path (Rx) consists of two channels that each include a high performance, 10-/12-bit, 64 MSPS analog-to-digital converter (ADC), input buffer, Programmable Gain Amplifier (RxPGA), digital Hilbert filter, and decimation filter. The Rx can be used to receive real, diversity, or I/Q data at baseband or low IF. The input buffers provide a constant input impedance for both channels to ease impedance matching with external components (e.g., SAW filter). The RxPGA provides a 20 dB gain

\*Protected by U.S.Patent No. 5,969,657. MxFE is a trademark of Analog Devices, Inc.

#### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### FUNCTIONAL BLOCK DIAGRAM

range for both channels. The output data bus can be multiplexed to accommodate a variety of interface types.

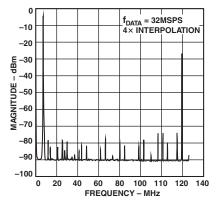

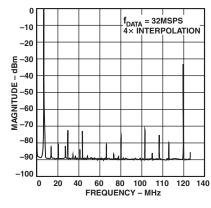

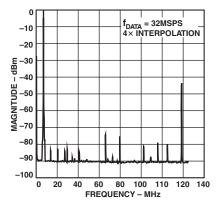

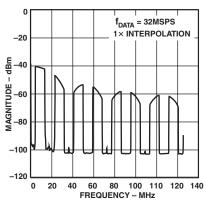

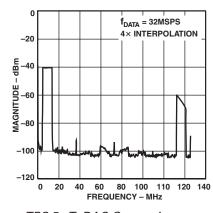

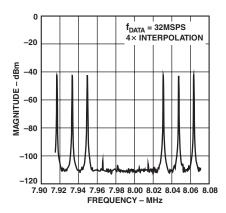

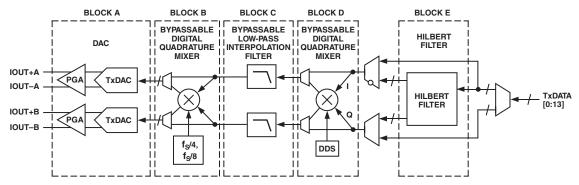

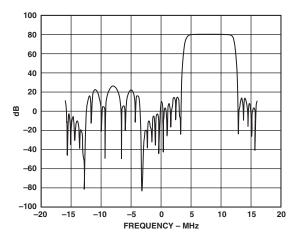

The AD9860/AD9862 transmit path (Tx) consists of two channels that contain high performance, 12-/14-bit, 128 MSPS digital-to-analog converters (DAC), programmable gain amplifiers (TxPGA), interpolation filters, a Hilbert filter, and digital mixers for complex or real signal frequency modulation. The Tx latch and demultiplexer circuitry can process real or I/Q data. Interpolation rates of  $2\times$  and  $4\times$  are available to ease requirements on an external reconstruction filter. For single channel systems, the digital Hilbert filter can be used with an external quadrature modulator to create an image rejection architecture. The two 12-/14-bit, high performance DACs produce an output signal that can be scaled over a 20 dB range by the TxPGA.

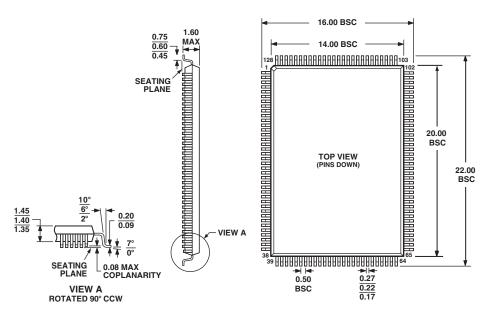

A programmable delay-locked loop (DLL) clock multiplier and integrated timing circuits enable the use of a single external reference clock or an external crystal to generate clocking for all internal blocks and also provides two external clock outputs. Additional features include a programmable sigma-delta output, four auxiliary ADC inputs and three auxiliary DAC outputs. Device programmability is facilitated by a serial port interface (SPI) combined with a register bank. The AD9860/AD9862 is available in a space saving 128-lead LQFP.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

# $\label{eq:continuous_problem} \textbf{AD9860/AD9862-SPECIFICATIONS} \\ (V_{A} = 3.3 \text{ V} \pm 5\%, V_{D} = 3.3 \text{ V} \pm 10\%, f_{DAC} = 128 \text{ MHz}, f_{ADC} = 64 \text{ MHz} \\ \text{Normal Timing Mode, } 2 \times \text{ DLL Setting, } R_{SET} = 4 \text{ k}\Omega, 50 \text{ }\Omega \text{ DAC Load, } \\ \text{RxPGA} = +6 \text{ dB Gain, } \text{TxPGA} = +20 \text{ dB Gain.}) \\ \end{cases}$

|                                                                                                |       | Test  |       | AD9860/AD9862 |                     |                                                         |

|------------------------------------------------------------------------------------------------|-------|-------|-------|---------------|---------------------|---------------------------------------------------------|

| Tx PARAMETERS                                                                                  | Temp  | Level | Min   | Тур           | Max                 | Unit                                                    |

| 12-/14-BIT DAC CHARACTERISTICS                                                                 |       |       |       |               |                     |                                                         |

| Resolution                                                                                     | NA    | NA    |       | 12/14         |                     | Bits                                                    |

| Maximum Update Rate                                                                            |       |       | 128   |               |                     | MSPS                                                    |

| Full-Scale Output Current                                                                      | Full  | I     | 2     |               | 20                  | mA                                                      |

| Gain Error (Using Internal Reference)                                                          | 25°C  | I     | -5.5  | +0.5          | +5.5                | %FS                                                     |

| Offset Error                                                                                   | 25°C  | I     | -1    | 0.0           | +1                  | %FS                                                     |

| Reference Voltage (REFIO Level)                                                                | 25°C  | I     | 1.15  | 1.22          | 1.28                | V                                                       |

| Negative Differential Nonlinearity (–DNL)                                                      | 25°C  | III   |       | -0.5/-0.5     |                     | LSB                                                     |

| Positive Differential Nonlinearity (+DNL)                                                      | 25°C  | III   |       | 1/2           |                     | LSB                                                     |

| Integral Nonlinearity (INL)                                                                    | 25°C  | III   |       | $\pm 1/\pm 3$ |                     | LSB                                                     |

| Output Capacitance                                                                             | 25°C  | III   |       | 5             |                     | pF                                                      |

| Phase Noise @ 1 kHz Offset, 6 MHz Tone                                                         |       |       |       |               |                     | -                                                       |

| Crystal and OSC IN Multiplier Enabled at 4×                                                    | 25°C  | III   |       | -115          |                     | dBc/Hz                                                  |

| Output Voltage Compliance Range                                                                | Full  | II    | -0.5  |               | +1.5                | V                                                       |

| TRANSMIT TxPGA CHARACTERISTICS                                                                 |       |       |       |               |                     |                                                         |

| Gain Range                                                                                     | 25°C  | III   |       | 20            |                     | dB                                                      |

| Step Size Accuracy                                                                             | 25°C  | III   |       | ±0.1          |                     | dB                                                      |

| Step Size                                                                                      | 25°C  | III   |       | 0.08          |                     | dB                                                      |

| <del></del>                                                                                    |       |       |       |               |                     |                                                         |

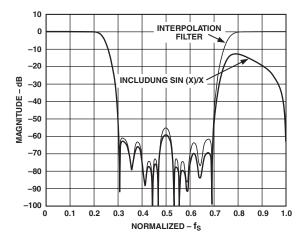

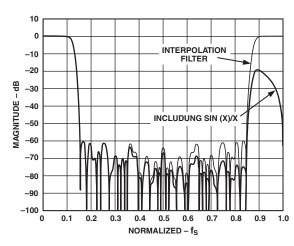

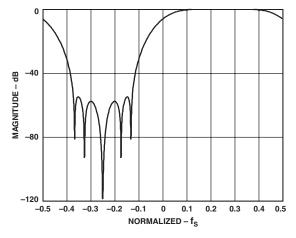

| Tx DIGITAL FILTER CHARACTERISTICS Hilbert Filter Pass Band (<0.1 dB Ripple)                    | Full  | II    | 12.5  |               | 20                  | 0/ £ 1                                                  |

| Hilbert Filter Pass Band (<0.1 dB Ripple) $2 \times /4 \times \text{Interpolator Stop Band}^2$ | Full  | II    | 12.5  |               | 38<br>±38           | % f <sub>DATA</sub> <sup>1</sup><br>% f <sub>DATA</sub> |

|                                                                                                | Full  | 11    |       |               | ±36                 | 70 IDATA                                                |

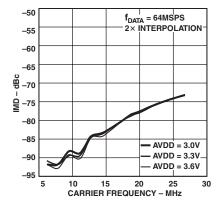

| DYNAMIC PERFORMANCE (A <sub>OUT</sub> = 20 mA FS, f = 1 MHz)                                   |       |       |       |               |                     |                                                         |

| Differential Phase                                                                             | 25°C  | III   |       | <0.1          |                     | Degree                                                  |

| Differential Gain                                                                              | 25°C  | III   |       | <1            |                     | LSB                                                     |

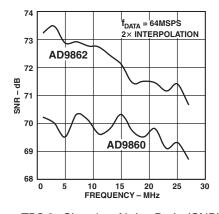

| AD9860 Signal-to-Noise Ratio (SNR)                                                             | Full  | I     | 68.2  | 70.7          |                     | dB                                                      |

| AD9860 Signal-to-Noise and Distortion Ratio                                                    | Full  | I     | 62.5  | 66.1          |                     | dB                                                      |

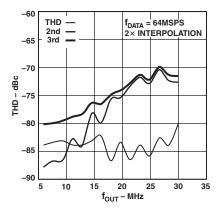

| AD9860 Total Harmonic Distortion (THD)                                                         | Full  | I     |       | -74.5         | -64.0               | dB                                                      |

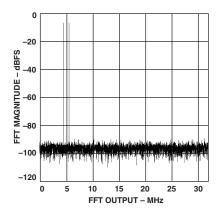

| AD9860 Wideband SFDR (to Nyquist)                                                              | 2.500 |       |       |               |                     | 15                                                      |

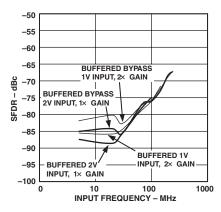

| 1 MHz Analog Out, I <sub>OUT</sub> = 2 mA                                                      | 25°C  | III   |       | 70.6          |                     | dBc                                                     |

| 1 MHz Analog Out, I <sub>OUT</sub> = 20 mA                                                     | 25°C  | I     | 64.4  | 75<br>7.5     |                     | dBc                                                     |

| 6 MHz Analog Out, I <sub>OUT</sub> = 20 mA                                                     | 25°C  | III   |       | 75            |                     | dBc                                                     |

| AD9860 Narrowband SFDR (1 MHz Window)                                                          | 2500  | ***   |       | 70.0          |                     | 1D                                                      |

| 1 MHz Analog Out, I <sub>OUT</sub> = 2 mA                                                      | 25°C  | III   | 0.2   | 70.2          |                     | dBc                                                     |

| 1 MHz Analog Out, I <sub>OUT</sub> = 20 mA                                                     | 25°C  | I     | 83    | 90            |                     | dBc                                                     |

| AD9862 Signal-to-Noise Ratio (SNR)                                                             | Full  | I     | 68.9  | 72.0          |                     | dB                                                      |

| AD9862 Signal-to-Noise and Distortion Ratio                                                    | Full  | I     | 64.75 | 69.8          | <i>(</i> <b>5</b> 0 | dB                                                      |

| AD9862 Total Harmonic Distortion (THD)                                                         | Full  | I     |       | -75.5         | -65.0               | dB                                                      |

| AD9862 Wideband SFDR (to Nyquist) 1 MHz Analog Out, I <sub>OUT</sub> = 2 mA                    | 25°C  | III   |       | 70.6          |                     | dBc                                                     |

| * · · · · · · · · · · · · · · · · · · ·                                                        | 25°C  | I     | 64.9  |               |                     | dBc                                                     |

| 1 MHz Analog Out, I <sub>OUT</sub> = 20 mA                                                     | 25°C  | III   | 04.9  | 76.0<br>76.0  |                     | dBc                                                     |

| 6 MHz Analog Out, I <sub>OUT</sub> = 20 mA<br>AD9862 Narrowband SFDR (1 MHz Window)            | 25 C  | 1111  |       | 70.0          |                     | ubc                                                     |

| 1 MHz Analog Out, I <sub>OUT</sub> = 2 mA                                                      | 25°C  | III   |       | 70.2          |                     | dBc                                                     |

| 1 MHz Analog Out, $I_{OUT} = 20 \text{ mA}$                                                    | 25°C  | I     | 83    | 90            |                     | dBc                                                     |

|                                                                                                | 25 C  | 1     | 65    | 90            |                     | авс                                                     |

| Rx PARAMETERS                                                                                  |       |       |       |               |                     |                                                         |

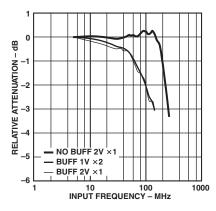

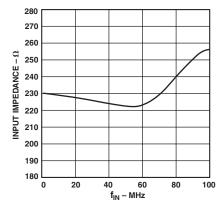

| RECEIVE BUFFER                                                                                 |       |       |       |               |                     |                                                         |

| Input Resistance (Differential)                                                                | Full  | III   |       | 200           |                     | Ω_                                                      |

| Input Capacitance (Each Input)                                                                 | Full  | III   |       | 5             |                     | pF                                                      |

| Maximum Input Bandwidth (-3 dB)                                                                | Full  | III   |       | 140           |                     | MHz                                                     |

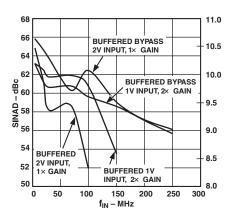

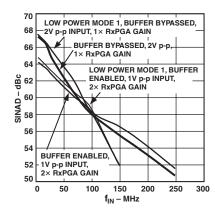

| Analog Input Range (Best Noise Performance)                                                    | Full  | II    |       | 2             |                     | V p-p Diff                                              |

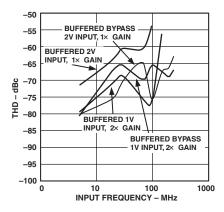

| Analog Input Range (Best THD Performance)                                                      | Full  | II    |       | 1             |                     | V p-p Diff                                              |

| RECEIVE PGA CHARACTERISTICS                                                                    |       |       |       |               |                     |                                                         |

| Gain Error                                                                                     | 25°C  | I     |       | $\pm 0.3$     |                     | dB                                                      |

| Gain Range                                                                                     | 25°C  | I     | 19    | 20            | 21                  | dB                                                      |

| Step Size Accuracy                                                                             | 25°C  | I     |       | $\pm 0.2$     |                     | dB                                                      |

| Step Size                                                                                      | 25°C  | I     |       | 1             |                     | dB                                                      |

| Input Bandwidth (-3 dB, Rx Buffer Bypassed)                                                    | 25°C  | III   |       | 250           |                     | MHz                                                     |

| 10 /10 DIT ADC CHADACTEDICTICS                                                                 |       |       |       |               |                     |                                                         |

| 10-/12-BIT ADC CHARACTERISTICS                                                                 |       | 1     | i i   |               |                     | 1                                                       |

| 10-/12-BIT ADC CHARACTERISTICS<br>Resolution                                                   | NA    | NA    |       | 10/12         |                     | Bits                                                    |

-2- REV. 0

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              | Test            | ADS        | 9860/AD986            | 52      |                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------|------------|-----------------------|---------|----------------------|

| Rx PARAMETERS (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Temp                                         | Level           | Min        | Typ                   | Max     | Unit                 |

| OC ACCURACY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |                 |            |                       |         |                      |

| Differential Nonlinearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25°C                                         | III             |            | $\pm 0.3/\pm 0.4$     | 4       | LSB                  |

| Integral Nonlinearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25°C                                         | III             |            | $\pm 1.2/\pm 5$       | •       | LSB                  |

| Offset Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25°C                                         | III             |            | $\pm 0.1$             |         | %FSR                 |

| Gain Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25°C                                         | III             |            |                       |         | %FSR                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |                 |            | ±0.2                  |         |                      |

| Aperture Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25°C                                         | III             |            | 2.0                   |         | ns                   |

| Aperture Uncertainty (Jitter)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25°C                                         | III             |            | 1.2                   |         | ps rms               |

| Input Referred Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25°C                                         | III             |            | 250                   |         | μV                   |

| Reference Voltage Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |                 |            |                       |         |                      |

| REFT-REFB Error (1 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25°C                                         | I               |            | ±1                    | $\pm 4$ | mV                   |

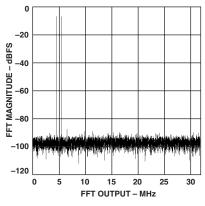

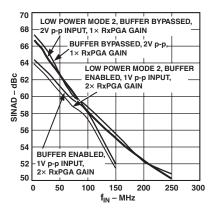

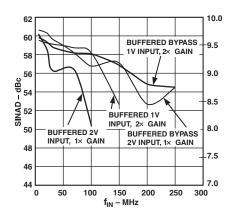

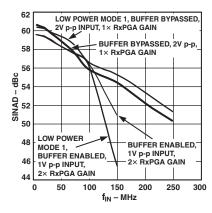

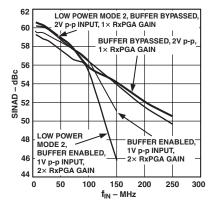

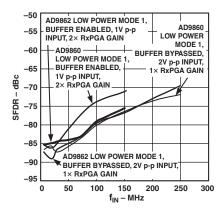

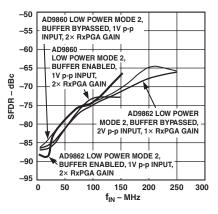

| $\Delta$ D9860 DYNAMIC PERFORMANCE (A <sub>IN</sub> = -0.5 dBFS, f = 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MHz)                                         |                 |            |                       |         |                      |

| Signal-to-Noise Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25°C                                         | I               | 59.0       | 60.66                 |         | dBc                  |

| Signal-to-Noise and Distortion Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25°C                                         | Ī               | 56.0       | 58.0                  |         | dBc                  |

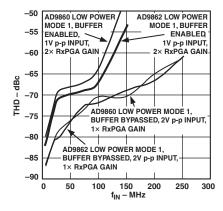

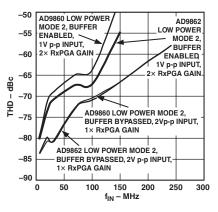

| Total Harmonic Distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25°C                                         | Ī               | 30.0       | -76.5                 | -70.5   | dBc                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25°C                                         | I               | 70.2       | -70.5<br>81.0         | -10.5   | dBc                  |

| Spurious Free Dynamic Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25°C                                         | 1               | 70.3       | 81.0                  |         | авс                  |

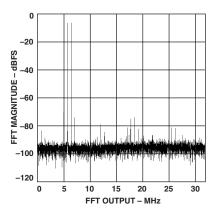

| $\Delta$ D9862 DYNAMIC PERFORMANCE ( $A_{\rm IN}$ = -0.5 dBFS, f =                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |                 |            |                       |         |                      |

| Signal-to-Noise Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25°C                                         | I               | 62.6       | 64.2                  |         | dBc                  |

| Signal-to-Noise and Distortion Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25°C                                         | I               | 62.5       | 64.14                 |         | dBc                  |

| Total Harmonic Distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25°C                                         | I               |            | -79.22                | -73.2   | dBc                  |

| Spurious Free Dynamic Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25°C                                         | I               | 77.09      | 85.13                 |         | dBc                  |

| CHANNEL-TO-CHANNEL ISOLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |                 |            |                       |         |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2500                                         | III             |            | >00                   |         | dB                   |

| Tx-to-Rx ( $A_{OUT} = 0$ dBFS, $f_{OUT} = 7$ MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25°C                                         |                 |            | >90                   |         |                      |

| Rx Channel Crosstalk ( $f_1 = 6 \text{ MHz}$ , $f_2 = 9 \text{ MHz}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25°C                                         | III             |            | >80                   |         | dB                   |

| PARAMETERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |                 |            |                       |         |                      |

| CMOS LOGIC INPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |                 |            |                       |         |                      |

| Logic "1" Voltage, V <sub>IH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25°C                                         | II              | DRVDD - 0. | .7                    |         | V                    |

| Logic "0" Voltage, V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25°C                                         | II              |            |                       | 0.4     | V                    |

| Logic "1" Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25°C                                         | II              |            |                       | 12      | μA                   |

| Logic "0" Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25°C                                         | II              |            |                       | 12      | μΑ                   |

| Input Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25°C                                         | III             |            | 3                     | 12      | pF                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | +                                            |                 |            |                       |         | F-                   |

| CMOS LOGIC OUTPUTS (1 mA Load)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25°C                                         | II              | DRVDD - 0. | 6                     |         | V                    |

| Logic "1" Voltage, V <sub>OH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |                 | DRVDD - 0. | .0                    | 0.4     |                      |

| Logic "0" Voltage, V <sub>OL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25°C                                         | II              |            |                       | 0.4     | V                    |

| OWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |                 |            |                       |         |                      |

| Analog Supply Currents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |                 |            |                       |         |                      |

| Tx (Both Channels, 20 mA FS Output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25°C                                         | I               |            | 70                    | 76      | mA                   |

| Tx Powered Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25°C                                         | I               |            | 2.5                   | 5.0     | mA                   |

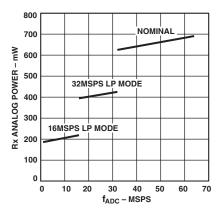

| Rx (Both Channels, Input Buffer Enabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25°C                                         | I               |            | 275                   | 307     | mA                   |

| Rx (Both Channels, Input Buffer Disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25°C                                         | III             |            | 245                   |         | mA                   |

| Rx (32 MSPS, Low Power Mode, Buffer Disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25°C                                         | III             |            | 155                   |         | mA                   |

| IX (32 MISI 5; LOW I OWEI MISUCE DUILEI DISABILEI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25°C                                         | III             |            | 80                    |         | mA                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |                 |            | 5.0                   | 6.0     | mA                   |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |                 |            | 0.0                   | 6.0     | 1 111174             |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled)<br>Rx Path Powered Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25°C                                         | I               |            |                       |         |                      |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled)<br>Rx Path Powered Down<br>DLL                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              | III             |            | 12                    |         | mA                   |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled) Rx Path Powered Down DLL Digital Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25°C                                         |                 |            |                       |         |                      |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled) Rx Path Powered Down DLL Digital Supply Current AD9860 Both Rx and Tx Path (All Channels Enabled)                                                                                                                                                                                                                                                                                                                                                                                        | 25°C<br>25°C                                 | III             |            | 12                    |         | mA                   |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled) Rx Path Powered Down DLL Digital Supply Current AD9860 Both Rx and Tx Path (All Channels Enabled) $2 \times$ Interpolation, $f_{DAC} = f_{ADC} = 64$ MSPS                                                                                                                                                                                                                                                                                                                                | 25°C                                         |                 |            |                       | 112     |                      |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled) Rx Path Powered Down DLL Digital Supply Current AD9860 Both Rx and Tx Path (All Channels Enabled) $2 \times$ Interpolation, $f_{DAC} = f_{ADC} = 64$ MSPS AD9862 Both Rx and Tx Path (All Channels Enabled)                                                                                                                                                                                                                                                                              | 25°C<br>25°C                                 | I               |            | 12<br>92              | 112     | mA                   |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled) Rx Path Powered Down DLL Digital Supply Current AD9860 Both Rx and Tx Path (All Channels Enabled) $2 \times$ Interpolation, $f_{DAC} = f_{ADC} = 64$ MSPS                                                                                                                                                                                                                                                                                                                                | 25°C<br>25°C                                 | III             |            | 12                    |         | mA                   |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled) Rx Path Powered Down DLL Digital Supply Current AD9860 Both Rx and Tx Path (All Channels Enabled) $2\times$ Interpolation, $f_{DAC} = f_{ADC} = 64$ MSPS AD9862 Both Rx and Tx Path (All Channels Enabled) $2\times$ Interpolation, $f_{DAC} = f_{ADC} = 64$ MSPS                                                                                                                                                                                                                        | 25°C<br>25°C                                 | I               |            | 12<br>92              | 112     | mA<br>mA             |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled)<br>Rx Path Powered Down DLL Digital Supply Current AD9860 Both Rx and Tx Path (All Channels Enabled) $2\times$ Interpolation, $f_{DAC} = f_{ADC} = 64$ MSPS AD9862 Both Rx and Tx Path (All Channels Enabled) $2\times$ Interpolation, $f_{DAC} = f_{ADC} = 64$ MSPS Tx Path ( $f_{DAC} = 128$ MSPS)                                                                                                                                                                                     | 25°C<br>25°C<br>25°C<br>25°C                 | I               |            | 92<br>104             | 112     | mA<br>mA             |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled) Rx Path Powered Down DLL Digital Supply Current AD9860 Both Rx and Tx Path (All Channels Enabled) $2 \times \text{Interpolation}, f_{DAC} = f_{ADC} = 64 \text{ MSPS}$ AD9862 Both Rx and Tx Path (All Channels Enabled) $2 \times \text{Interpolation}, f_{DAC} = f_{ADC} = 64 \text{ MSPS}$ AD9862 Both Rx and Tx Path (All Channels Enabled) $2 \times \text{Interpolation}, f_{DAC} = f_{ADC} = 64 \text{ MSPS}$ Tx Path ( $f_{DAC} = 128 \text{ MSPS}$ ) Processing Blocks Disabled | 25°C<br>25°C<br>25°C<br>25°C<br>25°C         | III<br>I<br>III |            | 92<br>104<br>45       | 112     | mA<br>mA<br>mA       |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled) Rx Path Powered Down DLL Digital Supply Current AD9860 Both Rx and Tx Path (All Channels Enabled) $2 \times \text{ Interpolation, } f_{DAC} = f_{ADC} = 64 \text{ MSPS}$ AD9862 Both Rx and Tx Path (All Channels Enabled) $2 \times \text{ Interpolation, } f_{DAC} = f_{ADC} = 64 \text{ MSPS}$ Tx Path ( $f_{DAC} = 128 \text{ MSPS}$ ) Processing Blocks Disabled $4 \times \text{ Interpolation}$                                                                                   | 25°C<br>25°C<br>25°C<br>25°C<br>25°C<br>25°C | III III III     |            | 92<br>104<br>45<br>90 | 112     | mA<br>mA<br>mA<br>mA |

| Rx (16 MSPS, Low Power Mode, Buffer Disabled) Rx Path Powered Down DLL Digital Supply Current AD9860 Both Rx and Tx Path (All Channels Enabled) $2 \times \text{Interpolation}, f_{DAC} = f_{ADC} = 64 \text{ MSPS}$ AD9862 Both Rx and Tx Path (All Channels Enabled) $2 \times \text{Interpolation}, f_{DAC} = f_{ADC} = 64 \text{ MSPS}$ AD9862 Both Rx and Tx Path (All Channels Enabled) $2 \times \text{Interpolation}, f_{DAC} = f_{ADC} = 64 \text{ MSPS}$ Tx Path ( $f_{DAC} = 128 \text{ MSPS}$ ) Processing Blocks Disabled | 25°C<br>25°C<br>25°C<br>25°C<br>25°C         | III<br>I<br>III |            | 92<br>104<br>45       | 112     | mA<br>mA<br>mA       |

REV. 0 -3-

|                                       |      | Test  |     | AD9860/AD9 | 9862 |      |

|---------------------------------------|------|-------|-----|------------|------|------|

| PARAMETERS (continued)                | Temp | Level | Min | Typ        | Max  | Unit |

| POWER SUPPLY (continued)              |      |       |     |            |      |      |

| Rx Path $(f_{ADC} = 64 \text{ MSPS})$ |      |       |     |            |      |      |

| Processing Blocks Disabled            | 25°C | III   |     | 9          |      | mA   |

| Decimation Filter Enabled             | 25°C | III   |     | 15         |      | mA   |

| Hilbert Filter Enabled                | 25°C | III   |     | 16         |      | mA   |

| Hilbert and Decimation Filter Enabled | 25°C | III   |     | 18.5       |      | mA   |

Specifications subject to change without notice.

# **TIMING CHARACTERISTICS**

|                                                    |      | Test  |     | AD9860/AI | 09862 |              |

|----------------------------------------------------|------|-------|-----|-----------|-------|--------------|

| (20 pF Load)                                       | Temp | Level | Min | Typ       | Max   | Unit         |

| Minimum Reset Pulsewidth Low (t <sub>RI</sub> )    | NA   | NA    | 5   |           |       | Clock Cycles |

| Digital Output Rise/Fall Time                      | 25°C | III   | 2.8 |           | 4     | ns           |

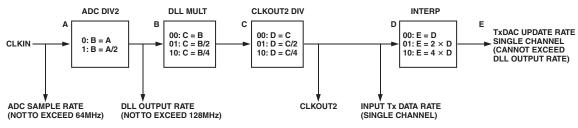

| DLL Output Clock                                   | 25°C | III   | 32  |           | 128   | MHz          |

| DLL Output Duty Cycle                              | 25°C | III   |     | 50        |       | %            |

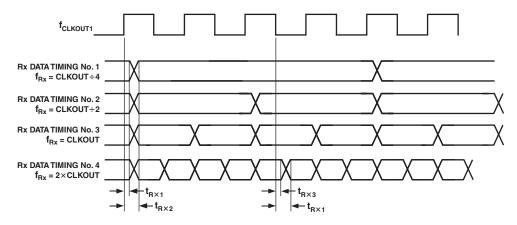

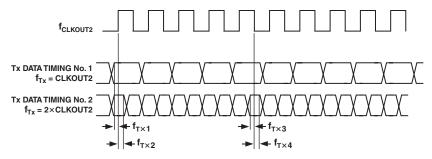

| Tx-/Rx-Interface (See Figures 11 and 12)           |      |       |     |           |       |              |

| TxSYNC/TxIQ Setup Time $(t_{Tx1}, t_{Tx3})$        | 25°C | III   | 3   |           |       | ns           |

| TxSYNC/TxIQ Hold Time $(t_{Tx2}, t_{Tx4})$         | 25°C | III   | 3   |           |       | ns           |

| RxSYNC/RxIQ/IF to Valid Time $(t_{Rx1}, t_{Rx3})$  | 25°C | III   |     |           | 5.2   | ns           |

| RxSYNC/RxIQ/IF Hold Time ( $t_{Rx2}$ , $t_{Rx4}$ ) | 25°C | III   | 0.2 |           | J.2   | ns           |

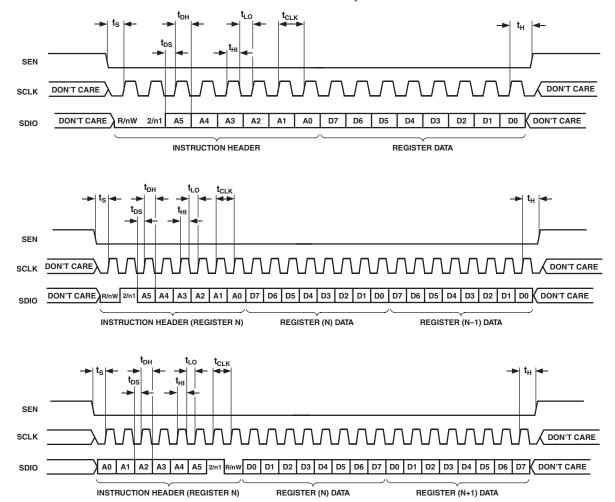

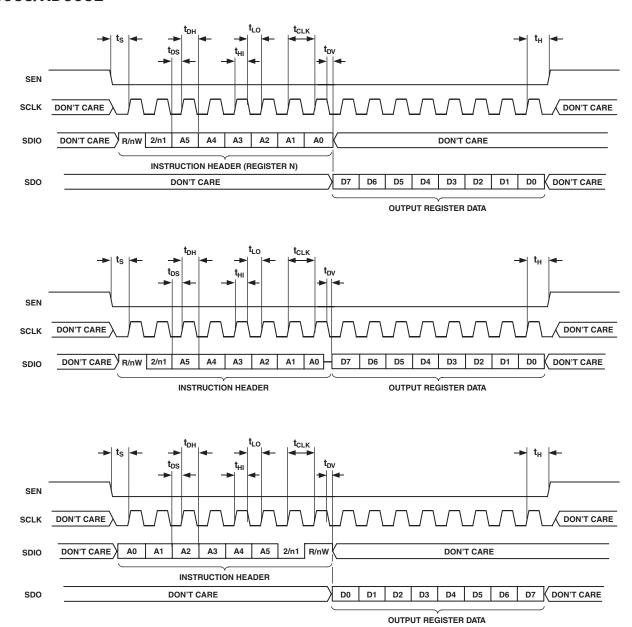

| Serial Control Bus (See Figures 1 and 2)           | 25 0 | 111   | 0.2 |           |       | 110          |

| Maximum SCLK Frequency (f <sub>SCLK</sub> )        | Full | III   |     |           | 16    | MHz          |

| Minimum Clock Pulsewidth High (t <sub>HI</sub> )   | Full | III   | 30  |           | 10    | ns           |

| Minimum Clock Pulsewidth Low (t <sub>I OW</sub> )  | Full | III   | 30  |           |       | ns           |

| Maximum Clock Rise/Fall Time                       | Full | III   | 30  |           | 1     | ms           |

| Minimum Data/SEN Setup Time (t <sub>S</sub> )      | Full | III   | 25  |           | 1     | ns           |

| Minimum SEN/Data Hold Time (t <sub>H</sub> )       | Full | III   | 0   |           |       | ns           |

| Minimum Data/SCLK Setup Time (t <sub>DS</sub> )    | Full | III   | 25  |           |       | ns           |

| Minimum Data Hold Time (t <sub>DS</sub> )          | Full | III   | 0   |           |       | ns           |

| Output Data Valid/SCLK Time (t <sub>DV</sub> )     | Full | III   | 0   |           | 30    | ns           |

| Output Data Valid/SCLK Time (tDV)                  | T'un | 111   |     |           | 30    | 118          |

| AUXILARY ADC                                       |      |       |     |           |       |              |

| Conversion Rate                                    | 25°C | III   |     | 1.25      |       | MHz          |

| Input Range                                        | 25°C | III   |     | 3         |       | V            |

| Resolution                                         | 25°C | III   |     | 10        |       | Bits         |

| AUXILARY DAC                                       |      |       |     |           |       |              |

| Settling Time                                      | 25°C | III   |     | 8         |       | μs           |

| Output Range                                       | 25°C | III   |     | 3         |       | V            |

| Resolution                                         | 25°C | III   |     | 8         |       | Bits         |

|                                                    | 25 0 | 111   |     |           |       | Dits         |

| ADC TIMING                                         |      |       |     | _         |       |              |

| Latency (All Digital Processing Blocks Disabled)   | 25°C | III   |     | 7         |       | Cycles       |

| DAC Timing                                         |      |       |     |           |       |              |

| Latency (All Digital Processing Blocks Disabled)   | 25°C | III   |     | 3         |       | Cycles       |

| Latency (2× Interpolation Enabled)                 | 25°C | III   |     | 30        |       | Cycles       |

| Latency (4× Interpolation Enabled)                 | 25°C | III   |     | 72        |       | Cycles       |

| Additional Latency (Hilbert Filter Enabled)        | 25°C | III   |     | 36        |       | Cycles       |

| Additional Latency (Coarse Modulation Enabled)     | 25°C | III   |     | 5         |       | Cycles       |

| Additional Latency (Fine Modulation Enabled)       | 25°C | III   |     | 8         |       | Cycles       |

| Output Settling Time (TST) (to 0.1%)               | 25°C | III   |     | 35        |       | ns           |

| - Output Setting Time (151) (to 0.170)             | 250  | 1111  |     |           |       | 115          |

Specifications subject to change without notice.

REV. 0 -4-

NOTES  $$^{1}\%$~f_{DATA}$  refers to the input data rate of the digital block.  $^{2}$  Interpolation filter stop band is defined by image suppression of 50 dB or greater.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Power Supply $(V_{AS}, V_{DS})$ 3.9 V            |

|--------------------------------------------------|

| Digital Output Current 5 mA                      |

| Digital Inputs0.3 V to DRVDD + 0.3 V             |

| Analog Inputs0.3 V to AVDD (IQ) + 0.3 V          |

| Operating Temperature <sup>2</sup> 40°C to +70°C |

| Maximum Junction Temperature                     |

| Storage Temperature65°C to +150°C                |

| Lead Temperature (Soldering 10 sec) 300°C        |

|                                                  |

#### NOTES

#### **EXPLANATION OF TEST LEVELS**

- I. Devices are 100% production tested at 25°C and guaranteed by design and characterization testing for the extended industrial temperature range (-40°C to +70°C).

- Parameter is guaranteed by design and/or characterization testing.

- III. Parameter is a typical value only.

- NA. Test level definition is not applicable.

#### THERMAL CHARACTERISTICS

Thermal Resistance

128-Lead LQFP  $\theta_{JA} = 29^{\circ}$ C/W

#### **ORDERING GUIDE**

| Model     | Temperature Range | Package Description                               | Package Option |

|-----------|-------------------|---------------------------------------------------|----------------|

| AD9860BST | −40°C to +70°C*   | 128-Lead Low Profile Plastic Quad Flatpack (LQFP) | ST-128B        |

| AD9862BST | –40°C to +70°C*   | 128-Lead Low Profile Plastic Quad Flatpack (LQFP) | ST-128B        |

| AD9860PCB |                   | Evaluation Board with AD9860                      |                |

| AD9862PCB |                   | Evaluation Board with AD9862                      |                |

<sup>\*</sup>The AD9860/AD9862 have been characterized to operate over the industrial temperature range (-40°C to +85°C) when operated in Half Duplex Mode.

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9860/AD9862 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0 -5-

<sup>&</sup>lt;sup>1</sup>Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

$<sup>^2</sup> The \ AD9860/AD9862$  have been characterized to operate over the industrial temperature range (–40°C to +85°C) when operated in Half Duplex Mode.

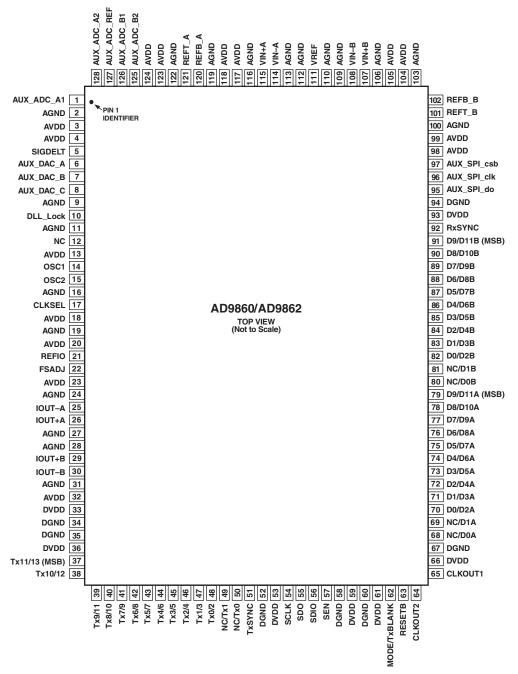

#### PIN CONFIGURATION

NC = NO CONNECT

-6- REV. 0

#### PIN FUNCTION DESCRIPTIONS

| Pin No.                             | Mnemonic          | Function                                                          | Pin No.                    | Mnemonic     | Function                                                                             |

|-------------------------------------|-------------------|-------------------------------------------------------------------|----------------------------|--------------|--------------------------------------------------------------------------------------|

|                                     | Receive Pins      |                                                                   |                            | Clock Pins   |                                                                                      |

| 68/70-79                            | D0A to            | 10-/12-Bit ADC Output of                                          | 10                         | DLL_Lock     | DLL Lock Indicator Pin                                                               |

|                                     | D9A/D11A          | Receive Channel A                                                 | 11, 16                     | AGND         | DLL Analog Ground Pins                                                               |

| 80/82-91                            | D0B to            | 10-/12-Bit ADC Output of                                          | 12                         | NC           | No Connect                                                                           |

|                                     | D9B/D11B          | Receive Channel B                                                 | 13                         | AVDD         | DLL Analog Supply Pin                                                                |

| 92                                  | RxSYNC            | Synchronization Clock for<br>Channel A and Channel B Rx Paths     | 14                         | OSC1         | Single Ended Input Clock<br>(or Crystal Oscillator Input)                            |

| 98, 99,                             | AVDD              | Analog Supply Pins                                                | 15                         | OSC2         | Crystal Oscillator Input                                                             |

| 104, 105,                           |                   |                                                                   | 17                         | CLKSEL       | Controls CLKOUT1 Rate                                                                |

| 117, 118, 123, 124,                 |                   |                                                                   | 64                         | CLKOUT2      | Clock Output Generated from Input                                                    |

| 100, 103,<br>106, 109,              | AGND              | Analog Ground Pins                                                |                            |              | Clock (DLL Multiplier Setting and CLKOUT2 Divide Factor)                             |

| 110, 112,<br>113, 116,<br>119, 122, |                   |                                                                   | 65                         | CLKOUT1      | Clock Output Generated from<br>Input Clock (1× if CLKSEL = 1<br>or /2 if CLKSEL = 0) |

| 101                                 | REFT_B            | Top Reference Decoupling for                                      | ,                          | Various Pins | 1                                                                                    |

|                                     |                   | Channel B ADC                                                     | 1                          | AUX_ADC_A1   | Auxiliary ADC A Input 1                                                              |

| 102                                 | REFB_B            | Bottom Reference Decoupling for Channel B ADC                     | 3, 4, 13                   | AVDD         | Analog Power Pins                                                                    |

| 107                                 | VIN+B             | Receive Channel B Differential (+) Input                          | 2, 9                       | AGND         | Analog Ground Pins                                                                   |

| 108                                 | VIN-B             | Receive Channel B Differential (-) Input                          | 5                          | SIGDELT      | Digital Output from                                                                  |

| 111                                 | VREF              | Internal ADC Voltage Reference                                    |                            |              | Programmable Sigma-Delta                                                             |

| 114                                 | VIN-A             | Receive Channel A Differential (–) Input                          | 6                          | AUX_DAC_A    | Auxiliary DAC A Output                                                               |

| 115                                 | VIN+A             | Receive Channel A Differential (+) Input                          | 7                          | AUX_DAC_B    | Auxiliary DAC B Output                                                               |

| 120                                 | REFB_A            | Bottom Reference Decoupling for                                   | 8                          | AUX_DAC_C    | Auxiliary DAC C Output                                                               |

|                                     | _                 | Channel A ADC                                                     | 33, 36, 53,<br>59, 61, 66, | DVDD         | Digital Power Supply Pin                                                             |

| 121                                 | REFT_A            | Top Reference Decoupling for Channel A ADC                        | 93                         |              |                                                                                      |

|                                     | Transmit Pi       |                                                                   | 34, 35, 52,<br>58, 60, 67, |              | Digital Ground Pin                                                                   |

| 18, 20                              | AVDD              | Analog Supply Pins                                                | 94                         |              |                                                                                      |

| 23, 32                              | III V D D         | Thining Supply This                                               | 54                         | SCLK         | Serial Bus Clock Input                                                               |

| 19, 24,                             | AGND              | Analog Ground Pins                                                | 55                         | SDO          | Serial Bus Data Bit                                                                  |

| 27, 28, 31                          |                   |                                                                   | 56                         | SDIO         | Serial Bus Data Bit                                                                  |

| 21                                  | REFIO             | Reference Output, 1.2 V Nominal                                   | 57                         | SEN          | Serial Bus Enable                                                                    |

| 22                                  | FSADJ             | Full-Scale Current Adjust                                         | 63                         | RESETB       | Reset (SPI Registers and Logic)                                                      |

| 25                                  | IOUT–A            | Transmit Channel A DAC Differential (–) Output                    | 95                         | AUX_SPI_do   | Optional Auxiliary ADC Serial Bus<br>Data Out Bit                                    |

| 26                                  | IOUT+A            | Transmit Channel A DAC Differential (+) Output                    | 96                         | AUX_SPI_clk  | Optional Auxiliary ADC Serial Bus<br>Data Out Latch Clock                            |

| 29                                  | IOUT+B            | Transmit Channel B DAC Differential (+) Output                    | 97                         | AUX_SPI_csb  | Optional Auxiliary ADC Serial Bus<br>Chip Select Bit                                 |

| 30                                  | IOUT-B            | Transmit Channel B DAC                                            | 128                        | AUX_ADC_A2   | Auxiliary ADC A Input 2                                                              |

|                                     |                   | Differential (–) Output                                           | 126                        | AUX_ADC_B1   | Auxiliary ADC B Input 1                                                              |

| 37-48/50                            | Tx11/Tx13         | 12-/14-Bit Transmit DAC Data                                      | 125                        | AUX_ADC_B2   | Auxiliary ADC B Input 2                                                              |

|                                     | to Tx0            | (Interleaved Data when Required)                                  | 127                        | AUX_ADC_REF  | Auxiliary ADC Reference                                                              |

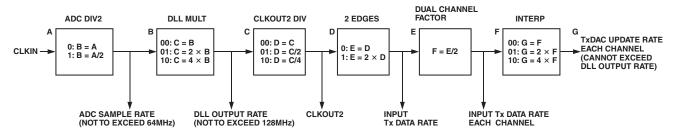

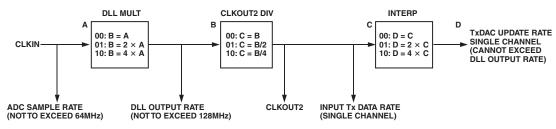

| 51                                  | TxSYNC            | Synchronization Input for Transmitter                             |                            | 1            | •                                                                                    |