# KSZ8794CNX

Integrated 4-Port 10/100 Managed Ethernet Switch with Gigabit RGMII/MII/RMII Interface

Revision 1.0

### **General Description**

The KSZ8794CNX is a highly integrated, Layer 2 managed, four-port switch with numerous features designed to reduce system cost. It is intended for costsensitive applications requiring three 10/100Mbps copper ports and one 10/100/1000Mbps Gigabit uplink port. The KSZ8794CNX incorporates a small package outline, lowest power consumption with internal biasing, and onchip termination. Its extensive features set includes enhanced power management, programmable rate limiting and priority ratio, tagged and port-based VLAN, port-based security and ACL rule-based packet filtering technology, QoS priority with four queues, management interfaces, enhanced MIB counters, high-performance memory bandwidth, and a shared memory-based switch fabric with non-blocking support. The KSZ8794CNX provides support for multiple CPU data interfaces to effectively address both current and emerging fast Ethernet and Gigabit Ethernet applications where the GMAC interface can be configured to any of RGMII, MII and RMII modes.

The KSZ8794CNX is built on Micrel's latest industryleading Ethernet analog and digital technology, with features designed to offload host processing and streamline your overall design:

- Three integrated 10/100Base-T/TX MAC/PHYs.

- One integrated 10/100/1000Base-T/TX GMAC with selectable RGMII, MII or RMII interfaces.

- Small 64-pin QFN package.

A robust assortment of power management features including Energy Efficient Ethernet (EEE), PME and WoL have been designed in to satisfy energy efficient environments.

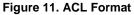

All registers in the MAC and PHY units can be managed through the SPI interface. MIIM PHY registers can be accessed through the MDC/MDIO interface.

Datasheets and support documentation are available on Micrel's web site at: <u>www.micrel.com</u>.

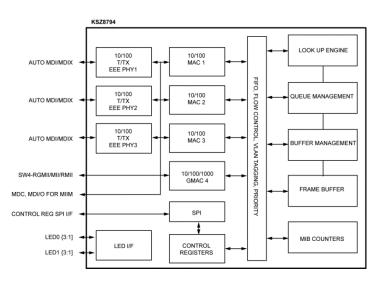

### **Functional Diagram**

LinkMD<sup>®</sup> is a registered trademark of Micrel, Inc.

Auto MDI/MDI-X<sup>™</sup> is a trademark of Hewlett-Pacard Company, L.P

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## **Highlights and Features**

### **Management Capabilities**

- The KSZ8794CNX includes all the functions of a 10/100Base-T/TX switch system which combines a switch engine, frame buffer management, address lookup table, queue management, MIB counters, media access controllers (MAC) and PHY transceivers

- Non-blocking store-and-forward switch fabric assures fast packet delivery by utilizing 1024 entries forwarding table

- Port mirroring/monitoring/sniffing: ingress and/or egress traffic to any port

- MIB counters for fully compliant statistics gathering 36 counters per port

- Support hardware for port-based flush and freeze command in MIB counter.

- Multiple loopback of remote, PHY and MAC modes support for the diagnostics

- Rapid Spanning Tree Support (RSTP) for topology management and ring/linear recovery

### **Robust PHY Ports**

- Four Integrated IEEE 802.3 / 802.3u compliant Ethernet transceivers supporting 10Base-T and 100Base-TX

- IEEE 802.1az EEE supported

- On-Chip termination resistors and internal biasing for differential pairs to reduce power

- HP Auto MDI/MDI-X<sup>™</sup> crossover support eliminating the need to differentiate between straight or crossover cables in applications

### MAC and GMAC Ports

- Four internal media access control (MAC1 to MAC3) units and one internal gigabit media access control (GMAC4) unit

- RGMII, MII or RMII interfaces support for the port 4 GMAC4 with uplink

- 2KByte Jumbo packet support

- Tail tagging mode (one byte added before FCS) support on port 4 to inform the processor which ingress port receives the packet and its priority

- Supports Reduced Media Independent Interface (RMII) with 50 MHz reference clock output

- Supports Media Independent Interface (MII) in either PHY mode or MAC mode on port 4

- Micrel LinkMD<sup>®</sup> cable diagnostic capabilities for determining cable opens, shorts, and length

### **Advanced Switch Capabilities**

- Non-blocking store-and-forward switch fabric assures fast packet delivery by utilizing 1024 entry forwarding table

- 64kb frame buffer RAM

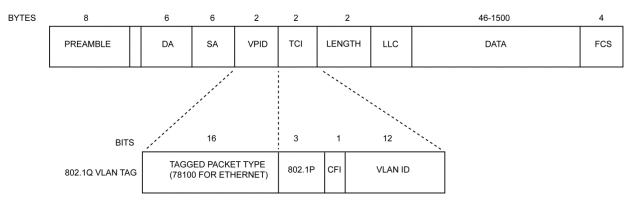

- IEEE 802.1q VLAN support for up to 128 active VLAN groups (full-range 4096 of VLAN IDs)

- IEEE 802.1p/Q tag insertion or removal on a per port basis (egress)

- VLAN ID tag/un-tag options on per port basis

- Fully compliant with IEEE 802.3/802.3u standards

- IEEE 802.3x full-duplex with force mode option and halfduplex back-pressure collision flow control

- IEEE 802.1w rapid spanning tree protocol support

- IGMP v1/v2/v3 snooping for multicast packet filtering

- QoS/CoS packets prioritization support: 802.1p, DiffServ-based and re-mapping of 802.1p priority field per port basis on four priority levels

- IPv4/IPv6 QoS support

- IPV6 multicast listener discovery (MLD) snooping

- Programmable rate limiting at the ingress and egress ports on a per port basis

- Jitter-free per packet based rate limiting support

- Tail tag mode (1 byte added before FCS) support on Port 4 to inform the processor which ingress port receives the packet

- Broadcast storm protection with percentage control (global and per port basis)

- 1K entry forwarding table with 64K Byte frame buffer

- 4 priority queues with dynamic packet mapping for IEEE 802.1P, IPv4 TOS (DIFFSERV), IPv6 Traffic Class, etc.

- Supports Wake on LAN (WoL) using AMD's Magic Packet

- VLAN and Address Filtering

- Support 802.1x port-based security, authentication and MAC-based authentication via access control lists (ACL)

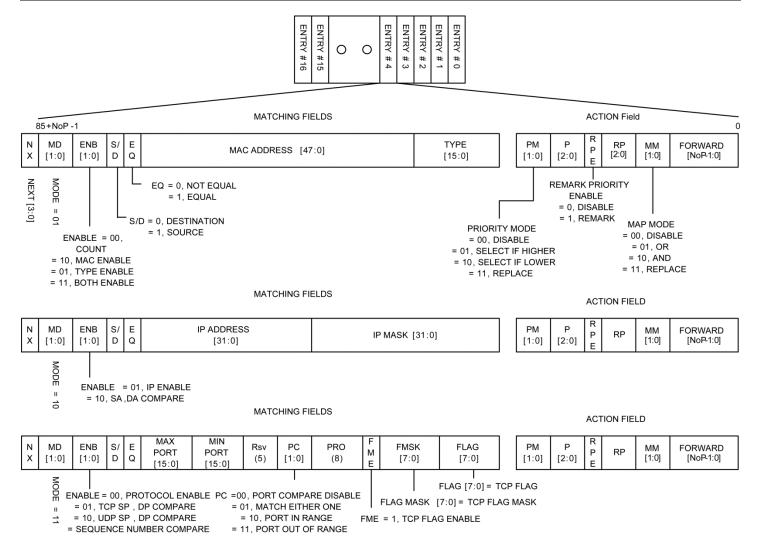

- Provide port-based and rule-based ACLs to support layer 2 MAC SA/DA address, layer 3 IP address and IP mask, layer 4 TCP/UDP port number, IP protocol, TCP flag and their combination for the port security filtering

- Ingress and egress rate limit based on bit per second (bps) and packet-based rate limiting (pps)

### **Configuration Registers Access**

- High speed SPI (4-wire, up to 50MHz) interface to access all internal registers

- MII Management (MIIM, MDC/MDIO 2-wire) Interface to access all PHY registers per Clause 22.2.4.5 of the IEEE 802.3 specification

- I/O pin strapping facility to set certain register bits from I/O pins during reset time

- Control registers configurable on-the-fly

### **Power and Power Management**

- Full-chip software power down (All registers value are not saved and strap-in value will re-strap after release the power down.)

- Per port software power down

- Energy Detect Power Down (EDPD), which disables the PHY transceiver when cables are removed

- Supports IEEE P802.3az energy-efficient Ethernet (EEE) to reduce power consumption in transceivers in LPI state even though cables are not removed

- Dynamic clock tree control to reduce clocking in areas not in use

- Very low power consumption (less than 0.5W) without extra power consumption on transformers

- Voltages: Using external LDO power supplies

Analog VDDAT 3.3V

- VDDIO support 3.3V, 2.5V and 1.8V

- -Low 1.2V voltage for analog and digital core power

- Wake on LAN support with configurable packet control

### **Additional Features**

- Single 25MHz +50ppm reference clock requirement

- Comprehensive programmable two LED indicator support for link, activity, full/half duplex and 10/100 speed

### Packaging and Environmental

- Commercial Temperature Range: 0°C to +70°C

- Industrial Temperature Range: -40°C to +85°C

- Small package available in an 64-pin lead free (ROHS) QFN form factor

- 0.065µm CMOS technology for lower power consumption

### **Target Applications**

- Industrial Ethernet applications that employ IEEE 802.3 compliant MACs. (Ethernet/IP, Profinet, MODBUS TCP, etc)

- VoIP Phone

- Set-top/Game Box

- Automotive

- Industrial Control

- IPTV POF

- SOHO Residential Gateway with full wire speed of four LAN Ports

- Broadband Gateway/Firewall/VPN

- Integrated DSL/Cable Modem

- Wireless LAN access point + gateway

- Standalone 10/100 switch

- Networked Measurement and Control Systems

# **Ordering Information**

| Part Number     | Temperature Range | Package          | Lead Finish/Grade  |

|-----------------|-------------------|------------------|--------------------|

| KSZ8794CNXCC    | 0°C to 70°C       | 64-Pin QFN       | Pb-Free/Commercial |

| KSZ8794CNXIC    | -40°C to +85°C    | 64-Pin QFN       | Pb-Free/Industrial |

| KSZ8794CNX-EVAL |                   | Evaluation Board |                    |

# **Revision History**

| Rev | vision | Date     | Description                                                        |

|-----|--------|----------|--------------------------------------------------------------------|

|     | 1.0    | 06/03/14 | Initial document created                                           |

|     | 1.0    | 07/18/14 | MarCom formatting/reflow of initial submission datasheet. D.Tanabe |

## Contents

| General Description                                                                           | 1  |

|-----------------------------------------------------------------------------------------------|----|

| Functional Diagram                                                                            |    |

| Highlights and Features                                                                       |    |

| Management Capabilities                                                                       |    |

| Robust PHY Ports                                                                              |    |

| MAC and GMAC Ports                                                                            |    |

| Advanced Switch Capabilities                                                                  |    |

| Configuration Registers Access                                                                |    |

| Power and Power Management                                                                    | 3  |

| Additional Features                                                                           | 3  |

| Packaging and Environmental                                                                   | 3  |

| Target Applications                                                                           | 3  |

| Ordering Information                                                                          |    |

| Revision History                                                                              |    |

| Contents<br>List of Figures                                                                   |    |

| List of Tables                                                                                |    |

| Pin Configuration                                                                             |    |

| Pin Description                                                                               |    |

| Strap-in Options                                                                              |    |

| Introduction                                                                                  |    |

| Functional Overview: Physical Layer (PHY)<br>100BASE-TX Transmit                              |    |

| 100BASE-TX Receive                                                                            |    |

| PLL Clock Synthesizer                                                                         |    |

| Scrambler/Descrambler (100BASE-TX only)                                                       |    |

| Straight Cable                                                                                | 24 |

| Crossover Cable                                                                               |    |

| Auto-Negotiation                                                                              | 25 |

| LinkMD <sup>®</sup> Cable Diagnostics                                                         | 27 |

| Access                                                                                        |    |

| Usage                                                                                         | 27 |

| A LinkMD example                                                                              |    |

| On-chip Termination and Internal Biasing                                                      |    |

| Functional Overview: Media Access Controller (MAC)<br>Media Access Controller (MAC) Operation |    |

| Inter-Packet Gap (IPG)                                                                        |    |

| Back-off Algorithm                                                                            |    |

| Late Collision                                                                                |    |

| Illegal Frames                                                                                |    |

| Flow Control                                                                                  |    |

| Half-Duplex Back Pressure                                                                     |    |

| ,                                                                                             |    |

| Broadcast Storm Protection                                                                    |    |

| Functional Overview: Switch Core<br>Address Look-Up                                           |    |

| Learning                                                                                      |    |

| Migration                                                                                     |    |

|                                                                                               |    |

| Aging                                                      |    |

|------------------------------------------------------------|----|

| Forwarding                                                 |    |

| Switching Engine                                           | 32 |

| Functional Overview: Power                                 |    |

| Functional Overview: Power Management                      |    |

| Normal Operation Mode                                      |    |

| Energy Detect Mode                                         |    |

| Soft Power-Down Mode                                       |    |

| Port-based Power-Down Mode                                 |    |

| Energy Efficient Ethernet (EEE)                            |    |

| LPI Signaling                                              |    |

| LPI Assertion                                              | 35 |

| LPI Detection                                              |    |

| PHY LPI Transmit Operation                                 | 36 |

| PHY LPI Receive Operation                                  | 37 |

| Negotiation with EEE Capability                            | 37 |

| Wake on LAN (WoL)                                          |    |

| Direction of Energy                                        |    |

| Direction of Link-up                                       |    |

| Magic Packet™                                              |    |

| Interrupt (INT_N/PME_N)<br>Functional Overview: Interfaces |    |

| Configuration Interface                                    |    |

| SPI Slave Serial Bus Configuration                         |    |

| MII Management Interface (MIIM)                            |    |

| Standard Media Independent Interface [MII]                 |    |

| Reduced Media Independent Interface [RMII]                 |    |

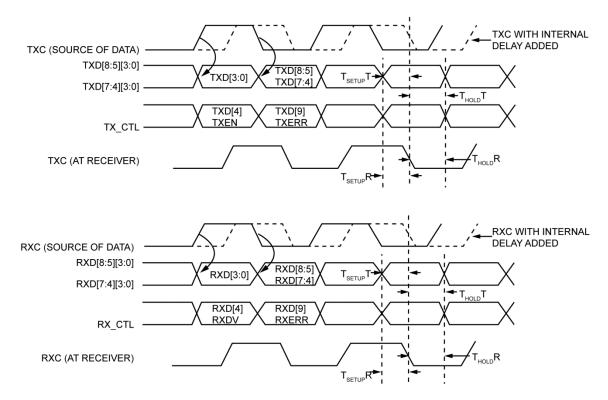

| Reduced Gigabit Media Independent Interface [RGMII]        |    |

| Port 4 GMAC4 SW4-RGMII Interface                           |    |

| Functional Overview: Advanced Functionality                |    |

| QoS Priority Support                                       |    |

| Port-based Priority                                        |    |

| 802.1p-based Priority                                      | 48 |

| DiffServ-Based Priority                                    | 49 |

| Spanning Tree Support                                      | 50 |

| Rapid Spanning Tree Support                                | 51 |

| Tail Tagging Mode                                          | 52 |

| IGMP Support                                               | 53 |

| IGMP Snooping                                              | 53 |

| IGMP Send Back to the Subscribed Port                      | 53 |

| IPv6 MLD Snooping                                          | 53 |

| Port Mirroring Support                                     | 53 |

| "Receive Only" mirror on a Port                            | 53 |

| "Transmit Only" mirror on a Port                           |    |

| "Receive and Transmit" mirror on two Ports                 | 53 |

| VLAN Support                                               | 54 |

| Ingress Rate Limit                                         | 56 |

| Egress Rate Limit                                                                      |  |

|----------------------------------------------------------------------------------------|--|

| Transmit Queue Ratio Programming                                                       |  |

| 802.1X Port-Based Security                                                             |  |

| Authentication Register and Programming Model                                          |  |

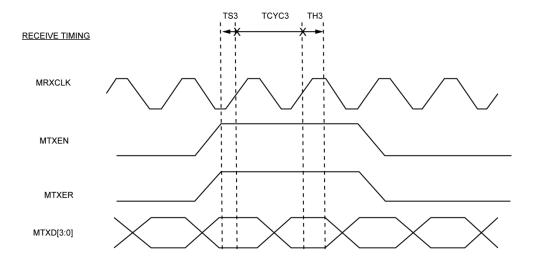

| ACL Filtering                                                                          |  |

| Access Control Lists                                                                   |  |

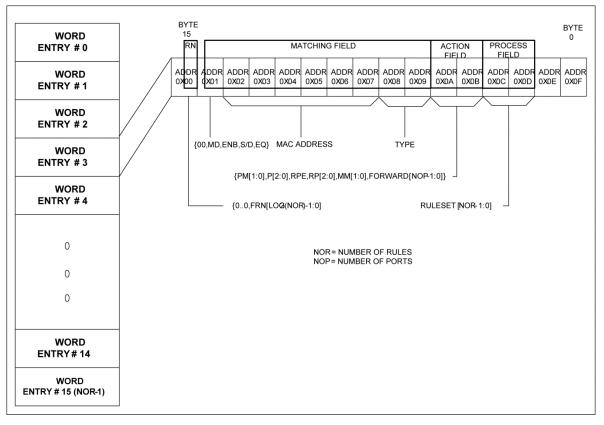

| Matching Field                                                                         |  |

| Action Field                                                                           |  |

| Processing Field                                                                       |  |

| DOS Attack Prevention via ACL                                                          |  |

| Device Registers Mapping                                                               |  |

| Direct Register Description                                                            |  |

| Global Registers<br>Register 0 (0x00): Chip ID0                                        |  |

| Register 1 (0x01): Chip ID1 / Start Switch                                             |  |

| Register 2 (0x02): Global Control 0                                                    |  |

| Register 3 (0x03): Global Control 1                                                    |  |

| Register 3 (0x03): Global Control 2                                                    |  |

| Register 6 (0x06): Global Control 4                                                    |  |

|                                                                                        |  |

| Register 7 (0x07): Global Control 5<br>Register 8 (0x08): Global Control 6 MIB Control |  |

| Register 9 (0x09): Global Control 7                                                    |  |

| Register 9 (0x09). Global Control 8                                                    |  |

| Register 10 (0x0A). Global Control 8<br>Register 11 (0x0B): Global Control 9           |  |

| Register 12 (0x0C): Global Control 9                                                   |  |

|                                                                                        |  |

| Register 13 (0x0D): Global Control 11                                                  |  |

| Register 14 (0x0E): Power Down Management Control 1                                    |  |

| Register 15 (0x0F): Power Down Management Control 2 Port Registers                     |  |

| Register 16 (0x10): Port 1 Control 0                                                   |  |

| Register 32 (0x20): Port 2 Control 0                                                   |  |

| Register 48 (0x30): Port 3 Control 0                                                   |  |

| Register 64 (0x40): Reserved                                                           |  |

| Register 80 (0x50): Port 4 Control 0                                                   |  |

| Register 17 (0x11): Port 1 Control 1                                                   |  |

| Register 33 (0x21): Port 2 Control 1                                                   |  |

| Register 49 (0x31): Port 3 Control 1                                                   |  |

| Register 65 (0x41): Reserved                                                           |  |

| Register 81 (0x51): Port 4 Control 1                                                   |  |

| Register 18 (0x12): Port 1 Control 2                                                   |  |

| Register 34 (0x22): Port 2 Control 2                                                   |  |

| Register 50 (0x32): Port 3 Control 2                                                   |  |

| Register 66 (0x42): Reserved                                                           |  |

| Register 82 (0x52): Port 4 Control 2                                                   |  |

| Register 19 (0x13): Port 1 Control 3                                                   |  |

| Register 35 (0x23): Port 2 Control 3                                                   |  |

|                                                                                        |  |

| Register 51 (0x33): Port 3 Control 3           | 75 |

|------------------------------------------------|----|

| Register 67 (0x43): Reserved                   | 75 |

| Register 83 (0x53): Port 4 Control 3           | 75 |

| Register 20 (0x14): Port 1 Control 4           |    |

| Register 36 (0x24): Port 2 Control 4           | 76 |

| Register 52 (0x34): Port 3 Control 4           | 76 |

| Register 68 (0x44): Reserved                   | 76 |

| Register 84 (0x54): Port 4 Control 4           | 76 |

| Register 21 (0x15): Port 1 Control 5           |    |

| Register 37 (0x25): Port 2 Control 5           | 76 |

| Register 53 (0x35): Port 3 Control 5           | 76 |

| Register 69 (0x45): Reserved                   | 76 |

| Register 85 (0x55): Port 4 Control 5           |    |

| Register 22 (0x16): Reserved                   |    |

| Register 38 (0x26): Reserved                   | 76 |

| Register 54 (0x36): Reserved                   |    |

| Register 70 (0x46): Reserved                   |    |

| Register 86 (0x56): Port 4 Interface Control 6 |    |

| Register 23 (0x17): Port 1 Control 7           | 78 |

| Register 39 (0x27): Port 2 Control 7           | 78 |

| Register 55 (0x37): Port 3 Control 7           | 78 |

| Register 71 (0x47): Reserved                   | 78 |

| Register 87 (0x57): Reserved                   | 78 |

| Register 24 (0x18): Port 1 Status 0            | 79 |

| Register 40 (0x28): Port 2 Status 0            | 79 |

| Register 56 (0x38): Port 3 Status 0            | 79 |

| Register 72 (0x48): Reserved                   | 79 |

| Register 87 (0x57): Reserved                   | 79 |

| Register 25 (0x19): Port 1 Status 1            | 80 |

| Register 41 (0x29): Port 2 Status 1            | 80 |

| Register 57 (0x39): Port 3 Status 1            | 80 |

| Register 73 (0x49): Reserved                   | 80 |

| Register 89 (0x59): Reserved                   | 80 |

| Register 26 (0x1A): Port 1 PHY Control 8       | 81 |

| Register 42 (0x2A): Port 2 PHY Control 8       | 81 |

| Register 58 (0x3A): Port 3 PHY Control 8       | 81 |

| Register 74 (0x4A): Reserved                   | 81 |

| Register 90 (0x5A): Reserved                   | 81 |

| Register 27 (0x1B): Port 1 LinkMD result       |    |

| Register 43 (0x2B): Port 2 LinkMD result       | 82 |

| Register 59 (0x3B): Port 3 LinkMD result       | 82 |

| Register 75 (0x4B): Reserved                   |    |

| Register 91 (0x5B): Reserved                   |    |

| Register 28 (0x1C): Port 1 Control 9           |    |

| Register 44 (0x2C): Port 2 Control 9           |    |

| Register 60 (0x3C): Port 3 Control 9                                               | 82 |

|------------------------------------------------------------------------------------|----|

| Register 76 (0x4C): Reserved                                                       | 82 |

| Register 92 (0x5C): Reserved                                                       | 82 |

| Register 29 (0x1D): Port 1 Control 10                                              | 83 |

| Register 45 (0x2D): Port 2 Control 10                                              | 83 |

| Register 61 (0x3D): Port 3 Control 10                                              | 83 |

| Register 77 (0x4D): Reserved                                                       | 83 |

| Register 93 (0x5D): Reserved                                                       | 83 |

| Register 30 (0x1E): Port 1 Status 2                                                |    |

| Register 46 (0x2E): Port 2 Status 2                                                |    |

| Register 62 (0x3E): Port 3 Status 2                                                |    |

| Register 78 (0x4E): Reserved                                                       |    |

| Register 94 (0x5E): Reserved                                                       |    |

| Register 31 (0x1F): Port 1 Control 11 and Status 3                                 |    |

| Register 47 (0x2F): Port 2 Control 11 and Status 3                                 |    |

| Register 63 (0x3F): Port 3 Control 11 and Status 3                                 |    |

| Register 79 (0x4F): Reserved                                                       |    |

| Register 95 (0x5F): Reserved                                                       |    |

| Advanced Control Registers                                                         |    |

| Register 104 (0x68): MAC Address Register 0                                        |    |

| Register 105 (0x69): MAC Address Register 1                                        |    |

| Register 106 (0x6A): MAC Address Register 2                                        |    |

| Register 107 (0x6B): MAC Address Register 3                                        |    |

| Register 108 (0x6C): MAC Address Register 4                                        |    |

| Register 110 (0x6E): Indirect Access Control 0                                     | 87 |

| Register 111 (0x6F): Indirect Access Control 1                                     |    |

| Register 112 (0x70): Indirect Data Register 8                                      |    |

| Register 113 (0x71): Indirect Data Register 7                                      | 88 |

| Register 114 (0x72): Indirect Data Register 6                                      | 88 |

| Register 115 (0x73): Indirect Data Register 5                                      | 88 |

| Register 116 (0x74): Indirect Data Register 4                                      | 88 |

| Register 117 (0x75): Indirect Data Register 3                                      | 88 |

| Register 118 (0x76): Indirect Data Register 2                                      | 88 |

| Register 119 (0x77): Indirect Data Register 1                                      | 88 |

| Register 120 (0x78): Indirect Data Register 0                                      | 88 |

| Register 160 (0XA0): Indirect Byte Register (It is for PME, EEE and ACL Registers) | 88 |

| Register 124 (0x7C): Interrupt Status Register                                     | 89 |

| Register 125 (0x7D): Interrupt Mask Register                                       | 89 |

| Register 126 (0x7E): ACL Interrupt Status Register                                 | 89 |

| Register 127 (0x7F): ACL Interrupt Control Register                                |    |

| Register 128 (0x80): Global Control 12                                             |    |

| Register 129 (0x81): Global Control 13                                             |    |

| Register 130 (0x82): Global Control 14                                             |    |

| Register 131 (0x83): Global Control 15                                             |    |

| Register 132 (0x84): Global Control 16                                             |    |

| Register 134 (0x86): Global Control 18                                             |    |

| Register 135 (0x87): Global Control 19                | 92 |

|-------------------------------------------------------|----|

| Register 144 (0x90): TOS Priority Control Register 0  | 93 |

| Register 145 (0x91): TOS Priority Control Register 1  | 93 |

| Register 146 (0x92): TOS Priority Control Register 2  | 93 |

| Register 147 (0x93): TOS Priority Control Register 3  | 93 |

| Register 148 (0x94): TOS Priority Control Register 4  | 93 |

| Register 149 (0x95): TOS Priority Control Register 5  | 94 |

| Register 150 (0x96): TOS Priority Control Register 6  | 94 |

| Register 151 (0x97): TOS Priority Control Register 7  | 94 |

| Register 152 (0x98): TOS Priority Control Register 8  | 94 |

| Register 153 (0x99): TOS Priority Control Register 9  |    |

| Register 154 (0x9A): TOS Priority Control Register 10 | 94 |

| Register 155 (0x9B): TOS Priority Control Register 11 |    |

| Register 156 (0x9C): TOS Priority Control Register 12 |    |

| Register 157 (0x9D): TOS Priority Control Register 13 | 95 |

| Register 158 (0x9E): TOS Priority Control Register 14 | 95 |

| Register 159 (0x9F): TOS Priority Control Register 15 | 95 |

| Register 163 (0XA3): Global Control 20                | 96 |

| Register 164 (0XA4): Global Control 21                | 96 |

| Register 176 (0xB0): Port 1 Control 12                |    |

| Register 192 (0xC0): Port 2 Control 12                | 97 |

| Register 208 (0xD0): Port 3 Control 12                | 97 |

| Register 224 (0xE0): Reserved                         | 97 |

| Register 240 (0xF0): Port 4 Control 12                | 97 |

| Register 177 (0xB1): Port 1 Control 13                | 98 |

| Register 193 (0xC1): Port 2 Control 13                | 98 |

| Register 209 (0xD1): Port 3 Control 13                | 98 |

| Register 225 (0xE1): Reserved                         | 98 |

| Register 241 (0xF1): Port 4 Control 13                | 98 |

| Register 178 (0xB2): Port 1 Control 14                | 98 |

| Register 194 (0xC2): Port 2 Control 14                | 98 |

| Register 210 (0xD2): Port 3 Control 14                | 98 |

| Register 226 (0xE2): Reserved                         | 98 |

| Register 242 (0xF2): Port 4 Control 14                | 98 |

| Register 179 (0xB3): Port 1 Control 15                |    |

| Register 195 (0xC3): Port 2 Control 15                | 99 |

| Register 211 (0xD3): Port 3 Control 15                | 99 |

| Register 227 (0xE3): Reserved                         |    |

| Register 243 (0xF3): Port 4 Control 15                |    |

| Register 180 (0xB4): Port 1 Control 16                |    |

| Register 196 (0xC4): Port 2 Control 16                |    |

| Register 212 (0xD4): Port 3 Control 16                |    |

| Register 228 (0xE4): Reserved                         |    |

| Register 244 (0xF4): Port 4 Control 16                |    |

| Register 181 (0xB5): Port 1 Control 17                |    |

|                                                       |    |

| Register 197 (0xC5): Port 2 Control 17                                        |     |

|-------------------------------------------------------------------------------|-----|

| Register 213 (0xD5): Port 3 Control 17                                        | 99  |

| Register 229 (0xE5): Reserved                                                 |     |

| Register 245 (0xF5): Port 4 Control 17                                        |     |

| Register 182 (0xB6): Port 1 Rate Limit Control                                | 100 |

| Register 198 (0xC6): Port 2 Rate Limit Control                                | 100 |

| Register 214 (0xD6): Port 3 Rate Limit Control                                | 100 |

| Register 230 (0xE6): Reserved                                                 |     |

| Register 246 (0xF6): Port 4 Rate Limit Control                                | 100 |

| Register 183 (0xB7): Port 1 Priority 0 Ingress Limit Control 1 <sup>(4)</sup> |     |

| Register 199 (0xC7): Port 2 Priority 0 Ingress Limit Control 1                |     |

| Register 215 (0xD7): Port 3 Priority 0 Ingress Limit Control 1                |     |

| Register 231 (0xE7): Reserved                                                 |     |

| Register 247 (0xF7): Port 4 Priority 0 Ingress Limit Control 1                |     |

| Register 184 (0xB8): Port 1 Priority 1 Ingress Limit Control 2 <sup>(4)</sup> | 101 |

| Register 200 (0xC8): Port 2 Priority 1 Ingress Limit Control 2                |     |

| Register 216 (0xD8): Port 3 Priority 1 Ingress Limit Control 2                | 101 |

| Register 232 (0xE8): Reserved                                                 | 101 |

| Register 248 (0xF8): Port 4 Priority 1 Ingress Limit Control 2                | 101 |

| Register 185 (0xB9): Port 1 Priority 2 Ingress Limit Control 3 <sup>(4)</sup> | 101 |

| Register 201 (0xC9): Port 2 Priority 2 Ingress Limit Control 3                | 101 |

| Register 217 (0xD9): Port 3 Priority 2 Ingress Limit Control 3                | 101 |

| Register 233 (0xE9): Reserved                                                 |     |

| Register 249 (0xF9): Port 4 Priority 2 Ingress Limit Control 3                | 101 |

| Register 186 (0xBA): Port 1 Priority 3 Ingress Limit Control 4 <sup>(4)</sup> | 102 |

| Register 202 (0xCA): Port 2 Priority 3 Ingress Limit Control 4                | 102 |

| Register 218 (0xDA): Port 3 Priority 3 Ingress Limit Control 4                | 102 |

| Register 234 (0xEA): Reserved                                                 | 102 |

| Register 250 (0xFA): Port 4 Priority 3 Ingress Limit Control 4                |     |

| Register 187 (0xBB): Port 1 Queue 0 Egress Limit Control 1 <sup>(5)</sup>     |     |

| Register 203 (0xCB): Port 2 Queue 0 Egress Limit Control 1                    |     |

| Register 219 (0xDB): Port 3 Queue 0 Egress Limit Control 1                    | 103 |

| Register 235 (0xEB): Reserved                                                 | 103 |

| Register 251 (0xFB): Port 4 Queue 0 Egress Limit Control 1                    | 103 |

| Register 188 (0xBC) : Port 1 Queue 1 Egress Limit Control 2 <sup>(5)</sup>    |     |

| Register 204 (0xCC) : Port 2 Queue 1 Egress Limit Control 2                   |     |

| Register 220 (0xDC) : Port 3 Queue 1 Egress Limit Control 2                   |     |

| Register 236 (0xEC) : Reserved                                                | 103 |

| Register 252 (0xFC) : Port 4 Queue 1 Egress Limit Control 2                   | 103 |

| Register 189 (0xBD): Port 1 Queue 2 Egress Limit Control 3 <sup>(5)</sup>     |     |

| Register 205 (0xCD): Port 2 Queue 2 Egress Limit Control 3                    |     |

| Register 221 (0xDD): Port 3 Queue 2 Egress Limit Control 3                    |     |

| Register 237 (0xED): Reserved                                                 |     |

| Register 253 (0xFD): Port 4 Queue 2 Egress Limit Control 3                    |     |

| Register 190 (0xBE) : Port 1 Queue 3 Egress Limit Control 4 <sup>(5)</sup>    |     |

| Register 206 (0xCE) : Port 2 Queue 3 Egress Limit Control 4                      |     |

|----------------------------------------------------------------------------------|-----|

| Register 222 (0xDE) : Port 3 Queue 3 Egress Limit Control 4                      |     |

| Register 238 (0xEE): Reserved                                                    |     |

| Register 254 (0xFE): Port 4 Queue 3 Egress Limit Control 4                       | 103 |

| Register 191(0xBF): Testing Register                                             |     |

| Register 207(0xCF): Reserved Control Register                                    |     |

| Register 223(0xDF): Test Register 2                                              |     |

| Register 239(0xEF): Test Register 3                                              |     |

| Register 255(0xFF): Test Register 4                                              |     |

| Indirect Register Description                                                    |     |

| Static MAC Address Table                                                         |     |

|                                                                                  |     |

| Dynamic MAC Address Table<br>PME Indirect Registers                              |     |

| Programming Examples:                                                            |     |

| Read Operation                                                                   |     |

| ,<br>Write Operation                                                             |     |

| ACL Rule Table and ACL Indirect Registers                                        |     |

| ACL Register and Programming Model                                               |     |

| ACL Indirect Registers                                                           |     |

| EEE Indirect Registers                                                           |     |

| EEE Global Registers                                                             |     |

| Management Information Base (MIB) Counters                                       |     |

| MIIM Registers                                                                   |     |

| Absolute Maximum Ratings <sup>(6)</sup>                                          |     |

| Operating Ratings <sup>(7)</sup><br>Electrical Characteristics <sup>(9,10)</sup> |     |

| Timing Diagrams                                                                  |     |

| RGMII Timing                                                                     |     |

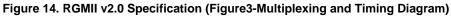

| MII Timing                                                                       |     |

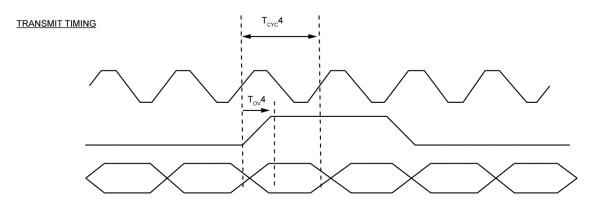

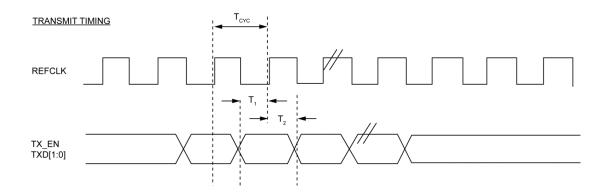

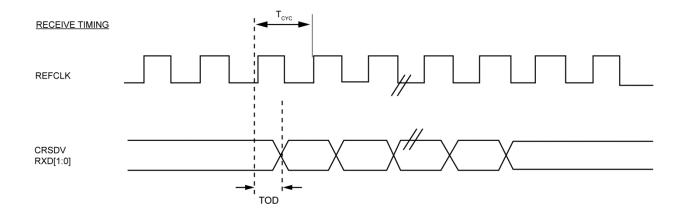

| RMII Timing                                                                      |     |

| SPI Timing                                                                       |     |

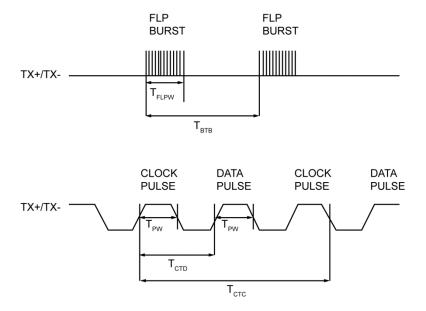

| Auto-Negotiation Timing                                                          |     |

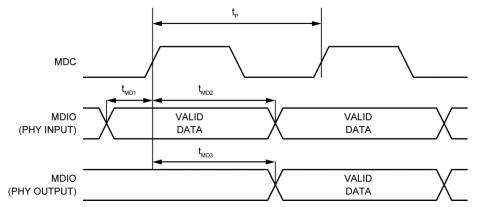

| MDC/MDIO Timing                                                                  |     |

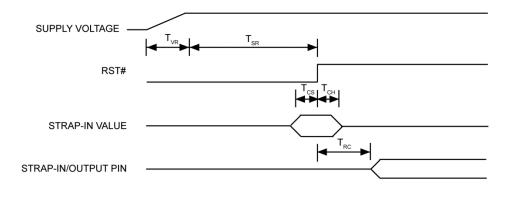

| Power-down/Power-up and Reset Timing                                             |     |

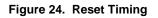

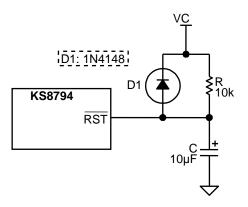

| Reset Circuit Diagram                                                            |     |

| Selection of Reference Crystal                                                   | 152 |

| MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA                           |     |

| Template Revision History                                                        |     |

## List of Figures

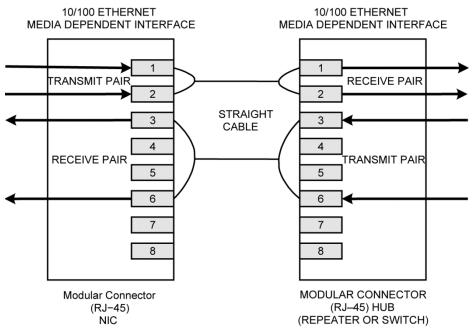

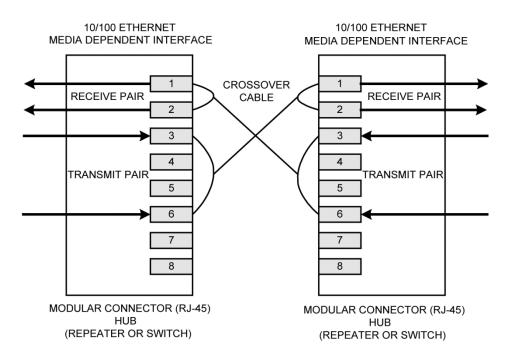

| Figure 1. Typical Straight Cable Connection                                   | 24  |

|-------------------------------------------------------------------------------|-----|

| Figure 2. Typical Crossover Cable Connection                                  | 24  |

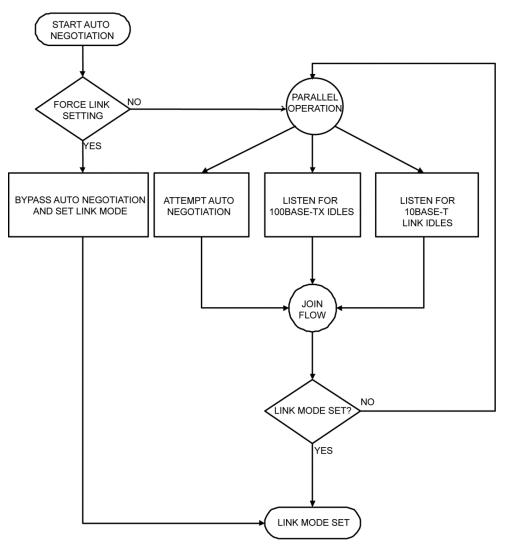

| Figure 3. Auto-Negotiation and Parallel Operation                             |     |

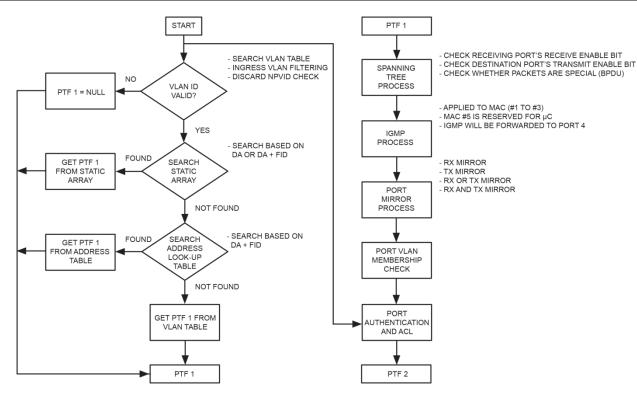

| Figure 4. Destination Address Lookup and Resolution Flow Chart                |     |

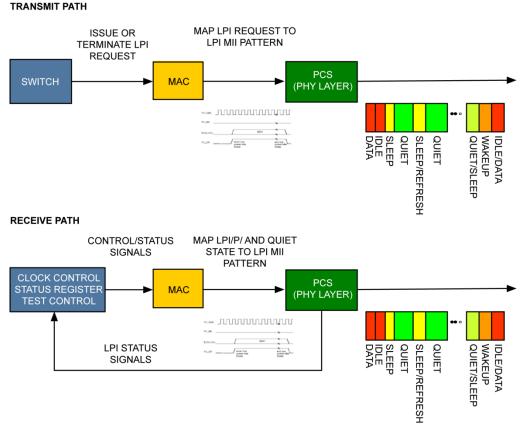

| Figure 5. EEE Transmit and Receive Signaling Paths                            |     |

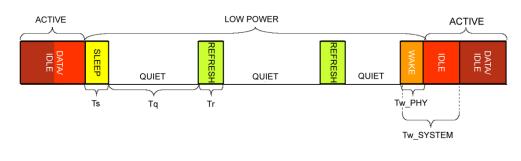

| Figure 6. Traffic Activity and EEE LPI Operations                             |     |

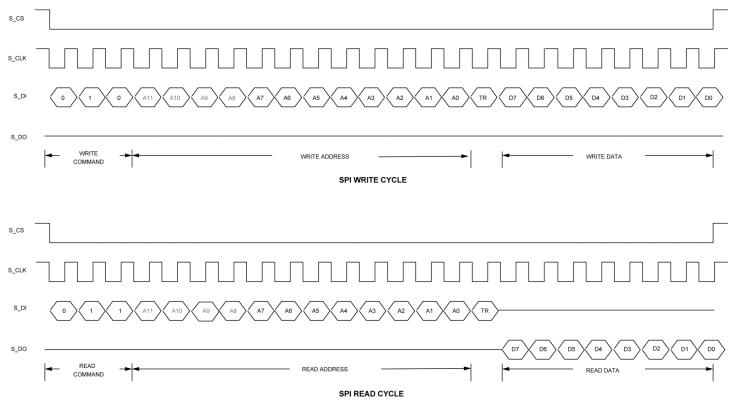

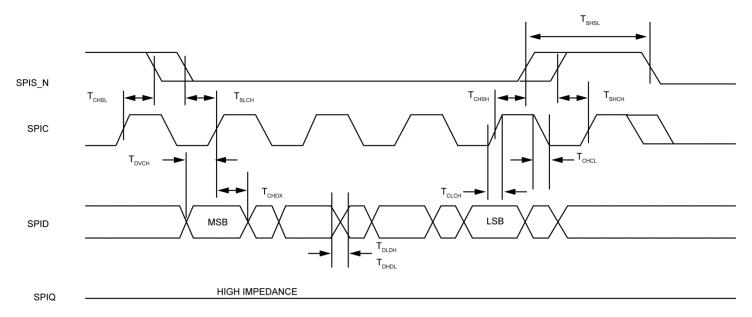

| Figure 7. SPI Access Timing                                                   |     |

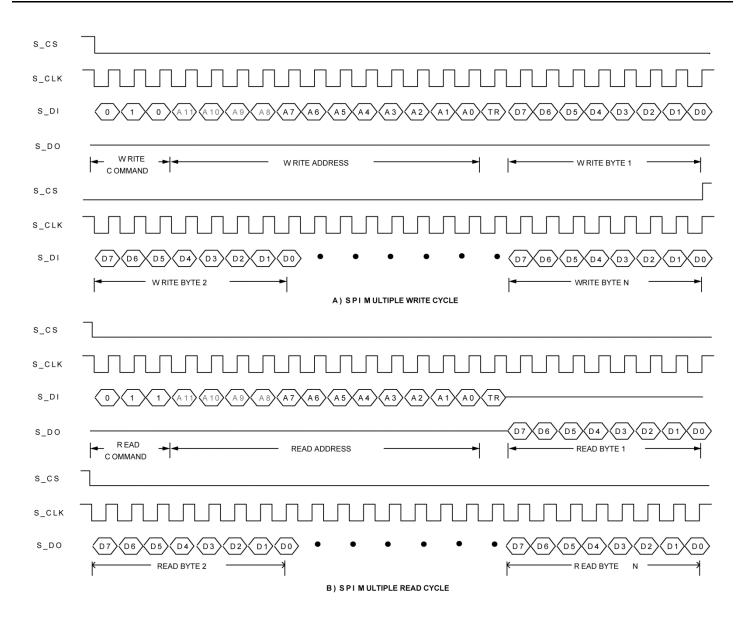

| Figure 8. SPI Multiple Access Timing                                          |     |

| Figure 9. 802.1p Priority Field Format                                        |     |

| Figure 10. Tail Tag Frame Format                                              |     |

| Figure 11. ACL Format                                                         |     |

| Figure 12. Interface and Register Mapping                                     | 63  |

| Figure 13. ACL Table Access                                                   |     |

| Figure 14. RGMII v2.0 Specification (Figure3-Multiplexing and Timing Diagram) |     |

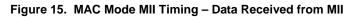

| Figure 15. MAC Mode MII Timing – Data Received from MII                       | 144 |

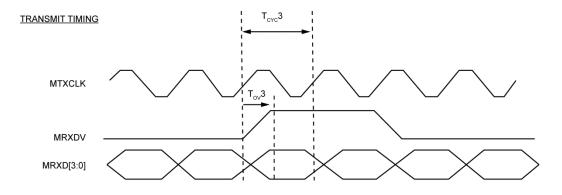

| Figure 16. MAC Mode MII Timing – Data Transmitted from MII                    | 144 |

| Figure 17. PHY Mode MII Timing – Data Received from MII                       |     |

| Figure 18. PHY Mode MII Timing – Data Transmitted from MII                    | 145 |

| Figure 19. RMII Timing – Data Received from RMII                              | 146 |

| Figure 20. RMII Timing – Data Transmitted to RMII                             |     |

| Figure 21. SPI Input Timing                                                   | 147 |

| Figure 22. Auto-Negotiation Timing                                            |     |

| Figure 23. MDC/MDIO Timing                                                    |     |

| Figure 27. Reset Timing                                                       | 150 |

| Figure 28. Recommended Reset Circuit                                          |     |

| Figure 29. Recommended Circuit for Interfacing with CPU/FPGA Reset            | 151 |

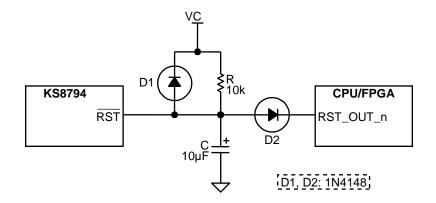

| Figure 30. 64-Pin (8mm x 8mm) QFN Package                                     | 153 |

## List of Tables

| Table 1. MDI/MDI-X Pin Definitions                                            |    |

|-------------------------------------------------------------------------------|----|

| Table 2. Internal Function Block Status                                       |    |

| Table 3. Available Interfaces                                                 |    |

| Table 4. SPI Connections                                                      |    |

| Table 5. MII Management Interface Frame Format                                |    |

| Table 6. Signals of RGMII/MII/RMII                                            |    |

| Table 7. Port 4 SW4-RGMII Connection                                          |    |

| Table 8. Port 4 SW4-RGMII Clock Delay Configuration hwit Connection Partner.= |    |

| Table 9. Port 4 SW4-MII Connection                                            |    |

| Table 10. Port 4 SW4-RMII Connection                                          |    |

| Table 11. Tail Tag Rules                                                      |    |

| Table 12. FID+DA Look-Up in the VLAN Mode                                     |    |

| Table 13. FID+SA Look-Up in the VLAN Mode                                     |    |

| Table 14. 10/100/1000Mbps Rate Selection for the Rate limit                   | 55 |

| Table 15. Mapping of Functional Areas within the Address Space                | 63 |

| Table 16. Static MAC Address Table                                            |    |

| Table 17. VLAN Table                                                          |    |

| Table 18. VLAN ID and Indirect Registers                                      |    |

| Table 19. Dynamic MAC Address Table                                           |    |

| Table 20. PME Indirect Registers                                              |    |

| Table 21. ACL Indirect Registers for 14 Bytes ACL Rules                       |    |

| Table 22. Temporal storage for 14 Bytes ACL Rules                             |    |

| Table 23. ACL Read and Write Control                                          |    |

| Table 24. Port 1 MIB Counter Indirect Memory Offerts                          |    |

| Table 25. Format of "Per Port" MIB Counter                                    |    |

| Table 26. All Port Dropped Packet MIB Counters                                |    |

| Table 27. Format of Per Port RX/TX Total Bytes MIB Counter                    |    |

| Table 28. Format of "All Dropped Packet" MIB Counter                          |    |

| Table 29. RGMII v2.0 Specification (Timing Specifics from Table 2)            |    |

| Table 30. MAC Mode MII Timing Parameters                                      |    |

| Table 31. PHY Mode MII Timing Parameters                                      |    |

| Table 32. RMII Timing Parameters                                              |    |

| Table 33. SPI Input Timing Parameters                                         |    |

| Table 34. Auto-Negotiation Timing Parameters                                  |    |

| Table 35. MDC/MDIO Typical Timing Parameters                                  |    |

| Table 36. Reset Timing Parameters                                             |    |

| Table 37. Transformer Selection Criteria                                      |    |

| Table 38. Qualified Magnetic Vendors                                          |    |

| Table 39. Typical Reference Crystal Characteristics                           |    |

|                                                                               |    |

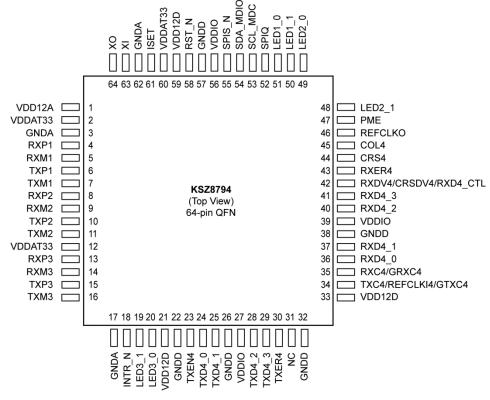

## **Pin Configuration**

### **Pin Description**

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function                                                                                                                                                                                                                                                 |  |

|------------|----------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | VDD12A   | Р                   |      | 1.2V Core Power                                                                                                                                                                                                                                              |  |

| 2          | VDDAT    | Р                   |      | 3.3V Analog Power                                                                                                                                                                                                                                            |  |

| 3          | GNDA     | GND                 |      | Analog Ground                                                                                                                                                                                                                                                |  |

| 4          | RXP1     | I                   | 1    | Port 1 Physical receive signal + (differential)                                                                                                                                                                                                              |  |

| 5          | RXM1     | I                   | 1    | Port 1 Physical receive signal - (differential)                                                                                                                                                                                                              |  |

| 6          | TXP1     | 0                   | 1    | Port 1 Physical transmit signal + (differential)                                                                                                                                                                                                             |  |

| 7          | TXM1     | 0                   | 1    | Port 1 Physical transmit signal - (differential)                                                                                                                                                                                                             |  |

| 8          | RXP2     | I                   | 2    | Port 2 Physical receive signal + (differential)                                                                                                                                                                                                              |  |

| 9          | RXM2     | I                   | 2    | Port 2 Physical receive signal - (differential)                                                                                                                                                                                                              |  |

| 10         | TXP2     | 0                   | 2    | Port 2 Physical transmit signal + (differential)                                                                                                                                                                                                             |  |

| 11         | TXM2     | 0                   | 2    | Port 2 Physical transmit signal - (differential)                                                                                                                                                                                                             |  |

| 12         | VDDAT    | Р                   |      | 3.3V Analog Power                                                                                                                                                                                                                                            |  |

| 13         | RXP3     | I                   | 3    | Port 3 Physical receive signal + (differential)                                                                                                                                                                                                              |  |

| 14         | RXM3     | I                   | 3    | Port 3 Physical receive signal - (differential)                                                                                                                                                                                                              |  |

| 15         | TXP3     | 0                   | 3    | Port 3 Physical transmit signal + (differential)                                                                                                                                                                                                             |  |

| 16         | TXM3     | 0                   | 3    | Port 3 Physical transmit signal – (differential)                                                                                                                                                                                                             |  |

| 17         | GNDA     | GND                 |      | Analog Ground.                                                                                                                                                                                                                                               |  |

| 18         | INTR_N   | Opu                 |      | Interrupt: Active low<br>This pin is Open-Drain output pin.                                                                                                                                                                                                  |  |

| 19         | LED3_1   | lpu/O               | 3    | Port 3 LED Indicator 1<br>See global Register 11 bits [5:4] for details.<br>Strap Option: Switch Port 4 GMAC4 Interface Mode Select by<br>LED3[1:0]<br>00 = MII for SW4-MII<br>01 = RMII for SW4-RMII<br>10 = Reserved<br>11 = RGMII for SW4-RGMII (Default) |  |

| 20         | LED3_0   | lpu/O               | 3    | Port 3 LED Indicator 0<br>See global Register 11 bits [5:4] for details.<br>Strap Option: see LED3_1                                                                                                                                                         |  |

| 21         | VDD12D   | Р                   |      | 1.2V Core Power.                                                                                                                                                                                                                                             |  |

| 22         | GNDD     | GND                 |      | Digital Ground.                                                                                                                                                                                                                                              |  |

Notes:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

GND = Ground.

Ipu = Input w/internal pull-up. Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise. Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

OTRI = Output tristated. PU = Strap pin pull-up.

PD = Strap pull-down.

NC = No connect or tie to ground for this product only.

| Pin Number | Pin Name                | Type <sup>(1)</sup> | Port | Pin Function                                                                                                                                                                                                                                                                                |  |

|------------|-------------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 23         | TXEN4/TXD4_CTL          | lpd                 | 4    | MII/RMII:<br>Port 4 Switch transmit enable.<br>RGMII:<br>Transmit data control.                                                                                                                                                                                                             |  |

| 24         | TXD4_0                  | Ipd                 | 4    | RGMII/MII/RMII:<br>Port 4 Switch transmit bit [0].                                                                                                                                                                                                                                          |  |

| 25         | TXD4_1                  | lpd                 | 4    | RGMII/MII/RMII:<br>Port 4 Switch transmit bit [1].                                                                                                                                                                                                                                          |  |

| 26         | GNDD                    | GND                 |      | Digital Ground.                                                                                                                                                                                                                                                                             |  |

| 27         | VDDIO                   | Р                   |      | 3.3V, 2.5V or 1.8V digital VDD for digital I/O circuitry.                                                                                                                                                                                                                                   |  |

| 28         | TXD4_2                  | lpd                 | 4    | RGMII/MII:<br>Port 4 Switch transmit bit [2].<br>RMII:<br>No connection.                                                                                                                                                                                                                    |  |

| 29         | TXD4_3                  | lpd                 | 4    | RGMII/MII:<br>Port 4 Switch transmit bit [3].<br>RMII:<br>No connection.                                                                                                                                                                                                                    |  |

| 30         | TXER4                   | lpd                 | 4    | MII:<br>Port 4 Switch transmit error.<br>RGMII/RMII:<br>No connection.                                                                                                                                                                                                                      |  |

| 31         | NC                      | NC                  |      | No Connect                                                                                                                                                                                                                                                                                  |  |

| 32         | GNDD                    | GND                 |      | Digital Ground                                                                                                                                                                                                                                                                              |  |

| 33         | VDD12D                  | Р                   |      | 1.2V Core Power                                                                                                                                                                                                                                                                             |  |

| 34         | TXC4/REFCLKI4<br>/GTXC4 | I/O                 | 4    | Port 4 Switch GMAC4 Clock Pin<br>MII: 2.5/25MHz clock, PHY mode is output, MAC mode is input.<br>RMII: Input for receiving 50MHz clock in normal mode<br>RGMII: Input 125MHz clock with falling and rising edge to latch data<br>the transmit.                                              |  |

| 35         | RXC4/GRXC4              | I/O                 | 4    | Port 4 Switch GMAC4 Clock Pin         MII: 2.5/25MHz clock, PHY mode is output, MAC mode is input.         RMII: Output 50MHz reference clock for the receiving/transmit in the clock mode.         RGMII: Output 125MHz clock with falling and rising edge to latch dat for the receiving. |  |

| 36         | RXD4_0                  | lpd/O               | 4    | RGMII/MII/RMII:<br>Port 4 Switch receive bit [0].                                                                                                                                                                                                                                           |  |

| 37         | RXD4_1                  | lpd/O               | 4    | RGMII/MII/RMII:<br>Port 4 Switch receive bit [1].                                                                                                                                                                                                                                           |  |

| 38         | GNDD                    | GND                 |      | Digital Ground.                                                                                                                                                                                                                                                                             |  |

| 39         | VDDIO                   | Р                   |      | 3.3V, 2.5V or 1.8V digital VDD for digital I/O circuitry.                                                                                                                                                                                                                                   |  |

| 40         | RXD4_2                  | lpd/O               | 4    | RGMII/MII:<br>Port 4 Switch receive bit [2].<br>RMII:<br>No connection.                                                                                                                                                                                                                     |  |

| Pin Number | Pin Name                  | Type <sup>(1)</sup> | Port | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|------------|---------------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 41         | RXD4_3                    | lpd/O               | 4    | RGMII/MII:<br>Port 4 Switch receive bit [3].<br>RMII:<br>No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 42         | RXDV4/CRSDV4<br>/RXD4_CTL | lpd/O               | 4    | MII:<br>RXDV4 is for Port 4 Switch GMII/MII receive data valid.<br>RMII:<br>CRSDV4 is for Port 4 RMII carrier sense/receive data valid output.<br>RGMII:<br>RXD4_CTL is for Port 4 RGMII receive data control                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 43         | RXER4                     | lpd/O               | 4    | MII:<br>Port 4 Switch receives error.<br>RGMII/RMII:<br>No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 44         | CRS4                      | lpd/O               | 4    | MII:<br>Port 4 Switch MII modes carrier sense.<br>RGMII/RMII:<br>No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 45         | COL4                      | lpd/O               | 4    | MII:<br>Port 4 Switch MII collision detects.<br>RGMII/RMII:<br>No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 46         | REFCLKO                   | lpu/O               |      | <b>25MHz Clock Output (Option)</b><br>Controlled by the strap pin LED2_0.<br>Default is enabled, it is better to disabled it if not be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 47         | PME_N                     | I/O                 |      | Power Management Event<br>This output signal indicates that a Wake On LAN event has been<br>detected as a result of a Wake-Up frame being detected. The<br>KSZ8794CNX is requesting the system to wake up from low power<br>mode. Its assertion polarity is programmable with the default polarity<br>to be active low.                                                                                                                                                                                                                                                                                                                                         |  |

| 48         | LED2_1                    | lpu/O               | 2    | Port 2 LED Indicator 1         See global register 11 bits [5:4] for details.         Strap Option: Port 4 MII and RMII Modes Select         When Port 4 is MII mode:         PU = MAC mode.         PD = PHY mode.         When Port 4 is RMII mode:         PU = Clock mode in RMII, using 25MHz OSC clock and provide         50MHz RMII clock from pin RXC4.         PD = Normal mode in RMII, the TXC4/REFCLKI4 pin on the Port 4         RMII will receive an external 50MHz clock.         Note: Port 4 also can use either an internal or external clock in RMII mode         based on this strap pin or the setting of the Register 86 (0x56) bit [7]. |  |

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|------------|----------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 49         | LED2_0   | lpu/O               | 2    | Port 2 LED Indicator 0<br>See global register 11 bits [5:4] for details.<br>Strap Option: REFCLKO Enable<br>PU = REFCLK_O (25MHz) is enabled. (Default)<br>PD = REFCLK_O is disabled<br>Note: It is better to disable this 25MHz clock if do not provide an extra 25MHz<br>clock for system.                                                                                                                                                                                             |  |

| 50         | LED1_1   | lpu/O               | 1    | <ul> <li>Port 1 LED Indicator 1.</li> <li>See global Register 11 bits [5:4] for details.</li> <li>Strap Option: PLL Clock Source Select</li> <li>PU = Still use 25MHz clock from XI/XO pin even though it is in Port RMII normal mode.</li> <li>PD = Use external clock from TXC4 in Port 4 RMII normal mode.</li> <li>Note: If received clock in Port 4 RMII normal mode has bigger clock jitter, s can select to use the 25MHz crystal/Oscillator as switch's clock source.</li> </ul> |  |

| 51         | LED1_0   | lpu/O               | 1    | Port 1 LED Indicator 0         See global Register 11 bits [5:4] for details.         Strap Option: Speed Select in RGMII         PU = 1Gbps in RGMII. (Default)         PD = 10/100Mbps in RGMII.         Note: Programmable through internal registers also.                                                                                                                                                                                                                           |  |

| 52         | SPIQ     | lpd/O               | All  | SPI Serial Data Output in SPI Slave Mode         Strap Option: Serial Bus Configuration         PD = SPI slave mode.         PU = MDC/MDIO mode.         Note: An external pull-up or pull-down resistor is required.                                                                                                                                                                                                                                                                    |  |

| 53         | SCL_MDC  | lpu                 | All  | Clock for SPI or MDC/MDIO Interfaces<br>Input clock up to 50MHz in SPI slave mode.<br>Input clock up to 25MHz in MDC/MDIO for MIIM access.                                                                                                                                                                                                                                                                                                                                               |  |

| 54         | SDA_MDIO | lpu/O               | All  | Data Line for SPI or MDC/MDIO Interfaces<br>Serial data input in SPI slave mode.<br>MDC/MDIO interface input/output data line.                                                                                                                                                                                                                                                                                                                                                           |  |

| 55         | SPIS_N   | lpu                 | All  | SPI Interface Chip Select<br>When SPIS_N is high, the KSZ8794CNX is deselected and SPIQ is<br>held in the high impedance state. A high-to-low transition initiates the<br>SPI data transfer. This pin is active low.                                                                                                                                                                                                                                                                     |  |

| 56         | VDDIO    | Р                   |      | 3.3V, 2.5V or 1.8V digital VDD for digital I/O circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 57         | GNDD     | GND                 |      | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 58         | RST_N    | lpu                 |      | <b>Reset</b><br>This active low signal resets the hardware in the device. See the timing<br>requirements in the Timing Diagram Section.                                                                                                                                                                                                                                                                                                                                                  |  |

| 59         | VDD12D   | Р                   |      | 1.2V Core Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 60         | VDDAT    | Р                   |      | 3.3V Analog Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port             | Pin Function                                                                                                                                                                                                                                                               |

|------------|----------|---------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61         | ISET     |                     |                  | <b>Transmit Output Current Set</b><br>This pin configures the physical transmit output current.<br>It should be connected to GND thru a $12.4k\Omega$ 1% resistor.                                                                                                         |

| 62         | GNDA     | GND                 | D Analog Ground. |                                                                                                                                                                                                                                                                            |

| 63         | XI       | I                   |                  | <b>Crystal Clock Input/Oscillator Input</b><br>When using a 25MHz crystal, this input is connected to one end of the crystal circuit. When using a 3.3V oscillator, this is the input from the oscillator.<br>The crystal or oscillator should have a tolerance of ±50ppm. |