# DS32EL0124, DS32ELX0124 125 MHz - 312.5 MHz FPGA-Link Deserializer with DDR LVDS **Parallel Interface**

Check for Samples: DS32EL0124, DS32ELX0124

# **FEATURES**

- 5-bit DDR LVDS Parallel Data Interface

- **Programmable Receive Equalization**

- Selectable DC-Balance Decoder

- Selectable De-Scrambler

- **Remote Sense for Automatic Detection and** Negotiation of Link Status

- **No External Receiver Reference Clock** • Required

- **LVDS Parallel Interface**

- Programmable LVDS Output Clock Delay

- Supports Output Data-Valid Signaling

- Supports Keep-Alive Clock Output

- **On Chip LC VCOs**

- Redundant Serial Input (ELX device only) •

- Retimed Serial Output (ELX device only)

- **Configurable PLL Loop Bandwidth** ٠

- **Configurable via SMBus** •

- Loss of Lock and Error Reporting •

- 48-pin WQFN Package with Exposed DAP •

# APPLICATIONS

- Imaging: Industrial, Medical Security, Printers

- **Displays: LED Walls, Commercial** •

- Video Transport ٠

- **Communication Systems** ٠

- **Test and Measurement** ٠

- Industrial Bus

# DESCRIPTION

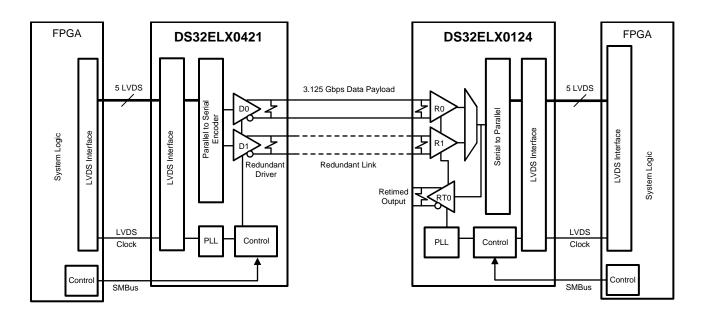

The DS32EL0124/DS32ELX0124 integrates clock and data recovery modules for high-speed serial communication over FR-4 printed circuit board backplanes, balanced cables, and optical fiber. This easy-to-use chipset integrates advanced signal and clock conditioning functions, with an FPGA friendly interface.

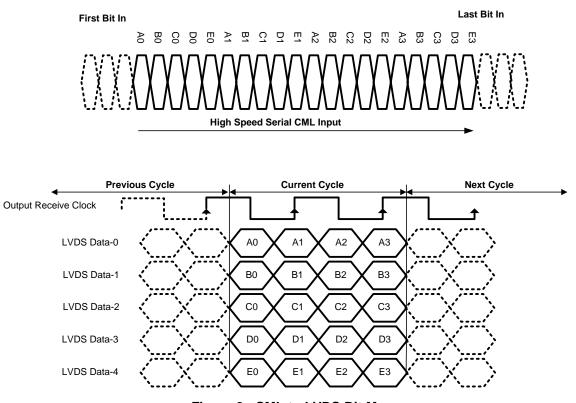

The DS32EL0124/DS32ELX0124 deserializes up to 3.125 Gbps of high speed serial data to 5 LVDS outputs without the need for an external reference clock. With DC-balance decoding enabled, the application payload of 2.5 Gbps is deserialized to 4 LVDS outputs.

The DS32EL0124/DS32ELX01214 deserializers feature a remote sense capability to automatically signal link status conditions to its companion DS32EL0421/ELX0421 serializers without requiring an additional feedback path.

The parallel LVDS interface of these devices reduce FPGA I/O pins, board trace count and alleviates EMI issues, when compared to traditional single-ended wide bus interfaces.

The DS32EL0124/ELX0124 is programmable through a SMBus interface as well as through control pins.

## Table 1. Key Specifications

|                                                   | VALUE         | UNIT |

|---------------------------------------------------|---------------|------|

| Serial data rate                                  | 1.25 to 3.125 | Gbps |

| DDR parallel clock                                | 125 to 312.5  | MHz  |

| Temperature range                                 | -40 to +85    | °C   |

| > 8 kV ESD (HBM) protection                       |               |      |

| 0.5 UI Minimum Input Jitter Tolerance (1.25 Gbps) |               |      |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

Texas Instruments

# **Typical Application**

Copyright © 2008–2012, Texas Instruments Incorporated

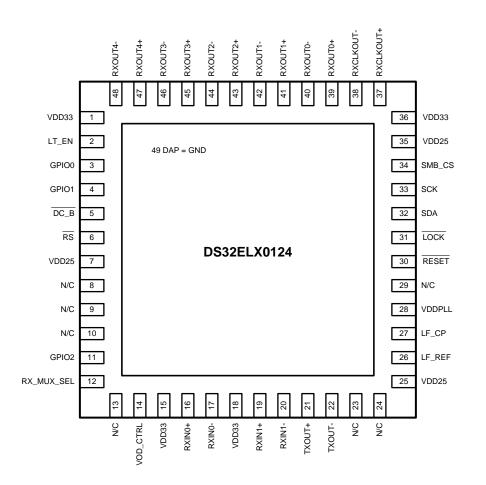

**Connection Diagrams**

www.ti.com

SNLS284J-MAY 2008-REVISED OCTOBER 2012

#### **RXCLKOUT+ RXCLKOUT-**RXOUT3+ RXOUT2+ **RXOUT1-**RXOUT0-RXOUT0+ RXOUT4-**RXOUT4+** RXOUT3-RXOUT2-RXOUT1+ 48 47 38 37 46 43 42 4 40 39 45 44 36 VDD33 1 VDD33 35 N/C 2 VDD25 49 DAP = GND GPIO0 3 34 SMB\_CS GPIO1 4 33 SCK DC\_B 32 SDA 5 31 RS 6 LOCK DS32EL0124 RESET VDD25 7 30 N/C N/C 8 29 N/C 9 28 VDDPLL N/C 10 27 LF\_CP GPIO2 11 26 LF\_REF N/C 12 25 VDD25 20 13 14 2 16 <u>∞</u> <u>\_</u> 22 33 24 VDD33 VDD33 N/C N/C N/C RXIN0-N/C N/C N/C N/C N/C RXIN0+

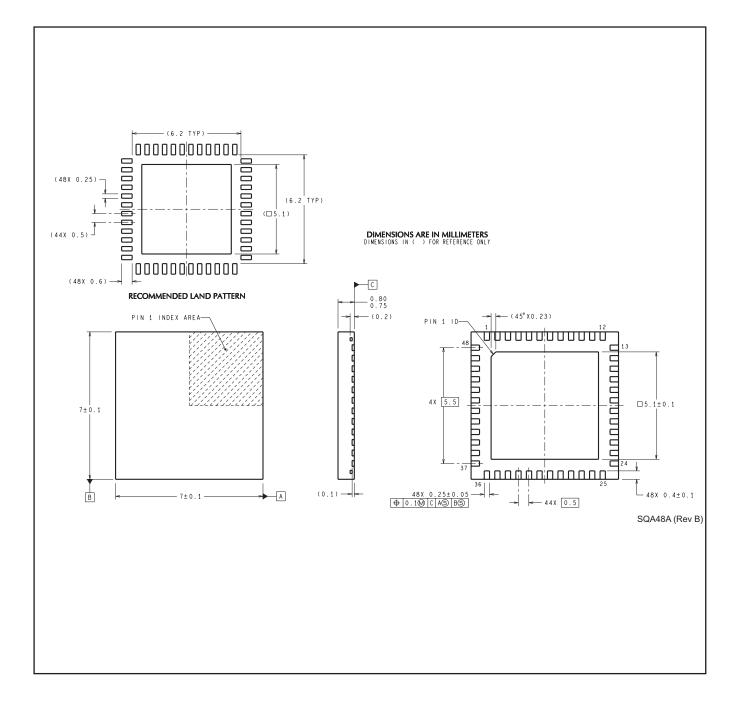

Figure 1. WQFN Package Package Number RHS0048A

www.ti.com

SNLS284J-MAY 2008-REVISED OCTOBER 2012

#### Figure 2. WQFN Package Package Number RHS0048A

#### **PIN DESCRIPTIONS**

| Pin Name               | Pin Number                                | I/O, Type | Description                                                                                                                                                                             |

|------------------------|-------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD33                  | 1, 15, 18, 36                             | I, VDD    | 3.3V supply                                                                                                                                                                             |

| VDD25                  | 7, 25, 35                                 | I, VDD    | 2.5V supply                                                                                                                                                                             |

| VDD_PLL                | 28                                        | I, VDD    | 3.3V supply                                                                                                                                                                             |

| LF_CP                  | 27                                        | Analog    | Loop filter capacitor connection                                                                                                                                                        |

| LF_REF                 | 26                                        | Analog    | Loop filter ground reference                                                                                                                                                            |

| Exposed Pad            | 49                                        | GND       | Exposed Pad must be connected to GND by 9 vias.                                                                                                                                         |

| CML I/O                |                                           |           |                                                                                                                                                                                         |

| RxIN0+<br>RxIN0-       | 16<br>17                                  | I, CML    | Non-inverting and inverting high speed CML differential inputs of the deserializer. These inputs are internally terminated.                                                             |

| RxIN1+<br>RxIN1-       | 19<br>20                                  | I, CML    | <b>DS32ELX0124 only.</b> Non-inverting and inverting high speed CML differential inputs of the deserializer. These inputs are internally terminated.                                    |

| TxOUT+<br>TxOUT-       | 21<br>22                                  | O, CML    | <b>DS32ELX0124 only.</b> Retimed serialized high speed output. Non-inverting and inverting speed CML differential outputs of the deserializer. These outputs are internally terminated. |

| LVDS Parallel          | Data Bus                                  | l.        |                                                                                                                                                                                         |

| RxCLKOUT+<br>RxCLKOUT- | 37<br>38                                  | O, LVDS   | Deserializer output clock. RxCLKOUT+/- are the non-inverting and inverting LVDS recovered clock output pins.                                                                            |

| RxOUT[0:4]+/-          | 39, 40, 41, 42, 43, 44, 45,<br>46, 47, 48 | O, LVDS   | Deserializer output data. RxOUT[0:4]+/- are the non-inverting and inverting LVDS deserialized output data pins.                                                                         |

4

Copyright © 2008–2012, Texas Instruments Incorporated

SNLS284J-MAY 2008-REVISED OCTOBER 2012

#### www.ti.com

## **PIN DESCRIPTIONS (continued)**

| Pin Name     | Pin Number                                             | I/O, Type   | Description                                                                                                                                                                                                                                                             |

|--------------|--------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Pins |                                                        |             |                                                                                                                                                                                                                                                                         |

| LT_EN        | 2                                                      | I, LVCMOS   | <b>DS32ELX0124 only.</b> When held high, retimed serialized high speed output is enabled.                                                                                                                                                                               |

| RX_MUX_SEL   | 12                                                     | I, LVCMOS   | <b>DS32ELX0124 only.</b> RX_MUX_SEL selects the input of the deserializer.<br>0 = RxIN0+/- selected<br>1 = RxIN1+/- selected                                                                                                                                            |

| VOD_CTRL     | 14                                                     | I, LVCMOS   | <b>DS32ELX0124 only.</b> VOD control. The deserializer loop through output amplitude can be adjusted by connecting this pin to a pull-down resistor. The value of the pull-down resistor determines the VOD. See LOOP THROUGH DRIVER LAUNCH AMPLITUDE for more details. |

| DC_B<br>RS   | 5<br>6                                                 | I, LVCMOS   | DC-balance and Remote Sense pins. See Applications Information for device behavior.                                                                                                                                                                                     |

| RESET        | 30                                                     | I, LVCMOS   | Reset pin. When held low, reset the device.<br>0 = Device Reset<br>1 = Normal operation                                                                                                                                                                                 |

| LOCK         | 31                                                     | O, LVCMOS   | Lock indication output. pin goes low when the deserializer is locked to the incoming data stream and begins to output data and clock on RxOUT and RxCLKOUT respectively.<br>0 = Deserializer locked<br>1 = Deserializer not locked                                      |

| SMBus        |                                                        |             |                                                                                                                                                                                                                                                                         |

| SCK          | I, SMBus                                               | 33          | SMBus compatible clock.                                                                                                                                                                                                                                                 |

| SDA          | I/O, SMBus                                             | 32          | SMBus compatible data line.                                                                                                                                                                                                                                             |

| SMB_CS       | I, SMBus                                               | 34          | SMBus chip select. When held high, SMBus management control is enabled.                                                                                                                                                                                                 |

| Other        |                                                        |             |                                                                                                                                                                                                                                                                         |

| GPIO0        | 3                                                      | I/O, LVCMOS | Software configurable IO pins.                                                                                                                                                                                                                                          |

| GPIO1        | 4                                                      | I/O, LVCMOS | Software configurable IO pins.                                                                                                                                                                                                                                          |

| GPIO2        | 11                                                     | I/O, LVCMOS | Software configurable IO pins.                                                                                                                                                                                                                                          |

| NC           | 2 ,8, 9, 10, 12, 13, 14, 19,<br>20, 21, 22, 23, 24, 29 | Misc.       | No Connect, for DS32EL0124                                                                                                                                                                                                                                              |

|              | 8, 9, 10, 13, 23, 24, 29                               | Misc        | No Connect, for DS32ELX0124                                                                                                                                                                                                                                             |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings<sup>(1)(2)</sup>

| 5                                   |                                     |

|-------------------------------------|-------------------------------------|

| Supply Voltage (V <sub>DD33</sub> ) | -0.3V to +4V                        |

| Supply Voltage (V <sub>DD25</sub> ) | -0.3V to +3.0V                      |

| LVCMOS Input Voltage                | -0.3V to (V <sub>DD33</sub> + 0.3V) |

| LVCMOS Output Voltage               | -0.3V to (V <sub>DD33</sub> + 0.3V) |

| CML Input/Output Voltage            | -0.3V to 3.6V                       |

| LVDS Output Voltage                 | -0.3V to +3.6V                      |

| Junction Temperature                | +125°C                              |

| Storage Temperature Range           | −65°C to +150°C                     |

| Lead Temperature Range              |                                     |

| Soldering (4 sec.)                  | +260°C                              |

| Package Thermal Resistance          |                                     |

| θ <sub>JA</sub>                     | +25.0°C/W                           |

| ESD Susceptibility                  |                                     |

| HBM                                 | ≥8 kV                               |

|                                     |                                     |

(1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

## **Recommended Operating Conditions**

|                                                  | Min   | Тур  | Max   | Units             |

|--------------------------------------------------|-------|------|-------|-------------------|

| Supply Voltage (V <sub>DD33</sub> )              | 3.135 | 3.3  | 3.465 | V                 |

| Supply Voltage (V <sub>DD25</sub> )              | 2.375 | 2.5  | 2.625 | V                 |

| Supply Noise Amplitude from 10 Hz to 50 MHz      |       |      | 100   | mV <sub>P-P</sub> |

| Ambient Temperature (T <sub>A</sub> )            | -40   | +25  | +85   | °C                |

| SMBus Pull–Up Resistor to V <sub>SDD</sub> Value |       | 1000 |       | Ω                 |

#### **Table 2. Power Supply Characteristics**

| Symbol            | Parameter                                           | Condition  | Min | Тур | Max | Unit |

|-------------------|-----------------------------------------------------|------------|-----|-----|-----|------|

| I <sub>DD25</sub> | 2.5V supply current                                 | 1.25 Gbps  |     | 50  | 59  | -    |

|                   | Loop Through Driver Disabled                        | 2.5 Gbps   |     | 62  | 73  |      |

|                   |                                                     | 3.125 Gbps |     | 69  | 79  | 0    |

|                   | 2.5V supply current                                 | 1.25 Gbps  |     | 88  | 99  | mA   |

|                   | Loop Through Driver Enabled                         | 2.5 Gbps   |     | 100 | 112 |      |

|                   |                                                     | 3.125 Gbps |     | 107 | 120 |      |

| I <sub>DD33</sub> | 3.3V supply current<br>Loop Through Driver Disabled | 1.25 Gbps  |     | 105 | 121 |      |

|                   |                                                     | 2.5 Gbps   |     | 105 | 121 | mA   |

|                   |                                                     | 3.125 Gbps |     | 105 | 121 |      |

|                   | 3.3V supply current<br>Loop Through Driver Enabled  | 1.25 Gbps  |     | 111 | 127 |      |

|                   |                                                     | 2.5 Gbps   |     | 111 | 127 |      |

|                   |                                                     | 3.125 Gbps |     | 111 | 127 |      |

| PD                | Power Consumption                                   | 1.25 Gbps  |     | 475 | 560 |      |

|                   | Loop Through Driver Disabled                        | 2.5 Gbps   |     | 500 | 600 |      |

|                   |                                                     | 3.125 Gbps |     | 520 | 620 |      |

|                   | Power Consumption                                   | 1.25 Gbps  |     | 590 | 690 | mW   |

|                   | Loop Through Driver Enabled                         | 2.5 Gbps   |     | 620 | 730 |      |

|                   |                                                     | 3.125 Gbps |     | 640 | 750 | ]    |

www.ti.com

#### **LVCMOS Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. Applies to LT\_EN, GPIO0, GPIO1, GPIO2, RX\_MUX\_SEL, DC\_B, RESET, RS, LOCK. <sup>(1) (2) (3)</sup>

| Symbol          | Parameter                    | Conditions                                  | Min | Тур  | Max             | Units |

|-----------------|------------------------------|---------------------------------------------|-----|------|-----------------|-------|

| V <sub>IH</sub> | High Level Input Voltage     |                                             | 2.0 |      | V <sub>DD</sub> | V     |

| V <sub>IL</sub> | Low Level Input Voltage      |                                             | GND |      | 0.8             | V     |

| V <sub>OH</sub> | High Level Output Voltage    | I <sub>OH</sub> = -2mA                      | 2.7 | 3.2  |                 | V     |

| V <sub>OL</sub> | Low Level Output Voltage     | $I_{OL} = 2mA$                              |     |      | 0.3V            | V     |

| V <sub>CL</sub> | Input Clamp Voltage          | I <sub>CL</sub> = −18 mA                    |     | -0.9 | -1.5            | V     |

| I <sub>IN</sub> | Input Current                | $V_{IN} = 0.4V, 2.5V, \text{ or } V_{DD33}$ | -40 |      | 40              | μA    |

| I <sub>OS</sub> | Output Short Circuit Current | $V_{OUT} = 0V$                              |     | -45  |                 | mA    |

(1) The Electrical and Timing Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

(2) Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except V<sub>OD</sub> and ΔV<sub>OD</sub>.

(3) Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

(4) Output short circuit current (I<sub>OS</sub>) is specified as magnitude only, minus sign indicates direction only.

# **SMBus Electrical Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. <sup>(1) (2)</sup>

| Symbol              | Parameter                      | Conditions       | Min   | Тур  | Max       | Units |

|---------------------|--------------------------------|------------------|-------|------|-----------|-------|

| V <sub>SIL</sub>    | Data, Clock Input Low Voltage  |                  |       |      | 0.8       | V     |

| V <sub>SIH</sub>    | Data, Clock Input High Voltage |                  | 2.1   |      | $V_{SDD}$ | V     |

| $V_{SDD}$           | Nominal Bus Voltage            |                  | 2.375 |      | 3.465     | V     |

| I <sub>SLEAKB</sub> | Input Leakage Per Bus Segment  | SCK and SDA pins |       | ±200 |           | μA    |

| I <sub>SLEAKP</sub> | Input Leakage Per Pin          |                  |       | ±10  |           | μA    |

| C <sub>SI</sub>     | Capacitance for SDA and SCK    |                  |       | 10   |           | pF    |

(1) The Electrical and Timing Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

(2) Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

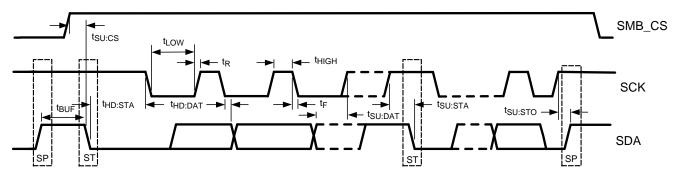

# **SMBus Timing Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. <sup>(1) (2)</sup>

| Symbol              | Parameter                                                                                   | Conditions | Min | Тур | Мах | Units |

|---------------------|---------------------------------------------------------------------------------------------|------------|-----|-----|-----|-------|

| f <sub>SMB</sub>    | Bus Operating Frequency                                                                     |            | 10  |     | 100 | kHz   |

| t <sub>BUF</sub>    | Bus free time between top and start condition                                               |            | 4.7 |     |     | μs    |

| t <sub>HD:STA</sub> | Hold time after (repeated) start condition. After this period, the first clock is generated |            | 4.0 |     |     | μs    |

| t <sub>SU:STA</sub> | Repeated Start Condition Setup Time                                                         | (3)        | 4.7 |     |     | μs    |

| t <sub>HD:DAT</sub> | Data Hold Time                                                                              |            | 300 |     |     | ns    |

| t <sub>SU:DAT</sub> | Data Setup Time                                                                             | (3)        | 250 |     |     | ns    |

| t <sub>LOW</sub>    | Clock Low Time                                                                              |            | 4.7 |     |     | μs    |

| t <sub>HIGH</sub>   | Clock High Time                                                                             |            | 4.0 |     | 50  | μs    |

| t <sub>SU:CS</sub>  | SMB_CS Setup Time                                                                           | (3)        | 30  |     |     | ns    |

(1) The Electrical and Timing Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

(2) Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Product Folder Links: DS32EL0124 DS32ELX0124

(3) Parameter is guaranteed by characterization and is not tested at production.

Copyright © 2008–2012, Texas Instruments Incorporated

www.ti.com

# **SMBus Timing Specifications (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol             | Parameter                                                   | Conditions | Min | Тур | Max | Units |

|--------------------|-------------------------------------------------------------|------------|-----|-----|-----|-------|

| t <sub>HS:CS</sub> | SMB_CS Hold Time                                            | (3)        | 100 |     |     | ns    |

| t <sub>POR</sub>   | Time in which the device must be operational after power on | (3)        |     |     | 500 | ms    |

# **LVDS Electrical Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol          | Parameter                                                      | Conditions                                                     | Min   | Тур  | Max   | Units |

|-----------------|----------------------------------------------------------------|----------------------------------------------------------------|-------|------|-------|-------|

| V <sub>OD</sub> | Differential Output Voltage                                    | $R_L = 100\Omega$                                              | 230   |      | 310   | mV    |

| $\Delta V_{OD}$ | Changes in V <sub>OD</sub> between complimentary output states |                                                                |       |      | 35    | mV    |

| V <sub>OS</sub> | Offset Voltage                                                 |                                                                | 1.125 | 1.25 | 1.375 | V     |

| $\Delta V_{OS}$ | Change in $V_{OS}$ between complimentary states                |                                                                |       |      | 35    | mV    |

| I <sub>OS</sub> | Output Short Circuit Current                                   | $\bigvee_{\substack{\text{(3)}\\(3)}} = 0V, \ R_L = 100\Omega$ | -50   |      |       | mA    |

(1) The Electrical and Timing Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

(2) Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

(3) Output short circuit current (I<sub>OS</sub>) is specified as magnitude only, minus sign indicates direction only.

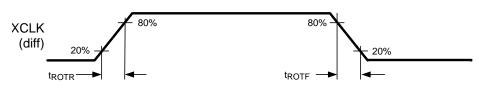

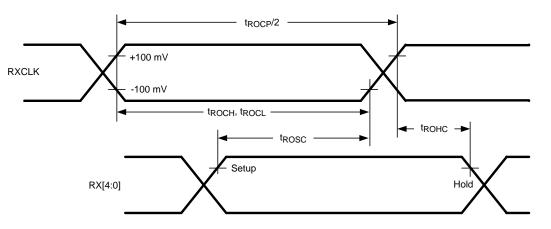

# **LVDS Timing Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. <sup>(1) (2)</sup>

| Symbol            | Parameter                        | Conditions | Min | Тур | Max | Units |

|-------------------|----------------------------------|------------|-----|-----|-----|-------|

| t <sub>ROTR</sub> | LVDS low-to-high transition time |            |     | 300 |     | ps    |

| t <sub>ROTF</sub> | LVDS high-to-low transition time |            |     | 300 |     | ps    |

| t <sub>ROCP</sub> | LVDS output clock period         |            |     | 2T  |     | ns    |

| t <sub>RODC</sub> | RxCLKOUT Duty Cycle              |            | 45  | 50  | 55  | %     |

| t <sub>RBIT</sub> | LVDS output bit width            |            |     | Т   |     | ns    |

| t <sub>ROSC</sub> | RxOUT Setup to RxCLKOUT OUT      |            | 650 | 800 |     | ps    |

| t <sub>ROHC</sub> | RxOUT Hold to RxCLKOUT OUT       |            | 650 | 800 |     | ps    |

| t <sub>RODJ</sub> | LVDS Output Deterministic Jitter | RxCLKOUT   |     | 18  |     |       |

|                   |                                  | RxOUT0-4   |     | 43  |     | - ps  |

| t <sub>RORJ</sub> | LVDS Output Random Jitter        | RxCLKOUT   |     | 2.5 |     |       |

|                   |                                  | RxOUT0-4   |     | 2.5 |     | - ps  |

| t <sub>ROTJ</sub> | Peak-to-Peak LVDS Output Jitter  | RxCLKOUT   |     | 51  |     |       |

|                   |                                  | RxOUT0-4   |     | 70  |     | ps    |

- (3) Parameter is guaranteed by characterization and is not tested at production.

- 8 Submit Documentation Feedback

<sup>(1)</sup> The Electrical and Timing Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

<sup>(2)</sup> Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

www.ti.com

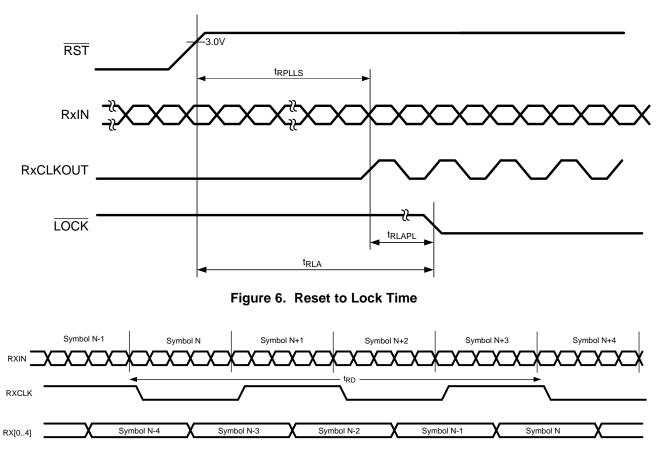

# LVDS Timing Specifications (continued)

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol            | Parameter              | Conditions                                         | Min | Тур | Max | Units |

|-------------------|------------------------|----------------------------------------------------|-----|-----|-----|-------|

| t <sub>RLA</sub>  | Deserializer Lock Time | (3)                                                |     |     |     |       |

|                   |                        | 1.25 Gbps                                          |     | 22  |     |       |

|                   |                        | 2.5 Gbps                                           |     | 90  |     | ms    |

|                   |                        | 3.125 Gbps                                         |     | 115 |     |       |

| t <sub>LVSK</sub> | LVDS Output Skew       | LVDS Differential Output Skew between + and - pins |     | 20  |     | ps    |

# **CML Input Timing Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. <sup>(1) (2)</sup>

| Symbol             | Parameter                             | Conditions                                                                                                                                                                                                                                                       | Min       | Тур                    | Max | Units |

|--------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|-----|-------|

| TOL <sub>JIT</sub> | Serial Input Jitter Tolerance         | $ \begin{array}{c} RJ = 0.18 \; UI \\ DJ = 0.37 \; UI \\ SJ \; \text{increased until failure} \\ 1.25 \; Gbps \\ f < 10 \; KHz \\ f > 1 \; MHz \\ \hline 2.5 \; Gbps \\ f < 10 \; KHz \\ f > 1 \; MHz \\ \hline 1 \; MHz \\ \hline f > 1 \; MHz \\ \end{array} $ |           | 30<br>0.5<br>50<br>0.3 |     | UI    |

|                    | 3.125 Gbps<br>f < 10 kHz<br>f > 1 MHz |                                                                                                                                                                                                                                                                  | 70<br>0.3 |                        |     |       |

(1) The Electrical and Timing Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

(2) Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

# **CML Input Electrical Specifications**

Over recommended operating supply and temperature ranges unless otherwise specified. <sup>(1) (2)</sup>

| Symbol          | Parameter                  | Conditions | Min  | Тур | Max  | Units |

|-----------------|----------------------------|------------|------|-----|------|-------|

| V <sub>ID</sub> | Differential input voltage | (3)        | 230  |     | 2200 | mV    |

| V <sub>IN</sub> | Single ended input voltage | (3)        | 115  |     | 1100 | mV    |

| I <sub>IN</sub> | Input Current              |            | -300 |     | 50   | μA    |

| R <sub>IT</sub> | Input Termination          |            | 84   | 100 | 116  | Ω     |

(1) The Electrical and Timing Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

(2) Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

(3) Parameter is guaranteed by characterization and is not tested at production.

www.ti.com

NSTRUMENTS

**EXAS**

# CML Retimed Loop Through Output Electrical Specifications, DS32ELX0124 Only

Over recommended operating supply and temperature ranges unless otherwise specified. <sup>(1) (2)</sup>

| Symbol            | Parameter                                | Conditions                          | Min  | Тур | Max  | Units |

|-------------------|------------------------------------------|-------------------------------------|------|-----|------|-------|

| V <sub>LTOD</sub> | Output differential voltage              | VOD_CTRL resistor = 9.09 k $\Omega$ | 1.15 |     | 1.45 | V     |

| R <sub>LTOT</sub> | Output termination                       | 50Ω                                 | 40   | 50  | 60   | Ω     |

|                   |                                          | 75Ω                                 | 60   | 75  | 90   | 12    |

| $\Delta R_{LTOT}$ | Mismatch in output termination resistors |                                     |      | 5   |      | %     |

(1) The Electrical and Timing Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

(2) Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

(3) Parameter is guaranteed by characterization and is not tested at production.

# CML Retimed Loop Through Output Timing Specifications, DS32ELX0124 Only

Over recommended operating supply and temperature ranges unless otherwise specified. <sup>(1) (2)</sup>

| Symbol              | Parameter                                                      | Conditions | Min | Тур | Max | Units |

|---------------------|----------------------------------------------------------------|------------|-----|-----|-----|-------|

| t <sub>JIT</sub>    | Additive Output Jitter                                         | (3)        |     | 24  | 35  | ps    |

| t <sub>OS</sub>     | Output Overshoot                                               | (3)        |     | 1.5 | 8   | %     |

| t <sub>LTR</sub>    | Retimed output driver differential low to high transition time | (3)        |     | 74  | 105 | ps    |

| t <sub>LTF</sub>    | Retimed output driver differential high to low transition time | (3)        |     | 74  | 105 | ps    |

| t <sub>LTRFMM</sub> | Mismatch in Rise/Fall Time                                     | (3)        |     | 5   | 15  | %     |

| t <sub>LTDE</sub>   | Retimed driver de-emphasis width                               |            |     | 1   |     | UI    |

(1) The Electrical and Timing Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

(2) Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

(3) Parameter is guaranteed by characterization and is not tested at production.

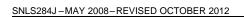

# **Timing Diagrams**

Figure 3. SMBus Timing Parameters

## Figure 4. LVDS Output Transition Time

# DS32EL0124, DS32ELX0124

SNLS284J-MAY 2008-REVISED OCTOBER 2012

Figure 5. Deserializer (LVDS Interface) Setup/Hold and High/Low Times

www.ti.com

Figure 8. CML to LVDS Bit Map

SNLS284J-MAY 2008-REVISED OCTOBER 2012

# FUNCTIONAL DESCRIPTION

### **POWER SUPPLIES**

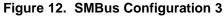

The DS32EL0124 and DS32ELX0124 have several power supply pins, at 2.5V as well as 3.3V. It is important that these pins all be connected and properly bypassed. Bypassing should consist of parallel 4.7 $\mu$ F and 0.1 $\mu$ F capacitors as a minimum, with a 0.1 $\mu$ F capacitor on each power pin. A 22  $\mu$ F capacitor is required on the VDDPLL pin which is connected to the 3.3V rail.

These devices have a large contact in the center on the bottom of the package. This contact must be connected to the system GND as it is the major ground connection for the device.

### **POWER UP**

It is recommended, although not necessary, to bring up the 3.3V power supply before the 2.5V supply. If the 2.5V supply is powered up first, an initial current draw of approximately 600mA from the 2.5V rail may occur before settling to its final value. Regardless of the sequence, both power rails should monotonically ramp up to their final values.

### POWER MANAGEMENT

These devices have two methods to reduce power consumption. To enter the first power save mode, the on board host FPGA or controlling device can cease to output the DDR transmit clock. To further reduce power, a write to the power down register will put the device in its lowest power mode.

### RESET

There are three ways to reset these devices. A reset occurs automatically during power-up. The device can also be reset by pulling the RESET pin low, with normal operation resuming when the pin is driven high again. The device can also be reset by writing to the reset register. This reset will put all of the register values back to their default values, except it will not affect the address register value if the SMBus default address has been changed.

# LVDS OUTPUTS

The DS32EL0124 and DS32ELX0124 has standard LVDS outputs, compatible with ANSI/TIA/EIA-644. It is recommended that the PCB trace between the FPGA and the deserializer output be no more than 40-inches. Longer PCB traces may introduce signal degradation as well as channel skew which could cause serialization errors. The connection between the host and the DS32EL0124 or DS32ELX0124 should be over a controlled impedance transmission line with impedance that matches the termination resistor – usually 100 $\Omega$ . Setup and hold times are specified in the LVDS Switching Characteristics table, however the clock delay can be adjusted by writing to register 30'h.

# LOOP FILTER

F

The DS32EL0124 and DSELX0124 have an internal clock data recovery module (CDR), which is used to recover the input serial data. The loop filter for this CDR is external, and for optimum results, a 30nF capacitor should be connected between pins 26 and 27. See the Typical Interface Circuit (Figure 14).

## LOOP THROUGH DRIVER LAUNCH AMPLITUDE

The launch amplitude of the retimed CML loop through driver is controlled by placing a single resistor from the VOD\_CTRL pin to ground. Use the following equation to obtain the desired  $V_{LTOD}$  by selecting the corresponding resistor value.

$$R = (1400 \text{ mV} / \text{V}_{\text{LTOD}}) \times 9.1 \text{ k}\Omega$$

(1)

The retimed CML loop through driver launch amplitude can also be adjusted by writing to SMBus register 49'h, bits 3:1. This register is meant to assist system designers during the initial prototype design phase. For final production, it is recommended that the appropriate resistor value be selected for the desired  $V_{LTOD}$  and that register 49'h be left to its default value.

Copyright © 2008–2012, Texas Instruments Incorporated

www.ti.com

# **REMOTE SENSE**

The remote sense feature can be used when a DS32EL0421 or DS32ELX0421 serializer is directly connected to a DS32EL0124 or DS32ELX0124 deserializer. Active components in the signal path between the serializer and the deserializer may interfere with the back channel signaling of the devices.

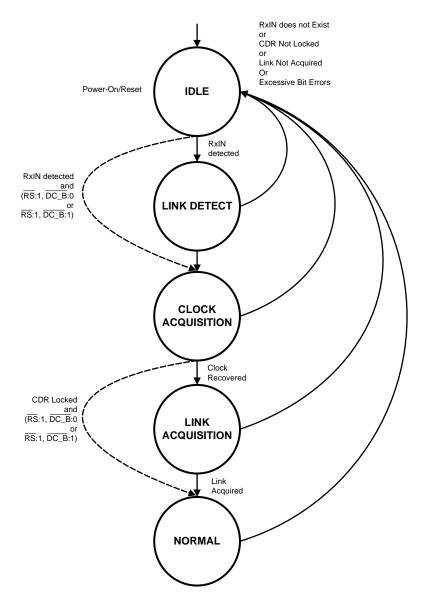

When remote sense is enabled, the deserializer will cycle through five states to successfully establish a link and align the data. The state diagram for the deserializer is shown in Figure 9. The deserializer will remain in the low power IDLE state until it receives an input signal. Once the CDR of the deserializer has locked to the input clock, the device will enter the LINK DETECT state. While in this state, the deserializer will monitor the line to see if the serializer is sending the training pattern. While in this state, the deserializer will periodically send a link detect signal upstream to notify the serializer that it can now send the training pattern. When the deserializer detects that data coming in on the serial line, it will proceed to the CLOCK ACQUISITION state. While in this state the deserializer will monitor the incoming data for set periods of time in an attempt to extract the clock from the data. Once, the deserializer has successfully extracted the clock the device will proceed to the LINK ACQUISITION STATE. In this state the deserializer will perform lane alignment based on the expected training pattern and then enter the NORMAL state. If the deserializer is unable to successfully lock or maintain lock, it will break the link sending the serializer back to the IDLE or LINK DETECT states.

# **DC-BALANCE DECODER**

The DS32EL0124 and DS32ELX0124 have a built-in DC-balance decoder to support AC-coupled applications. When enabled, the output signal RxOUT4+/-, is treated as a data valid bit. If RxOUT4+/- is low, then the data output from RxOUT0 - RxOUT3 has been successfully decoded using the 8b/10b coding scheme. If RxOUT4+/- is high and the outputs RxOUT0 - RxOUT3 are high then an invalid 8b/10b code was received, signifying a bit error. If RxOUT4+/- is high and the outputs RxOUT0 - RxOUT0 - RxOUT3 are low then an idle character has been received. The default idle character is a K28.5 code. In order to properly receive other K codes, they must first be programmed into the deserializer via the SMBus. The SMBus registers allow for only a single programmable character.

SNLS284J-MAY 2008-REVISED OCTOBER 2012

Figure 9. Deserializer State Diagram

# DESCRAMBLER AND NRZI DECODER

The CDR of the deserializer expects a transition density of 20% for a period of 200 µs. To improve the transition density of the data, the scrambler and NRZI encoder, which are integrated features in the DS32EL0421 and DS32ELX0421, serializers can be enabled. If the descrambler is enabled, the serialized data is descrambled after being recovered by the CDR to according to the polynomial specified in the DS32EL0421 datasheet. Using the scrambler/descrambler helps to lower EMI emissions by spreading the spectrum of the data. Scrambling also creates transitions for a deserializer's CDR to properly lock onto.

The scrambler is enabled or disabled by default depending on how the DC\_B and RS pins are configured. To override the default scrambler setting two register writes must be performed. First, write to register 22'h and set bit 5 to unlock the descrambler register. Next write to register 21'h and change bit 5 to the desired value. Please note that NRZI decoder has its own control bits in registers 22'h and 21'h.

Copyright © 2008–2012, Texas Instruments Incorporated

Submit Documentation Feedback 15

www.ti.com

### CML INPUT INTERFACING

The DS32ELX0124 has two inputs to support redundancy and failover applications. Either input can be selected by using the RX\_MUX\_SEL pin or internal control registers. Whichever input is selected will be routed to the CDR of the deserializer. Only one input may be selected at a time. Within the CDR, the data is strobed at the center of the eye diagram(i.e. 0.5UI).

The input stage is self-biased and does not need any external bias circuitry. The DS32EL0124 and DS32ELX0124 include integrated input termination resistors. These deserializers also support a wide common mode input from 50mV to Vcc - 50mV and can be DC-coupled where there is no significant Ground potential difference between the interfacing systems. The serial inputs also provides input equalization control in order to compensate for loss from the media. The level of equalization is controlled by the SMBus interface. For the DS32ELX0124, each input can have its own independent equalizer settings.

It is recommended to use RxIN0+/- as the primary input. Due to its close proximity to the loop through driver, RxIN1 has a typical performance less than RxIN0, with regards to cable length performance. When interfacing to RxIN1+/- and transmitting with the loop through driver on TxOUT+/-, it is important to follow good layout practices as described in the LAYOUT GUIDELINES section and in the LVDS Owner's Manual. Poor layout techniques can result in excessive cross talk coupled into RxIN1.

## CML OUTPUT INTERFACING (DS32ELX0124 ONLY)

The retimed loop through serial outputs of the DS32ELX0124 provide low-skew differential signals. Internal resistors connected from TxOUT+ and TxOUT- to VDD25 terminate the outputs. The output level can be set by adjusting the pull-down resistor to the VOD\_CTRL pin. The output terminations can also be programmed to be either 50 or 75 ohms.

The output buffer consists of a current mode logic(CML) driver with user configurable de-emphasis control, which can be used to optimize performance over a wide range of transmission line lengths and attenuation distortions resulting from low cost CAT(-5, -6, -7) cable or FR4 backplane. Output de-emphasis is user programmable through SMBus interface. Users can control the strength of the de-emphasis to optimize for a specific system environment. Please see the Register Map, register 67'h bits 6:5, for details.

## **DEVICE CONFIGURATION**

There are four ways to configure the DS32EL0124 and DS32ELX01<u>24</u> devices, these combinations are shown in Table 3. Refer to Figure 9 to see how the combinations of the RS and DC\_B pins change the link startup behavior of the deserializers. When connecting to a serializer other than the DS32EL0421 or DS32ELX0421, Remote Sense should be disabled. The descrambler and NRZI decoder shown in Table 3 can be enabled or disabled through register programming.

When Remote Sense is enabled, with  $\overline{\text{RS}}$  pin tied low, the deserializer must be connected directly to a DS32EL0421/DS32ELX0421 serializer without any active components between them. The Remote Sense module features both an upstream and downstream communication method for the serializer to detect a deserializer and vice versa. This feature is used to pass link status information between the 2 devices.

If DC-Balance is enabled, the maximum number of parallel LVDS lanes is four. The fifth lane becomes a Data Valid signal (TXIN4±). If the Data Valid input to the serializer is logic high, then SYNC characters are transmitted. If the deserializer receives a SYNC character, then the LVDS data outputs will all be logic low and the Data Valid outputs will be logic high. If the deserializer detects a DC-Balance code error, the output data pins will be set to logic high with the Data Valid output also set to logic high.

In the case where DC-Balance is enabled and Remote Sense is disabled, with RS set to high and DC\_B set to low, an external device should toggle the Data Valid input to the serializer periodically to ensure constant lock. With these pin settings the devices can interface with other active component in the high speed signal path, such as fiber modules. Every time a DS32EL0421/DS32ELX0421 serializer establishes a link to a DS32EL0124/DS32ELX0124 deserializer with DC-Balance enabled and Remote Sense disabled, the Data Valid input to the serializer must be held high for 110 LVDS clock periods. This allows the deserializer to extract the clock and perform lane alignment while skipping the LINK ACQUISITION state.

When both Remote Sense and DC-Balance are disabled,  $\overline{RS}$  and  $\overline{DC_B}$  pins set to high, the LVDS lane alignment is not maintained. In this configuration, data formatting is handled by an FPGA or external source. In this mode the deserializer locks to incoming random data. To achieve lock during the clock acquisition phase, the incoming data should have a transition density of approximately 20% for a period of 200 µs. Scrambling and NRZI encoding can be implemented to help improve the transition density of the data. This pin setting also allows for the devices to interface with other active components in the high speed signal path.

| Remote Sense Pin (RS) | DC-Balance Pin(DC_B) | Configuration                                                                                                             |

|-----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| 0                     | 0                    | Remote Sense enabled<br>DC-Balance enabled<br>Data Alignment<br>De-Scrambler and NRZI decoder disabled by<br>default      |

| 0                     | 1                    | Remote Sense enabled<br>DC-Balance disabled<br>Data Alignment<br>De-Scrambler and NRZI decoder enabled by<br>default      |

| 1                     | 0                    | Remote Sense disabled<br>DC-Balance enabled<br>Data Alignment<br>De-Scrambler and NRZI decoder enabled by<br>default      |

| 1                     | 1                    | Remote Sense disabled<br>DC-Balance disabled<br>No Data Alignment<br>De-Scrambler and NRZI decoder disabled by<br>default |

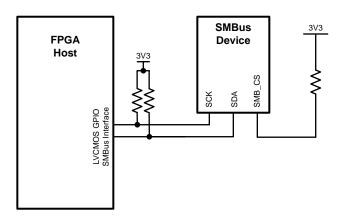

#### SMBus INTERFACE

The System Management Bus interface is compatible to SMBus 2.0 physical layer specification. The use of the Chip Select signal is **required**. Holding the SMB\_CS pin HIGH enables the SMBus port, allowing access to the configuration registers. Holding the SMB\_CS pin LOW disables the device's SMBus, allowing communication from the host to other slave devices on the bus. In the STANDBY state, the System Management Bus remains active. When communication to other devices on the SMBus is active, the SMB\_CS signal for the deserializer must be driven LOW.

The address byte for all DS32EL0124 and DS32ELX0124 devices is B0'h. Based on the SMBus 2.0 specification, these devices have a 7-bit slave address of 1011000'b. The LSB is set to 0'b (for a WRITE), thus the 8-bit value is 1011 0000'b or B0'h.

The SCK and SDA pins are 3.3V LVCMOS signaling and include high-Z internal pull up resistors. External low impedance pull up resistors maybe required depending upon SMBus loading and speed. Note, these pins are not 5V tolerant.

#### Transfer of Data via the SMBus

During normal operation the data on SDA must be stable during the time when SCK is HIGH.

There are three unique states for the SMBus:

| START | A HIGH to LOW transition on SDA while SCK is HIGH indicates a message START condition.                                                                                                                                             |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STOP  | A LOW to HIGH transition on SDA while SCK is HIGH indicates a message STOP condition.                                                                                                                                              |

| IDLE  | If SCK and SDA are both HIGH for a time exceeding $t_{BUF}$ from the last detected STOP condition or if they are HIGH for a total exceeding the maximum specification for $t_{HIGH}$ then the bus will transfer to the IDLE state. |

# **SMBus Transactions**

The devices support WRITE and READ transactions. See Register Map for register address, type (Read/ Write, Read Only), default value and function information.

## Writing to a Register

The devices support WRITE and READ transactions. See Register Map for register address, type (Read/ Write, Read Only), default value and function information.

- 1. The Host (Master) selects the device by driving its SMBus Chip Select (SMB\_CS) signal HIGH.

- 2. The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 3. The Device (Slave) drives the ACK bit ("0").

- 4. The Host drives the 8-bit Register Address.

- 5. The Device drives an ACK bit ("0").

- 6. The Host drive the 8-bit data byte.

- 7. The Device drives an ACK bit ("0").

- 8. The Host drives a STOP condition.

- 9. The Host de-selects the device by driving its SMBus CS signal Low.

The WRITE transaction is completed, the bus goes IDLE and communication with other SMBus devices may now occur.

### **Reading a Register**

To read a register, the following protocol is used (see SMBus 2.0 specification).

- 1. The Host (Master) selects the device by driving its SMBus Chip Select (SMB\_CS) signal HIGH.

- 2. The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 3. The Device (Slave) drives the ACK bit ("0").

- 4. The Host drives the 8-bit Register Address.

- 5. The Device drives an ACK bit ("0").

- 6. The Host drives a START condition.

- 7. The Host drives the 7-bit SMBus Address, and a "1" indicating a READ.

- 8. The Device drives an ACK bit "0".

- 9. The Device drives the 8-bit data value (register contents).

- 10. The Host drives a NACK bit "1" indicating end of the READ transfer.

- 11. The Host drives a STOP condition.

- 12. The Host de-selects the device by driving its SMBus CS signal Low.

The READ transaction is completed, the bus goes IDLE and communication with other SMBus devices may now occur.

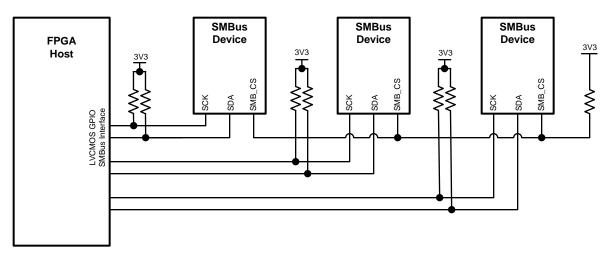

#### **SMBus Configurations**

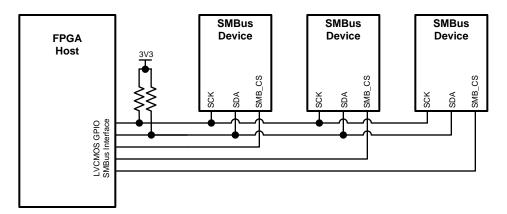

Many different configurations of the SMBus are possible and depend upon the specific requirements of the applications. Several possible applications are described.

#### **Configuration 1**

The deserializer SMB\_CS may be tied High (always enabled) since it is the only device on the SMBus. See Figure 10.

## Configuration2

Since the multiple SER devices have the same address, the use of the individual SMB\_CS signals is required. To communicate with a specific device, its SMB\_CS is driven High to select the device. After the transaction is complete, its SMB\_CS is driven Low to disable its SMB interface. Other devices on the bus may now be selected with their respective chip select signals and communicated with. See Figure 11.

#### **Configuration 3**

www.ti.com

The addressing field is limited to 7-bits by the SMBus protocol. Thus it is possible that multiple devices may share the same 7-bit address. An optional feature in the SMBus 2.0 specification supports an Address Resolution Protocol (ARP). This optional feature is not supported by the DS32EL0124/DS32ELX0124 devices. Solutions for this include: the use of the independent SMB\_CS signals, independent SMBus segments, or other means.

Figure 10. SMBus Configuration 1

# PROPAGATION DELAY

Once the deserializer is locked, the amount of time it takes for a signal to travel from the high speed CML serial input through the device and out via the DDR LVDS interface is defined to be the propagation delay. The propagation delay through the DS32EL0124/DS32ELX0124 due to the analog circuitry is considered negligible compared to the time delay caused by the digital components. The information presented in this section allows system designers to predict the propagation delay through the device in terms of clock cycles which are proportional to the high speed serial line rate.

Each clock cycle shown inFigure 13 is defined to be 1/20<sup>th</sup> of the high speed serial bit rate. For example, at a serial line rate of 3.125 Gbps the clock frequency of each delay cycle would be 156.25 MHz. Note, this is not the same frequency as the LVDS outputs, which would be 312.5 MHz for a serial line rate of 3.125 Gbps. Dashed lines in Figure 13 indicate that the feature is disabled by default in that mode and therefore add no more time to the total propagation delay. In the last row, bypassed indicates that the data is sampled even though the feature is disabled by default. The sampling of the data results in an added amount of propagation delay as specified in the box.

| Config Pins<br>(RS, DC_B) | CML Interface | NRZ Decoder           | Descrambler           | Lane<br>Alignment<br>Logic | DC Balance<br>Decoder | LVDS<br>Interface | Total<br>Propagation<br>Delay |  |  |

|---------------------------|---------------|-----------------------|-----------------------|----------------------------|-----------------------|-------------------|-------------------------------|--|--|

| Data Flow                 |               |                       |                       |                            |                       |                   |                               |  |  |

| 0, 0                      | 2 clocks      |                       |                       | 3 clocks                   | 1 clock               | 3-4 clocks        | 9-10 clocks                   |  |  |

| 0, 1                      | 2 clocks      | 1 clock               | 1 clock               | 3 clocks                   | 1 clock               | 3-4 clocks        | 11-12 clocks                  |  |  |

| 1, 0                      | 2 clocks      | 1 clock               | 1 clock               | 3 clocks                   |                       | 3-4 clocks        | 10-11 clocks                  |  |  |

| 1, 1                      | 2 clocks      | 1 clock<br>(bypassed) | 1 clock<br>(bypassed) | 3 clocks                   |                       | 3-4 clocks        | 10-11 clocks                  |  |  |

Figure 13. Deserializer Propagation Delay

# PROPAGATION DELAY FOR RETIMED LOOP THROUGH DRIVER — DS32ELX0124 ONLY

If the loop through driver is enabled in the DS32ELX0124, the propagation delay can also be defined as the amount of time it takes a signal to pass from the high speed CML serial input to the retimed loop through driver output. This time delay is measured in CDR clock cycles. The CDR clock frequency is equal to high speed serial line rate or one high speed serial bit width. For example, if the high speed serial line rate is 3.125 Gbps, then the CDR clock frequency is 3.125 GHz. The propagation delay from the high speed input to the loop through driver output is 1 CDR clock.

## **Applications Information**

#### **GPIO PINS**

The GPIO pins can be useful tools when debugging or evaluating the system. For specific GPIO configurations and functions refer to registers 2, 3, 4, 5 and 6 in the device register map.

GPIO pins are commonly used when there are multiple deserializers on the same SMBus. In order to program individual settings into each serializer, they will each need to have a unique SMBus address. To reprogram multiple deserializers on a single SMBus, configure the first deserializer such that the SMBus lines are connected to the FPGA or host controller. The CS pin of the second serializer should be tied to GPIO0 of the first deserializer, with the CS pin of the next deserializer tied to GPIO0 of its preceding deserializer. By holding all of the GPIO0 pins low, the first deserializer's address may now be reprogrammed by writing to register 0. The first deserializer's GPIO pin can now be asserted and the second deserializer's address may now be reprogrammed.

www.ti.com

#### HIGH SPEED COMMUNICATION MEDIA

Using the deserializer's integrated equalizer blocks in combination with the DS32EL0421 or DS32ELX0421's integrated de-emphasis block allows data to be transmitted across a variety of media at high speeds. Factors that can limit device performance include excessive input clock jitter, noisy power rails, EMI from nearby noisy components and poor layout techniques. Although many cables contain wires of similar gauge and shielding, performance can vary greatly depending on the quality of the connector.

The DS32ELX0124 also has a programmable de-emphasis block on its retimed loop through output TxOUT+/-. The de-emphasis setting for the loop through driver is programmed through the SMBus.

#### **REDUNDANCY APPLICATIONS**

The DS32ELX0124 has two high speed CML serial inputs. SMBus register control allows the host device to monitor for errors or link loss on the active input channel. This enables the host device, usually an FPGA, to switch to the secondary input if problems occur with the primary input.

#### LINK AGGREGATION

Multiple DS32EL0421/DS32ELX0421 serializers and D32EL0124/DS32ELX0124 deserializers can be aggregated together if an application requires a data throughput of more than 3.125 Gbps. By utilizing the data valid signal of each device, the system can be properly deskewed to allow for a single cable, such as CAT-6, DVI-D, or HDMI, to carry data payloads beyond 3.125 Gbps.

Link aggregation configurations can also be implemented in applications which require longer cable lengths. In these type of applications the data rate of each serializer and deserializer chipset can be reduced, such that the applications' net data throughput is still the same. Since each high speed channel is now operating at a fraction of the original data rate, the loss over the cable is reduced, allowing for greater lengths of cable to be used in the system.

For more information regarding link aggregation please see Application Note 1887, Expanding the Payload with National's FPGA-Link DS32ELX0421 and DS32ELX0124 Serializer and Deserializer.

#### **REACH EXTENSION**

The DS32ELX0124 deserializer contains a retimed loop through CML serial output. The loop through driver also has programmable de-emphasis making this device capable of reach extension applications.

#### DAISY CHAINING

The loop through driver of the DS32ELX0124 deserializer can be used to string together deserializers in a daisy chain configuration. This allows a single data source such as a DS32EL0421 serializer to communicate to multiple receiving systems.

#### LAYOUT GUIDELINES

It is important to follow good layout practices for high speed devices. The length of LVDS input traces should not exceed 40 inches. In noisy environments the LVDS traces may need to be shorter to prevent data corruption due to EMI. Noisy components should not be placed next to the LVDS or CML traces. The LVDS and CML traces must have a controlled differential impedance of  $100\Omega$ . Do not place termination resistors at the CML inputs or output, the DS32EL0124 and DS32ELX0124 have internal termination resistors. It is recommended to avoid using vias. Each pair of vias creates an impedance mismatch in the transmission line and result in reflections, which can greatly lower the maximum distance of the high speed data link. If vias are required, they should be placed symmetrically on each side of the differential pair. For more tips and detailed suggestions regarding high speed board layout principles, please consult the LVDS Owner's Manual.

SNLS284J-MAY 2008-REVISED OCTOBER 2012

www.ti.com

Figure 14. Typical Interface Circuit

Copyright © 2008–2012, Texas Instruments Incorporated

#### SNLS284J-MAY 2008-REVISED OCTOBER 2012

## **Typical Performance Characteristics**

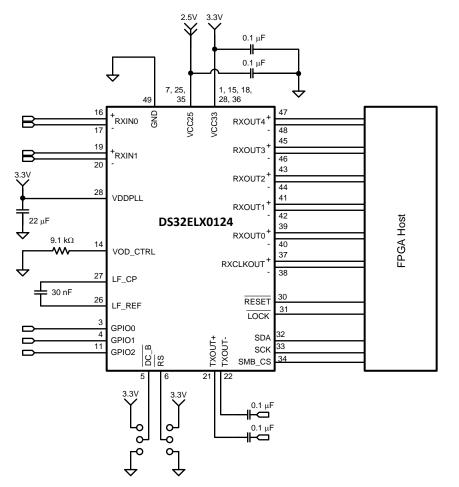

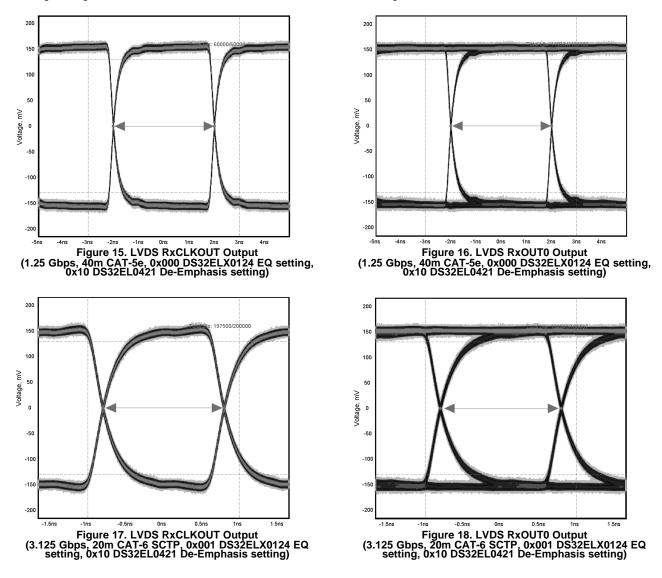

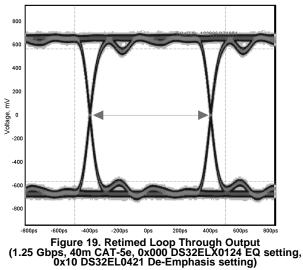

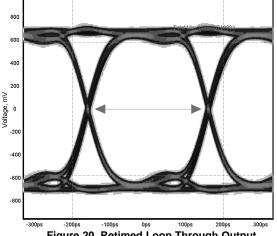

The eye diagrams shown below illustrate the typical performance of the DS32ELX0124/DS32EL0124 configured with  $\overline{RS} = 0$ ,  $\overline{DC}_B = 0$ , for the conditions listed below each figure. The PRBS-15 data was generated by a low cost FPGA, which used an LMK03000C to generate the various clock frequencies. The data was then sent to a DS32ELX0421 configured with  $\overline{RS} = 0$ ,  $\overline{DC}_B = 0$ , which transmitted the data across the specified cable type and length at the specified data rate. The signal conditioning settings used for each measurement are also listed below the figures.

#### SNLS284J-MAY 2008-REVISED OCTOBER 2012

### **Typical Performance Characteristics (continued)**

The eye diagrams shown below illustrate the typical performance of the DS32ELX0124/DS32EL0124 configured with  $\overline{RS} = 0$ ,  $\overline{DC}_B = 0$ , for the conditions listed below each figure. The PRBS-15 data was generated by a low cost FPGA, which used an LMK03000C to generate the various clock frequencies. The data was then sent to a DS32ELX0421 configured with  $\overline{RS} = 0$ ,  $\overline{DC}_B = 0$ , which transmitted the data across the specified cable type and length at the specified data rate. The signal conditioning settings used for each measurement are also listed below the figures.

Figure 20. Retimed Loop Through Output (3.125 Gbps, 20m CAT-6 SCTP, 0x001 DS32ELX0124 EQ setting, 0x10 DS32EL0421 De-Emphasis setting)

Copyright © 2008–2012, Texas Instruments Incorporated

#### www.ti.com

### **Register Map**

The register information for the deserializer is shown in the table below. Some registers have been omitted or marked as reserved; these are for internal testing and should not be written to. Some register bits require an override bit to be set before they can be written to.

| Addr (Hex) | Name         | Bits | Field          | R/W            | Default | Description                                                                                                         |                                                                                                        |

|------------|--------------|------|----------------|----------------|---------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 00         | Device ID    | 7:1  | SMBus Address  | R/W            | 58'h    | Some systems<br>will use all 8 bits<br>as the device ID.<br>This will shift the<br>value from 58'h to<br>B0'h       |                                                                                                        |

|            |              | 0    | Reserved       |                | 0       |                                                                                                                     |                                                                                                        |

| 01         | Reset        | 7:1  | Reserved       |                | 0       |                                                                                                                     |                                                                                                        |

|            |              | 0    | Software Reset | R/W            | 0       | Reset the device.<br>Does not affect<br>device ID.                                                                  |                                                                                                        |

| 02         | GPIO0 Config | 7:4  | GPIO0 Mode     | R/W            | 0       | 0000: GP Out<br>0001: Signal<br>Detect RxIN0<br>0010: BIST Status<br>All Others:<br>Reserved                        |                                                                                                        |

|            |              |      | 3:2            | GPIO0 R Enable | R/W     | 01'b                                                                                                                | 00:<br>Pullup/Pulldown<br>disabled<br>01: Pulldown<br>Enabled<br>10: Pullup<br>Enabled<br>11: Reserved |

|            |              | 1    | Input Enable   | R/W            | 0       | 0: Input buffer<br>disabled<br>1: Input buffer<br>enabled                                                           |                                                                                                        |

|            |              | 0    | Output Enable  | R/W            | 1'b     | 0: Output Tri-<br>State™<br>1: Output enabled                                                                       |                                                                                                        |

| 03         | GPIO1 Config | 7:4  | GPIO1 Mode     | R/W            | 0       | 0000: Power On<br>Reset<br>0001: GP Out<br>0010: Signal<br>Detect RxIN1<br>0011:CDR Lock<br>All Others:<br>Reserved |                                                                                                        |

|            |              | 3:2  | GPIO1 R Enable | R/W            | 01'b    | 00:<br>Pullup/Pulldown<br>disabled<br>01: Pulldown<br>Enabled<br>10: Pullup<br>Enabled<br>11: Reserved              |                                                                                                        |

|            |              | 1    | Input Enable   | R/W            | 0       | 0: Input buffer<br>disabled<br>1: Input buffer<br>enabled                                                           |                                                                                                        |

|            |              | 0    | Output Enable  | R/W            | 1       | 0: Output Tri-<br>State™<br>1: Output enabled                                                                       |                                                                                                        |

| Addr (Hex)      | Name            | Bits | Field                   | R/W | Default | Description                                                                                                      |

|-----------------|-----------------|------|-------------------------|-----|---------|------------------------------------------------------------------------------------------------------------------|

| 04              | GPIO2 Config    | 7:4  | GPIO2 Mode              | R/W | 0       | 0000: GP Out<br>0001: Always on<br>Clock Out<br>0010: LVDS Tx<br>CLK<br>0011: CDR CLK<br>All Others:<br>Reserved |

|                 |                 | 3:2  | GPIO2 R Enable          | R/W | 01'b    | 00:<br>Pullup/Pulldown<br>disabled<br>01: Pulldown<br>Enabled<br>10: Pullup<br>Enabled<br>11: Reserved           |

|                 |                 | 1    | Input Enable            | R/W | 0       | 0: Input buffer<br>disabled<br>1: Input buffer<br>enabled                                                        |

|                 |                 | 0    | Output Enable           | R/W | 1'b     | 0: Output Tri-<br>State™<br>1: Output enabled                                                                    |

| 05              | GP In           | 7:3  | Reserved                |     |         |                                                                                                                  |

|                 |                 | 2    | GP In 2                 | R   | 0       | Input value on GPIO2                                                                                             |

|                 |                 | 1    | GP In 1                 | R   | 0       | Input value on<br>GPIO1                                                                                          |

|                 |                 | 0    | GP In 0                 | R   | 0       | Input value on<br>GPIO0                                                                                          |

| 06              | GP Out          | 7:3  | Reserved                |     | 0       |                                                                                                                  |

|                 |                 | 2    | GP Out 2                | R/W | 0       | Output value on<br>GPIO2                                                                                         |

|                 |                 | 1    | GP Out 1                | R/W | 0       | Output value on<br>GPIO1                                                                                         |

|                 |                 | 0    | GP Out 0                | R/W | 0       | Output value on GPIO0                                                                                            |

| 07 — 1F Reserve | ed              |      |                         |     |         |                                                                                                                  |

| 20              | Device Config 0 | 7    | LVDS Always On<br>Clock | R/W | 0       | 1: Disable<br>0: When not<br>locked switch to<br>Always On Clock                                                 |

|                 |                 | 6:3  | Reserved                |     | 0       |                                                                                                                  |

|                 |                 | 2    | Reverse Data<br>Order   | R/W | 0       | 0: Normal<br>1: Reverse output<br>data order                                                                     |

|                 |                 | 1    | Reset Channel           | R/W | 0       | Reset input high speed channel                                                                                   |

|                 |                 | 0    | Digital Power<br>Down   | R/W | 0       | Power down<br>parallel, seria-to-<br>parallell, and<br>always on clock                                           |

Copyright © 2008–2012, Texas Instruments Incorporated

www.ti.com

Texas

NSTRUMENTS

#### SNLS284J-MAY 2008-REVISED OCTOBER 2012

| Addr (Hex)       | Name            | Bits | Field                       | R/W | Default | Description                                                                                                                   |