# **CAP1166**

## 6 Channel Capacitive Touch Sensor with 6 LED Drivers

#### **General Description**

The CAP1166, which incorporates RightTouch<sup>®</sup> technology, is a multiple channel Capacitive Touch sensor with multiple power LED drivers. It contains six (6) individual capacitive touch sensor inputs with programmable sensitivity for use in touch sensor applications. Each sensor input automatically recalibrates to compensate for gradual environmental changes.

The CAP1166 also contains six (6) LED drivers that offer full-on / off, variable rate blinking, dimness controls, and breathing. Each of the LED drivers may be linked to one of the sensor inputs to be actuated when a touch is detected. As well, each LED driver may be individually controlled via a host controller.

The CAP1166 includes Multiple Pattern Touch recognition that allows the user to select a specific set of buttons to be touched simultaneously. If this pattern is detected, then a status bit is set and an interrupt generated.

Additionally, the CAP1166 includes circuitry and support for enhanced sensor proximity detection.

The CAP1166 offers multiple power states operating at low quiescent currents. In the Standby state of operation, one or more capacitive touch sensor inputs are active and all LEDs may be used. If a touch is detected, it will wake the system using the WAKE/SPI\_MOSI pin.

Deep Sleep is the lowest power state available, drawing 5uA (typical) of current. In this state, no sensor inputs are active. Driving the WAKE/SPI\_MOSI pin or communications will wake the device.

#### Applications

- · Desktop and Notebook PCs

- LCD Monitors

- Consumer Electronics

- Appliances

#### Features

- Six (6) Capacitive Touch Sensor Inputs

- Programmable sensitivity

- Automatic recalibration

- Individual thresholds for each button

- Proximity Detection

- Multiple Button Pattern Detection

- Calibrates for Parasitic Capacitance

- · Analog Filtering for System Noise Sources

- Press and Hold feature for Volume-like Applications

- Multiple Communication Interfaces

- SMBus / I<sup>2</sup>C compliant interface

- SPI communications

- Pin selectable communications protocol and multiple slave addresses (SMBus / I<sup>2</sup>C only)

- Low Power Operation

- 5uA quiescent current in Deep Sleep

- 50uA quiescent current in Standby (1 sensor input monitored)

- Samples one or more channels in Standby

- Six (6) LED Driver Outputs

- Open Drain or Push-Pull

- Programmable blink, breathe, and dimness controls

- Can be linked to Capacitive Touch Sensor inputs

- Dedicated Wake output flags touches in low power state

- System RESET pin

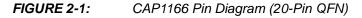

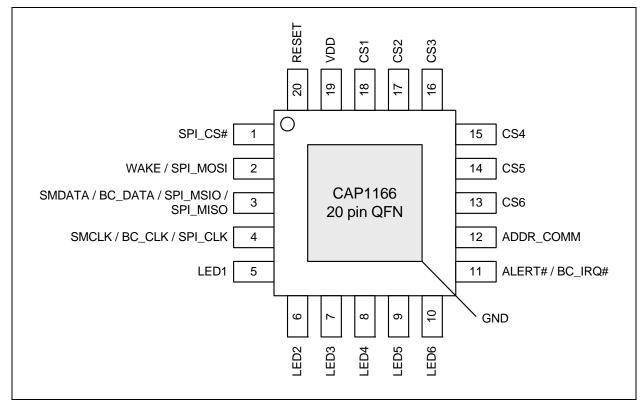

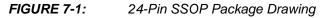

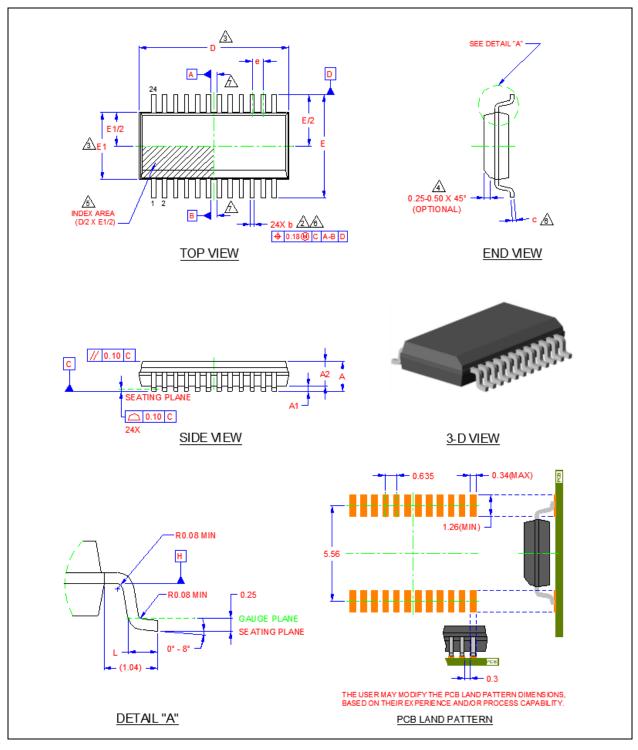

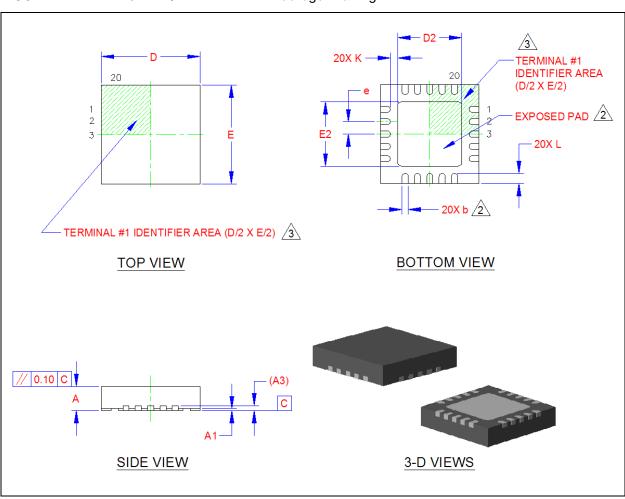

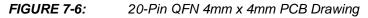

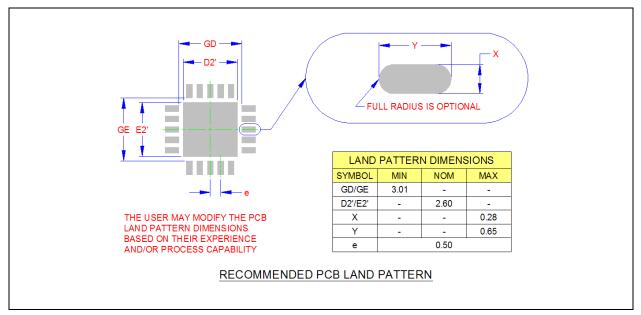

- Available in 20-pin 4mm x 4mm QFN or 24-pin SSOP RoHS compliant package

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### **Table of Contents**

| .0 Block Diagram                        | 4    |

|-----------------------------------------|------|

| .0 Pin Description                      | 5    |

| 0.0 Electrical Specifications           | 9    |

| .0 Communications                       | . 12 |

| 0.0 General Description                 | . 23 |

| 0.0 General Description                 | . 29 |

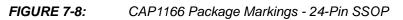

| 0 Package Information                   | . 67 |

| vppendix A: Device Delta                | . 72 |

| vppendix B: Data Sheet Revision History | . 74 |

| he Microchip Web Site                   | . 76 |

| Customer Change Notification Service    | . 76 |

| Customer Support                        | . 76 |

| Product Identification System           | . 77 |

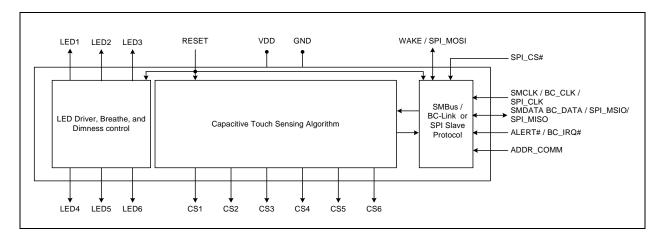

### 1.0 BLOCK DIAGRAM

## CAP1166

## 2.0 PIN DESCRIPTION

#### FIGURE 2-2: CAP1166 Pin Diagram (24-pin SSOP)

#### TABLE 2-1: PIN DESCRIPTION FOR CAP1166

| Pin<br>Number<br>(QFN 20) | Pin<br>Number<br>(SSOP 24) | Pin Name | Pin Function                                                                                                                                  | Pin Type | Unused<br>Connection  |  |

|---------------------------|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|--|

| 1                         | 4                          | SPI_CS#  | Active low chip-select for SPI bus                                                                                                            | DI (5V)  | Connect to<br>Ground  |  |

|                           |                            | 5        | WAKE - Active high wake / interrupt output                                                                                                    | DO       |                       |  |

| 2                         | 2 5 <sup>WA</sup>          |          | Standby power state - requires pull-down resistor<br>WAKE - Active high wake input - requires pull-down<br>resistor<br>Deep Sleep power state | DI       | Pull-down<br>Resistor |  |

|                           |                            |          | SPI_MOSI - SPI Master-Out-Slave-In port when used<br>in normal mode                                                                           | DI (5V)  | Connect to<br>GND     |  |

#### TABLE 2-1: PIN DESCRIPTION FOR CAP1166 (CONTINUED)

| Pin<br>Number<br>(QFN 20) | Pin<br>Number<br>(SSOP 24) | Pin Name               | Pin Function                                                                              | Pin Type  | Unused<br>Connection                  |

|---------------------------|----------------------------|------------------------|-------------------------------------------------------------------------------------------|-----------|---------------------------------------|

|                           |                            |                        | SMDATA - Bi-directional, open-drain SMBus data -<br>requires pull-up resistor             | DIOD (5V) |                                       |

|                           | <u> </u>                   | SMDATA /               | SPI_MSIO - SPI Master-Slave-In-Out bidirectional port<br>when used in bi-directional mode | DIO       | n/a                                   |

| 3                         | 6                          | SPI_MSIO /<br>SPI_MISO | SPI_MISO - SPI Master-In-Slave-Out port when used<br>in normal mode                       | DO        |                                       |

|                           |                            |                        | SMCLK - SMBus clock input - requires pull-up resistor                                     | DI (5V)   |                                       |

| 4                         | 8                          | SMCLK /<br>SPI_CLK     | SPI_CLK - SPI clock input                                                                 | DI (5V)   | n/a                                   |

|                           |                            | <u> </u>               | Open drain LED 1 driver (default)                                                         | OD (5V)   | Connect to<br>Ground                  |

| 5                         | 9                          | LED1                   | Push-pull LED 1 driver                                                                    | DO        | leave open or<br>connect to<br>Ground |

|                           |                            |                        | Open drain LED 2 driver (default)                                                         | OD (5V)   | Connect to<br>Ground                  |

| 6                         | 10                         | LED2                   | Push-pull LED 2 driver                                                                    | DO        | leave open or<br>connect to<br>Ground |

|                           |                            |                        | Open drain LED 3 driver (default)                                                         | OD (5V)   | Connect to<br>Ground                  |

| 7                         | 11                         | LED3                   | Push-pull LED 3 driver                                                                    | DO        | leave open or<br>connect to<br>Ground |

|                           |                            |                        | Open drain LED 4 driver (default)                                                         | OD (5V)   | Connect to<br>Ground                  |

| 8                         | 13                         | LED4                   | Push-pull LED 4 driver                                                                    | DO        | leave open or<br>connect to<br>Ground |

|                           |                            |                        | Open drain LED 5 driver (default)                                                         | OD (5V)   | Connect to<br>Ground                  |

| 9                         | 15                         | LED5                   | Push-pull LED 5 driver                                                                    | DO        | leave open or<br>connect to<br>Ground |

|                           |                            |                        | Open drain LED 6 driver (default)                                                         | OD (5V)   | Connect to<br>Ground                  |

| 10                        | 16                         | LED6                   | Push-pull LED 6 driver                                                                    | DO        | leave open or<br>connect to<br>Ground |

## CAP1166

#### TABLE 2-1: PIN DESCRIPTION FOR CAP1166 (CONTINUED)

| Pin<br>Number<br>(QFN 20) | Pin<br>Number<br>(SSOP 24) | Pin Name      | Pin Function                                                                                                              | Pin Type | Unused<br>Connection |

|---------------------------|----------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------|----------|----------------------|

| 11                        | 17                         | ALERT#        | ALERT# - Active low alert / interrupt output for SMBus<br>alert or SPI interrupt<br>- requires pull-up resistor (default) |          | Connect to<br>GND    |

|                           |                            |               | ALERT# - Active high push-pull alert / interrupt output<br>for SMBus alert or SPI interrupt                               | DO       | High-Z               |

| 12                        | 18                         | ADDR_<br>COMM | Address / communications select pin - pull-down resis-<br>tor determines address / communications mechanism               | AI       | n/a                  |

| 13                        | 19                         | CS6           | Capacitive Touch Sensor Input 6                                                                                           | AIO      | Connect to<br>Ground |

| 14                        | 20                         | CS5           | Capacitive Touch Sensor Input 5                                                                                           | AIO      | Connect to<br>Ground |

| 15                        | 21                         | CS4           | Capacitive Touch Sensor Input 4                                                                                           | AIO      | Connect to<br>Ground |

| 16                        | 22                         | CS3           | Capacitive Touch Sensor Input 3                                                                                           | AIO      | Connect to<br>Ground |

| 17                        | 23                         | CS2           | Capacitive Touch Sensor Input 2                                                                                           | AIO      | Connect to<br>Ground |

| 18                        | 24                         | CS1           | Capacitive Touch Sensor Input 1                                                                                           | AIO      | Connect to<br>Ground |

| 19                        | 1                          | VDD           | Positive Power supply                                                                                                     | Power    | n/a                  |

| 20                        | 1                          | RESET         | Active high soft reset for system - resets all registers to default values. If not used, connect to ground.               | DI (5V)  | Connect to<br>Ground |

| Bottom Pad                | 12                         | GND           | Ground                                                                                                                    | Power    | n/a                  |

| Dottom Pad                | 14                         | GND           | Ground                                                                                                                    | Power    | n/a                  |

**APPLICATION NOTE:** When the ALERT# pinis configured as an active low output, it will be open drain. When it is configured as an active high output, it will be push-pull.

**APPLICATION NOTE:** For the 5V tolerant pins that have a pull-up resistor, the pull-up voltage must not exceed 3.6V when the CAP1166 is unpowered.

**APPLICATION NOTE:** The SPI\_CS# pin should be grounded when SMBus, or I<sup>2</sup>C,communications are used. The pin types are described in Table 2-2. All pins labeled with (5V) are 5V tolerant.

#### TABLE 2-2: PIN TYPES

| Pin Type                                                                   | Description                                                                                                                                                                     |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Power                                                                      | This pin is used to supply power or ground to the device.                                                                                                                       |  |  |

| DI                                                                         | Digital Input - This pin is used as a digital input. This pin is 5V tolerant.                                                                                                   |  |  |

| AIO Analog Input / Output - This pin is used as an I/O for analog signals. |                                                                                                                                                                                 |  |  |

| DIOD                                                                       | Digital Input / Open Drain Output - This pin is used as a digital I/O. When it is used as an output, it is open drain and requires a pull-up resistor. This pin is 5V tolerant. |  |  |

| OD                                                                         | Open Drain Digital Output - This pin is used as a digital output. It is open drain and requires a pull-up resistor. This pin is 5V tolerant.                                    |  |  |

| DO                                                                         | Push-pull Digital Output - This pin is used as a digital output and can sink and source current.                                                                                |  |  |

| DIO                                                                        | Push-pull Digital Input / Output - This pin is used as an I/O for digital signals.                                                                                              |  |  |

## 3.0 ELECTRICAL SPECIFICATIONS

#### TABLE 3-1: ABSOLUTE MAXIMUM RATINGS

| Voltage on 5V tolerant pins (V <sub>5VT_PIN</sub> )                               | -0.3 to 5.5       | V    |

|-----------------------------------------------------------------------------------|-------------------|------|

| Voltage on 5V tolerant pins ( V <sub>5VT_PIN</sub> - V <sub>DD</sub>  ) Note 3-2  | 0 to 3.6          | V    |

| Voltage on VDD pin                                                                | -0.3 to 4         | V    |

| Voltage on any other pin to GND                                                   | -0.3 to VDD + 0.3 | V    |

| Package Power Dissipation up to $T_A = 85^{\circ}C$ for 20 pin QFN (see Note 3-3) | 0.9               | W    |

| Junction to Ambient ( $\theta_{JA}$ ) (see Note 3-4)                              | 58                | °C/W |

| Operating Ambient Temperature Range                                               | -40 to 125        | °C   |

| Storage Temperature Range                                                         | -55 to 150        | °C   |

| ESD Rating, All Pins, HBM                                                         | 8000              | V    |

**Note 3-1** Stresses above those listed could cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other condition above those indicated in the operation sections of this specification is not implied.

**Note 3-2** For the 5V tolerant pins that have a pull-up resistor, the voltage difference between  $V_{5VT_{PIN}}$  and  $V_{DD}$  must never exceed 3.6V.

**Note 3-3** The Package Power Dissipation specification assumes a recommended thermal via design consisting of a 3x3 matrix of 0.3mm (12mil) vias at 1.0mm pitch connected to the ground plane with a 2.5 x 2.5mm thermal landing.

**Note 3-4** Junction to Ambient  $(\theta_{JA})$  is dependent on the design of the thermal vias. Without thermal vias and a thermal landing, the  $\theta_{JA}$  is approximately 60°C/W including localized PCB temperature increase.

| V <sub>DD</sub> = 3V to                | 3.6V, $T_A = 0^{\circ}$ | C to 85°C, a          | II typical v | /alues at T | ี <sub>A</sub> = 27°C เ | unless otherwise noted.                                                                                                                          |

|----------------------------------------|-------------------------|-----------------------|--------------|-------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                         | Symbol                  | Min                   | Тур          | Max         | Unit                    | Conditions                                                                                                                                       |

|                                        |                         |                       | DC Po        | wer         |                         |                                                                                                                                                  |

| Supply Voltage                         | V <sub>DD</sub>         | 3.0                   | 3.3          | 3.6         | V                       |                                                                                                                                                  |

|                                        | I <sub>STBY</sub>       |                       | 120          | 170         | uA                      | Standby state active<br>1 sensor input monitored<br>No LEDs active<br>Default conditions (8 avg, 70ms<br>cycle time)                             |

| Supply Current                         | I <sub>STBY</sub>       |                       | 50           |             | uA                      | Standby state active<br>1 sensor input monitored<br>No LEDs active<br>1 avg, 140ms cycle time,                                                   |

|                                        | I <sub>DSLEEP</sub>     |                       | 5            | 15          | uA                      | Deep Sleep state active<br>LEDs at 100% or 0% Duty Cycle<br>No communications<br>$T_A < 40^{\circ}C$<br>$3.135 < V_{DD} < 3.465V$                |

|                                        | I <sub>DD</sub>         |                       | 500          | 600         | uA                      | Capacitive Sensing Active<br>No LEDs active                                                                                                      |

|                                        |                         | Capaci                | tive Touch   | Sensor In   | puts                    |                                                                                                                                                  |

| Maximum Base<br>Capacitance            | C <sub>BASE</sub>       |                       | 50           |             | pF                      | Pad untouched                                                                                                                                    |

| Minimum Detectable<br>Capacitive Shift | $\Delta c_{TOUCH}$      | 20                    |              |             | fF                      | Pad touched - default conditions (1<br>avg, 35ms cycle time, 1x sensitiv-<br>ity)                                                                |

| Recommended Cap<br>Shift               | $\Delta C_{TOUCH}$      | 0.1                   |              | 2           | pF                      | Pad touched - Not tested                                                                                                                         |

| Power Supply Rejec-<br>tion            | PSR                     |                       | ±3           | ±10         | counts /<br>V           | Untouched Current Counts<br>Base Capacitance 5pF - 50pF<br>Maximum sensitivity<br>Negative Delta Counts disabled<br>All other parameters default |

|                                        |                         |                       | Timiı        | ng          |                         |                                                                                                                                                  |

| RESET Pin Delay                        | t <sub>RST_DLY</sub>    | 10                    |              |             | ms                      |                                                                                                                                                  |

| Time to communica-<br>tions ready      | t <sub>COMM_DLY</sub>   |                       |              | 15          | ms                      |                                                                                                                                                  |

| Time to first conver-<br>sion ready    | t <sub>CONV_DLY</sub>   |                       | 170          | 200         | ms                      |                                                                                                                                                  |

|                                        |                         |                       | LED Dr       | ivers       |                         |                                                                                                                                                  |

| Duty Cycle                             | DUTY <sub>LED</sub>     | 0                     |              | 100         | %                       | Programmable                                                                                                                                     |

| Drive Frequency                        | f <sub>LED</sub>        |                       | 2            |             | kHz                     |                                                                                                                                                  |

| Sinking Current                        | I <sub>SINK</sub>       |                       |              | 24          | mA                      | V <sub>OL</sub> = 0.4                                                                                                                            |

| Sourcing Current                       | ISOURCE                 |                       |              | 24          | mA                      | V <sub>OH</sub> = V <sub>DD</sub> - 0.4                                                                                                          |

| Leakage Current                        | I <sub>LEAK</sub>       |                       |              | ±5          | uA                      | powered or unpowered<br>TA < 85°C<br>pull-up voltage <u>&lt;</u> 3.6V if unpowered                                                               |

|                                        | r                       |                       | I/O P        | ins         | 1                       |                                                                                                                                                  |

| Output Low Voltage                     | V <sub>OL</sub>         |                       |              | 0.4         | V                       | I <sub>SINK_IO</sub> = 8mA                                                                                                                       |

| Output High Voltage                    | V <sub>OH</sub>         | V <sub>DD</sub> - 0.4 |              |             | V                       | I <sub>SOURCE IO</sub> = 8mA                                                                                                                     |

### TABLE 3-2: ELECTRICAL SPECIFICATIONS

#### TABLE 3-2: ELECTRICAL SPECIFICATIONS (CONTINUED)

| V <sub>DD</sub> = 3V to               | 3.6V, $T_A = 0^{\circ}$               | C to 85°C, a         | II typical | values at T          | A = 27°C | unless otherwise noted.                                                                 |

|---------------------------------------|---------------------------------------|----------------------|------------|----------------------|----------|-----------------------------------------------------------------------------------------|

| Characteristic                        | Symbol                                | Min                  | Тур        | Max                  | Unit     | Conditions                                                                              |

| Input High Voltage                    | V <sub>IH</sub>                       | 2.0                  |            |                      | V        |                                                                                         |

| Input Low Voltage                     | V <sub>IL</sub>                       |                      |            | 0.8                  | V        |                                                                                         |

| Leakage Current                       | I <sub>LEAK</sub>                     |                      |            | ±5                   | uA       | powered or unpowered<br>$T_A < 85^{\circ}C$<br>pull-up voltage $\leq 3.6V$ if unpowered |

| RESET Pin Release to conversion ready | t <sub>RESET</sub>                    |                      | 170        | 200                  | ms       |                                                                                         |

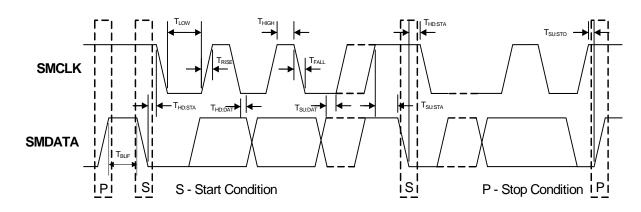

|                                       |                                       |                      | SMBus      | Timing               |          |                                                                                         |

| Input Capacitance                     | C <sub>IN</sub>                       |                      | 5          |                      | pF       |                                                                                         |

| Clock Frequency                       | f <sub>SMB</sub>                      | 10                   |            | 400                  | kHz      |                                                                                         |

| Spike Suppression                     | t <sub>SP</sub>                       |                      |            | 50                   | ns       |                                                                                         |

| Bus Free Time Stop to<br>Start        | t <sub>BUF</sub>                      | 1.3                  |            |                      | us       |                                                                                         |

| Start Setup Time                      | t <sub>SU:STA</sub>                   | 0.6                  |            |                      | us       |                                                                                         |

| Start Hold Time                       | t <sub>HD:STA</sub>                   | 0.6                  |            |                      | us       |                                                                                         |

| Stop Setup Time                       | t <sub>SU:STO</sub>                   | 0.6                  |            |                      | us       |                                                                                         |

| Data Hold Time                        | t <sub>HD:DAT</sub>                   | 0                    |            |                      | us       | When transmitting to the master                                                         |

| Data Hold Time                        | t <sub>HD:DAT</sub>                   | 0.3                  |            |                      | us       | When receiving from the master                                                          |

| Data Setup Time                       | t <sub>SU:DAT</sub>                   | 0.6                  |            |                      | us       |                                                                                         |

| Clock Low Period                      | t <sub>LOW</sub>                      | 1.3                  |            |                      | us       |                                                                                         |

| Clock High Period                     | t <sub>HIGH</sub>                     | 0.6                  |            |                      | us       |                                                                                         |

| Clock / Data Fall Time                | t <sub>FALL</sub>                     |                      |            | 300                  | ns       | $Min = 20+0.1C_{LOAD} ns$                                                               |

| Clock / Data Rise<br>Time             | t <sub>RISE</sub>                     |                      |            | 300                  | ns       | $Min = 20+0.1C_{LOAD} ns$                                                               |

| Capacitive Load                       | C <sub>LOAD</sub>                     |                      |            | 400                  | pF       | per bus line                                                                            |

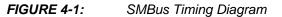

|                                       |                                       |                      | SPI Ti     | ming                 |          |                                                                                         |

| Clock Period                          | t <sub>P</sub>                        | 250                  |            |                      | ns       |                                                                                         |

| Clock Low Period                      | t <sub>LOW</sub>                      | 0.4 x t <sub>P</sub> |            | 0.6 x t <sub>P</sub> | ns       |                                                                                         |

| Clock High Period                     | t <sub>HIGH</sub>                     | 0.4 x t <sub>P</sub> |            | 0.6 x t <sub>P</sub> | ns       |                                                                                         |

| Clock Rise / Fall time                | t <sub>RISE</sub> / t <sub>FALL</sub> |                      |            | 0.1 x t <sub>P</sub> | ns       |                                                                                         |

| Data Output Delay                     | t <sub>D:CLK</sub>                    |                      |            | 10                   | ns       |                                                                                         |

| Data Setup Time                       | t <sub>SU:DAT</sub>                   | 20                   |            |                      | ns       |                                                                                         |

| Data Hold Time                        | t <sub>HD:DAT</sub>                   | 20                   |            |                      | ns       |                                                                                         |

| SPI_CS# to SPI_CLK<br>setup time      | t <sub>SU:CS</sub>                    | 0                    |            |                      | ns       |                                                                                         |

| Wake Time                             | t <sub>WAKE</sub>                     | 10                   |            | 20                   | us       | SPI_CS# asserted to CLK assert                                                          |

**Note 3-5** The ALERT pin will not glitch high or low at power up if connected to VDD or another voltage.

**Note 3-6** The SMCLK and SMDATA pins will not glitch low at power up if connected to VDD or another voltage.

### 4.0 COMMUNICATIONS

#### 4.1 Communications

The CAP1166communicates using the 2-wire SMBus or  $I^2C$  bus, the 2-wire proprietary BC-Link, or the SPI bus. If the proprietary BC-Link protocol is required for your application, please contact your Microchip representative for ordering instructions. Regardless of communication mechanism, the device functionality remains unchanged. The communications mechanism as well as the SMBus (or  $I^2C$ ) slave address is determined by the resistor connected between the ADDR\_COMM pin and ground as shown in Table 4-1.

| Pull-Down Resistor (+/- 5%) | Protocol Used                                                    | SMBus Address |

|-----------------------------|------------------------------------------------------------------|---------------|

| GND                         | SPI Communications using Normal<br>4-wire Protocol Used          | n/a           |

| 56k                         | SPI Communications using Bi-<br>Directional 3-wire Protocol Used | n/a           |

| 68k                         | Reserved                                                         | n/a           |

| 82k                         | SMBus / I <sup>2</sup> C                                         | 0101_100(r/w) |

| 100k                        | SMBus / I <sup>2</sup> C                                         | 0101_011(r/w) |

| 120k                        | SMBus / I <sup>2</sup> C                                         | 0101_010(r/w) |

| 150k                        | SMBus / I <sup>2</sup> C                                         | 0101_001(r/w) |

| VDD                         | SMBus / I <sup>2</sup> C                                         | 0101_000(r/w) |

#### 4.1.1 SMBUS (I<sup>2</sup>C) COMMUNICATIONS

When configured to communicate via the SMBus, the CAP1166 supports the following protocols: Send Byte, Receive Byte, Read Byte, Write Byte, Read Block, and Write Block. In addition, the device supports  $I^2C$  formatting for block read and block write protocols.

**APPLICATION NOTE:** For SMBus/I<sup>2</sup>C communications, the SPI\_CS# pin is not used and should be grounded; any data presented to this pin will be ignored.

See Section 4.2 and Section 4.3 for more information on the SMBus bus and protocols respectively.

#### 4.1.2 SPI COMMUNICATIONS

When configured to communicate via the SPI bus, the CAP1166supports both bi-directional 3-wire and normal 4-wire protocols and uses the SPI\_CS# pin to enable communications.

APPLICATION NOTE: See Section 4.5 and Section 4.6 for more information on the SPI bus and protocols respectively. Upon power up, the CAP1166 will not respond to any communications for up to 15ms. After this time, full functionality is available.

#### 4.2 System Management Bus

The CAP1166 communicates with a host controller, such as an SIO, through the SMBus. The SMBus is a two-wire serial communication protocol between a computer host and its peripheral devices. A detailed timing diagram is shown in Figure 4-1. Stretching of the SMCLK signal is supported; however, the CAP1166 will not stretch the clock signal.

#### 4.2.1 SMBUS START BIT

The SMBus Start bit is defined as a transition of the SMBus Data line from a logic '1' state to a logic '0' state while the SMBus Clock line is in a logic '1' state.

#### 4.2.2 SMBUS ADDRESS AND RD / WR BIT

The SMBus Address Byte consists of the 7-bit slave address followed by the RD /  $\overline{WR}$  indicator bit. If this RD /  $\overline{WR}$  bit is a logic '0', then the SMBus Host is writing data to the slave device. If this RD /  $\overline{WR}$  bit is a logic '1', then the SMBus Host is reading data from the slave device.

See Table 4-1 for available SMBus addresses.

#### 4.2.3 SMBUS DATA BYTES

All SMBus Data bytes are sent most significant bit first and composed of 8-bits of information.

#### 4.2.4 SMBUS ACK AND NACK BITS

The SMBus slave will acknowledge all data bytes that it receives. This is done by the slave device pulling the SMBus Data line low after the 8th bit of each byte that is transmitted. This applies to both the Write Byte and Block Write protocols.

The Host will NACK (not acknowledge) the last data byte to be received from the slave by holding the SMBus data line high after the 8th data bit has been sent. For the Block Read protocol, the Host will ACK each data byte that it receives except the last data byte.

#### 4.2.5 SMBUS STOP BIT

The SMBus Stop bit is defined as a transition of the SMBus Data line from a logic '0' state to a logic '1' state while the SMBus clock line is in a logic '1' state. When the CAP1166 detects an SMBus Stop bit and it has been communicating with the SMBus protocol, it will reset its slave interface and prepare to receive further communications.

#### 4.2.6 SMBUS TIMEOUT

The CAP1166 includes an SMBus timeout feature. Following a 30ms period of inactivity on the SMBus where the SMCLK pin is held low, the device will timeout and reset the SMBus interface.

The timeout function defaults to disabled. It can be enabled by setting the TIMEOUT bit in the Configuration register (see Section 6.6, "Configuration Registers").

#### 4.2.7 SMBUS AND I<sup>2</sup>C COMPATIBILITY

The major differences between SMBus and  $I^2C$  devices are highlighted here. For more information, refer to the SMBus 2.0 and  $I^2C$  specifications. For information on using the CAP1166 in an  $I^2C$  system, refer to AN 14.0 Dedicated Slave Devices in  $I^2C$  Systems.

- 1. CAP1166 supports I<sup>2</sup>C fast mode at 400kHz. This covers the SMBus max time of 100kHz.

- Minimum frequency for SMBus communications is 10kHz. 2.

- 3. The SMBus slave protocol will reset if the clock is held at a logic '0' for longer than 30ms. This timeout functionality is disabled by default in the CAP1166 and can be enabled by writing to the TIMEOUT bit. I<sup>2</sup>C does not have a timeout.

- The SMBus slave protocol will reset if both the clock and data lines are held at a logic '1' for longer than 200µs 4. (idle condition). This function is disabled by default in the CAP1166 and can be enabled by writing to the TIME-OUT bit. I<sup>2</sup>C does not have an idle condition.

- 5. I<sup>2</sup>C devices do not support the Alert Response Address functionality (which is optional for SMBus).

- I<sup>2</sup>C devices support block read and write differently. I<sup>2</sup>C protocol allows for unlimited number of bytes to be sent 6 in either direction. The SMBus protocol requires that an additional data byte indicating number of bytes to read / write is transmitted. The CAP1166 supports I<sup>2</sup>C formatting only.

#### 4.3 SMBus Protocols

The CAP1166 is SMBus 2.0 compatible and supports Write Byte, Read Byte, Send Byte, and Receive Byte as valid protocols as shown below.

All of the below protocols use the convention in Table 4-2.

| TABLE 4-2:             | PROTOCOL FORM            | ΙΑΤ |

|------------------------|--------------------------|-----|

| Data Sent to<br>Device | Data Sent to the<br>HOst |     |

Data sent

#### 4.3.1 SMBUS WRITE BYTE

The Write Byte is used to write one byte of data to a specific register as shown in Table 4-3.

Data sent

#### **TABLE 4-3**: WRITE BYTE PROTOCOL

| Start | Slave<br>Address | WR | ACK | Register<br>Address | ACK | Register Data | ACK | Stop   |

|-------|------------------|----|-----|---------------------|-----|---------------|-----|--------|

| 1 ->0 | YYYY_YYY         | 0  | 0   | XXh                 | 0   | XXh           | 0   | 0 -> 1 |

#### 4.3.2 SMBUS READ BYTE

The Read Byte protocol is used to read one byte of data from the registers as shown in Table 4-4.

#### **TABLE 4-4: READ BYTE PROTOCOL**

| Start | Slave<br>Address | WR | ACK | Register<br>Address | АСК | Start | Slave<br>Address | RD | АСК | Register<br>Data | NACK | Stop   |

|-------|------------------|----|-----|---------------------|-----|-------|------------------|----|-----|------------------|------|--------|

| 1->0  | YYYY_YYY         | 0  | 0   | XXh                 | 0   | 1 ->0 | YYYY_YYY         | 1  | 0   | XXh              | 1    | 0 -> 1 |

#### 4.3.3 SMBUS SEND BYTE

The Send Byte protocol is used to set the internal address register pointer to the correct address location. No data is transferred during the Send Byte protocol as shown in Table 4-5.

APPLICATION NOTE: The Send Byte protocol is not functional in Deep Sleep (i.e., DSLEEP bit is set).

**TABLE 4-5**: SEND BYTE PROTOCOL

| Start  | Slave Address | WR | ACK | Register Address | ACK | Stop   |

|--------|---------------|----|-----|------------------|-----|--------|

| 1 -> 0 | YYYY_YYY      | 0  | 0   | XXh              | 0   | 0 -> 1 |

#### 4.3.4 SMBUS RECEIVE BYTE

The Receive Byte protocol is used to read data from a register when the internal register address pointer is known to be at the right location (e.g., set via Send Byte). This is used for consecutive reads of the same register as shown in Table 4-6.

APPLICATION NOTE: The Receive Byte protocol is not functional in Deep Sleep (i.e., DSLEEP bit is set).

| Start  | Slave Address | RD | ACK | Register Data | NACK | Stop   |

|--------|---------------|----|-----|---------------|------|--------|

| 1 -> 0 | YYYY_YYY      | 1  | 0   | XXh           | 1    | 0 -> 1 |

#### 4.4 I<sup>2</sup>C Protocols

The CAP1166 supports I<sup>2</sup>C Block Write and Block Read.

The protocols listed below use the convention in Table 4-2.

#### 4.4.1 BLOCK WRITE

The Block Write is used to write multiple data bytes to a group of contiguous registers as shown in Table 4-7.

APPLICATION NOTE: When using the Block Write protocol, the internal address pointer will be automatically incremented after every data byte is received. It will wrap from FFh to 00h.

TABLE 4-7: BLOCK WRITE PROTOCOL

| Start         | Slave<br>Address | WR               | ACK | Register<br>Address | ACK              | Register Data | ACK    |

|---------------|------------------|------------------|-----|---------------------|------------------|---------------|--------|

| 1 ->0         | YYYY_YYY         | 0                | 0   | XXh                 | 0                | XXh           | 0      |

| Register Data | ACK              | Register<br>Data | ACK |                     | Register<br>Data | ACK           | Stop   |

| XXh           | 0                | XXh              | 0   |                     | XXh              | 0             | 0 -> 1 |

#### 4.4.2 BLOCK READ

The Block Read is used to read multiple data bytes from a group of contiguous registers as shown in Table 4-8.

APPLICATION NOTE: When using the Block Read protocol, the internal address pointer will be automatically incremented after every data byte is received. It will wrap from FFh to 00h.

TABLE 4-8:BLOCK READ PROTOCOL

| Start | Slave<br>Address | WR  | ACK              | Register<br>Address | ACK              | Start | Slave<br>Address | RD               | АСК  | Register<br>Data |

|-------|------------------|-----|------------------|---------------------|------------------|-------|------------------|------------------|------|------------------|

| 1->0  | YYYY_YYY         | 0   | 0                | XXh                 | 0                | 1 ->0 | YYYY_YYY         | 1                | 0    | XXh              |

| ACK   | Register<br>Data | ACK | Register<br>Data | ACK                 | Register<br>Data | ACK   |                  | Register<br>Data | NACK | Stop             |

| 0     | XXh              | 0   | XXh              | 0                   | XXh              | 0     |                  | XXh              | 1    | 0 -> 1           |

#### 4.5 SPI Interface

The SMBus has a predefined packet structure, the SPI does not. The SPI Bus can operate in two modes of operation, normal 4-wire mode and bi-directional 3-wire mode. All SPI commands consist of 8-bit packets sent to a specific slave device (identified by the CS pin).

The SPI bus will latch data on the rising edge of the clock and the clock and data both idle high.

All commands are supported via both operating modes. The supported commands are: Reset Serial interface, set address pointer, write command and read command. Note that all other codes received during the command phase are ignored and have no effect on the operation of the device.

#### 4.5.1 SPI NORMAL MODE

The SPI Bus can operate in two modes of operation, normal and bi-directional mode. In the normal mode of operation, there are dedicated input and output data lines. The host communicates by sending a command along the CAP1166 SPI\_MOSI data line and reading data on the SPI\_MISO data line. Both communications occur simultaneously which allows for larger throughput of data transactions.

All basic transfers consist of two 8 bit transactions from the Master device while the slave device is simultaneously sending data at the current address pointer value.

Data writes consist of two or more 8-bit transactions. The host sends a specific write command followed by the data to write the address pointer. Data reads consist of one or more 8-bit transactions. The host sends the specific read data command and continues clocking for as many data bytes as it wishes to receive.

#### 4.5.2 SPI BI-DIRECTIONAL MODE

In the bi-directional mode of operation, the SPI data signals are combined into the SPI\_MSIO line, which is shared for data received by the device and transmitted by the device. The protocol uses a simple handshake and turn around sequence for data communications based on the number of clocks transmitted during each phase.

All basic transfers consist of two 8 bit transactions. The first is an 8 bit command phase driven by the Master device. The second is by an 8 bit data phase driven by the Master for writes, and by the CAP1166 for read operations.

The auto increment feature of the address pointer allows for successive reads or writes. The address pointer will return to 00h after reaching FFh.

#### 4.5.3 SPI\_CS# PIN

The SPI Bus is a single master, multiple slave serial bus. Each slave has a dedicated CS pin (chip select) that the master asserts low to identify that the slave is being addressed. There are no formal addressing options.

#### 4.5.4 ADDRESS POINTER

All data writes and reads are accessed from the current address pointer. In both Bi-directional mode and Full Duplex mode, the Address pointer is automatically incremented following every read command or every write command.

The address pointer will return to 00h after reaching FFh.

#### 4.5.5 SPI TIMEOUT

The CAP1166 does not detect any timeout conditions on the SPI bus.

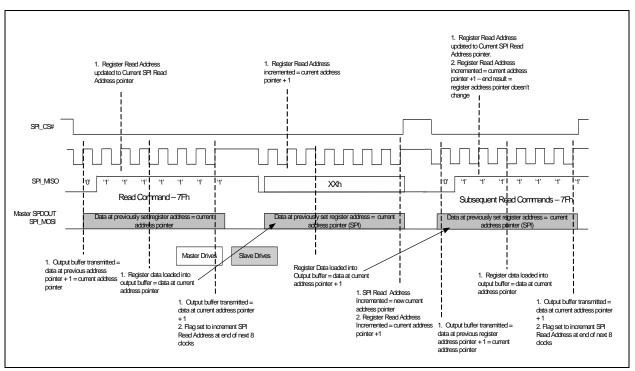

#### 4.6 Normal SPI Protocols

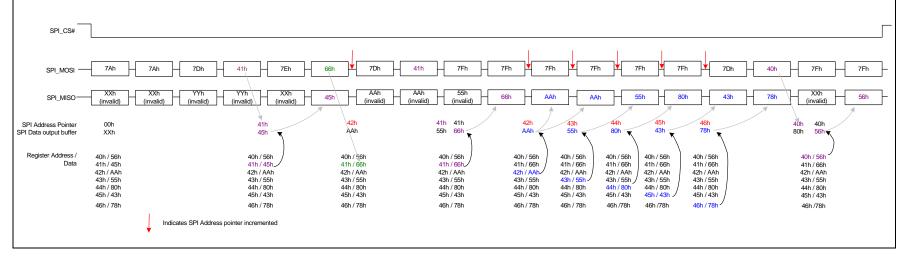

When operating in normal mode, the SPI bus internal address pointer is incremented depending upon which command has been transmitted. Multiple commands may be transmitted sequentually so long as the SPI\_CS# pin is asserted low. Figure 4-3 shows an example of this operation.

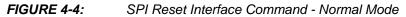

#### 4.6.1 RESET INTERFACE

Resets the Serial interface whenever two successive 7Ah codes are received. Regardless of the current phase of the transaction - command or data, the receipt of the successive reset commands resets the Serial communication interface only. All other functions are not affected by the reset operation.

| SPI_CS#                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SPI_CLK                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Master SPDOUT<br>SPI_MOSI | '0'       '1'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '0'       '1'       '1'       '0'       '1'       ' |  |

| SPI_MISO                  | Invalid register data 00h – Internal Data buffer empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                           | Master Drives Slave Drives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

#### 4.6.2 SET ADDRESS POINTER

The Set Address Pointer command sets the Address pointer for subsequent reads and writes of data. The pointer is set on the rising edge of the final data bit. At the same time, the data that is to be read is fetched and loaded into the internal output buffer but is not transmitted.

#### FIGURE 4-5: SPI Set Address Pointer Command - Normal Mode

| SPI_CS#                   |                              |                                |

|---------------------------|------------------------------|--------------------------------|

| SPI_CLK                   |                              |                                |

| Master SPDOUT<br>SPI_MOSI | 0, (1, 1, 1, 1, 1, 1, 0, (1, | Register Address               |

|                           | Set Address Pointer – 7Dh    |                                |

| SPI_MISO                  | Unknown, Invalid Data        | Unknown, Invalid Data          |

|                           | Master Drives S              | ave Drives Address pointer set |

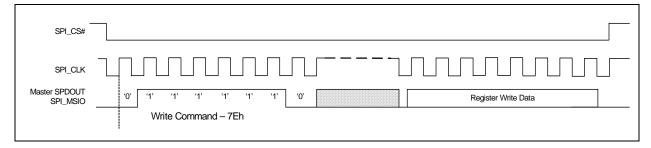

#### 4.6.3 WRITE DATA

The Write Data protocol updates the contents of the register referenced by the address pointer. As the command is processed, the data to be read is fetched and loaded into the internal output buffer but not transmitted. Then, the register is updated with the data to be written. Finally, the address pointer is incremented.

| r                         |                                                          |                                                                                 |

|---------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------|

| SPI_CS#                   |                                                          |                                                                                 |

| SPI_CLK                   |                                                          |                                                                                 |

| Master SPDOUT<br>SPI_MOSI | Write Command – 7Eh Data to Write                        |                                                                                 |

|                           |                                                          |                                                                                 |

| SPI_MISO                  | Unknown, Invalid Data Old Data at Current Address Pointe | er                                                                              |

|                           | а                                                        | I. Data written at current<br>address pointer<br>2. Address pointer incremented |

#### FIGURE 4-6: SPI Write Command - Normal Mode

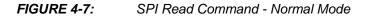

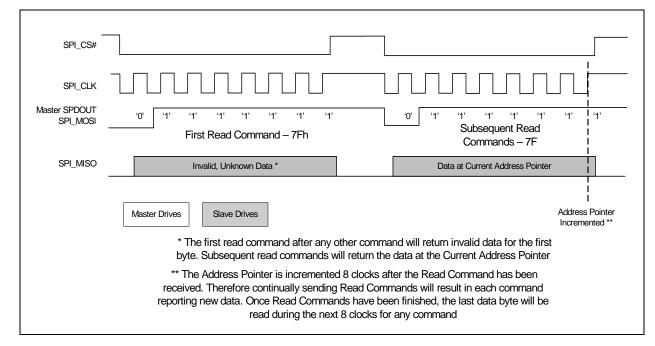

#### 4.6.4 READ DATA

The Read Data protocol is used to read data from the device. During the normal mode of operation, while the device is receiving data, the CAP1166 is simultaneously transmitting data to the host. For the Set Address commands and the Write Data commands, this data may be invalid and it is recommended that the Read Data command is used.

#### FIGURE 4-8: SPI Read Command - Normal Mode - Full

#### 4.7 Bi-Directional SPI Protocols

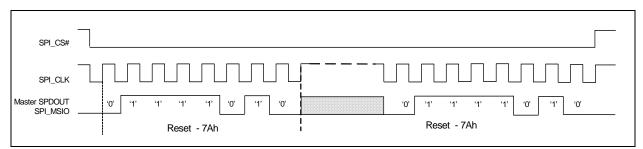

#### 4.7.1 RESET INTERFACE

Resets the Serial interface whenever two successive 7Ah codes are received. Regardless of the current phase of the transaction - command or data, the receipt of the successive reset commands resets the Serial communication interface only. All other functions are not affected by the reset operation.

#### FIGURE 4-9: SPI Reset Interface Command - Bi-directional Mode

#### 4.7.2 SET ADDRESS POINTER

Sets the address pointer to the register to be accessed by a read or write command. This command overrides the autoincrementing of the address pointer.

#### FIGURE 4-10: SPI Set Address Pointer Command - Bi-directional Mode

| SPI_CS#                   |                                                                                                                  |

|---------------------------|------------------------------------------------------------------------------------------------------------------|

| SPI_CLK                   |                                                                                                                  |

| Master SPDOUT<br>SPI_MSIO | '0'         '1'         '1'         '0'         '1'         Register Address           Set Address Pointer – 7Dh |

#### 4.7.3 WRITE DATA

Writes data value to the register address stored in the address pointer. Performs auto increment of address pointer after the data is loaded into the register.

#### FIGURE 4-11: SPI Write Data Command - Bi-directional Mode

#### 4.7.4 READ DATA

Reads data referenced by the address pointer. Performs auto increment of address pointer after the data is transferred to the Master.

#### FIGURE 4-12: SPI Read Data Command - Bi-directional Mode

| SPI_CLK                   |                                                  |  |

|---------------------------|--------------------------------------------------|--|

| Master SPDOUT<br>SPI_MSIO | 10 11 11 11 11 11 11 11 11 11 Register Read Data |  |

|                           | Read Command 7Fh                                 |  |

|                           | Master Drives Save Drives Indeterminate          |  |

|                           |                                                  |  |

#### 4.8 BC-Link Interface

The BC-Link is a proprietary bus developed to allow communication between a host controller device to a companion device. This device uses this serial bus to read and write registers and for interrupt processing. The interface uses a data port concept, where the base interface has an address register, data register and a control register, defined in the 8051's SFR space.

Refer to documentation for the BC-Link compatible host controller for details on how to access the CAP1166 via the BC-Link Interface.

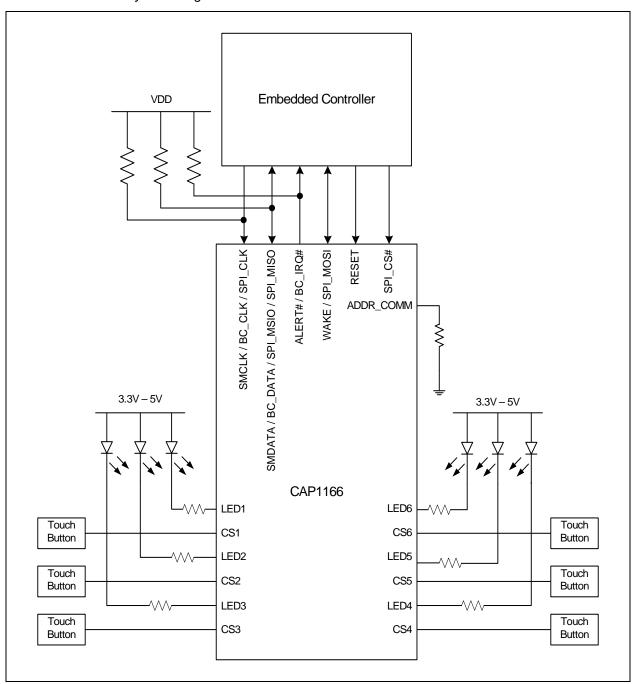

### 5.0 GENERAL DESCRIPTION

The CAP1166 is a multiple channel Capacitive Touch sensor with multiple power LED drivers. It contains six (6) individual capacitive touch sensor inputs with programmable sensitivity for use in touch sensor applications. Each sensor input automatically recalibrates to compensate for gradual environmental changes.

The CAP1166 also contains six (6) low side (or push-pull) LED drivers that offer full-on / off, variable rate blinking, dimness controls, and breathing. Each of the LED drivers may be linked to one of the sensor inputs to be actuated when a touch is detected. As well, each LED driver may be individually controlled via a host controller.

Finally, the device contains a dedicated RESET pin to act as a soft reset by the system.

The CAP1166 offers multiple power states. It operates at the lowest quiescent current during its Deep Sleep state. In the low power Standby state, it can monitor one or more channels and respond to communications normally. The device contains a wake pin (WAKE/SPI\_MOSI) output to wake the system when a touch is detected in Standby and to wake the device from Deep Sleep.

The device communicates with a host controller using the SPI bus, or via SMBus / I<sup>2</sup>C. The host controller may poll the device for updated information at any time or it may configure the device to flag an interrupt whenever a touch is detected on any sensor pad.

A typical system diagram is shown in Figure 5-1.

FIGURE 5-1: System Diagram for CAP1166

#### 5.1 Power States

The CAP1166 has three operating states depending on the status of the STBY and DSLEEP bits. When the device transitions between power states, previously detected touches (for inactive channels) are cleared and the status bits reset.

- 1. Fully Active The device is fully active. It is monitoring all active capacitive sensor inputs and driving all LED channels as defined.

- 2. Standby The device is in a lower power state. It will measure a programmable number of channels using the Standby Configuration controls (see Section 6.20 through Section 6.22). Interrupts will still be generated based on the active channels. The device will still respond to communications normally and can be returned to the Fully

Active state of operation by clearing the STBY bit.

3. Deep Sleep - The device is in its lowest power state. It is not monitoring any capacitive sensor inputs and not driving any LEDs. All LEDs will be driven to their programmed non-actuated state and no PWM operations will be done. While in Deep Sleep, the device can be awakened by SMBus or SPI communications targeting the device. This will not cause the DSLEEP to be cleared so the device will return to Deep Sleep once all communications have stopped.

If the device is not communicating via the 4-wire SPI bus, then during this state of operation, if the WAKE/SPI\_MOSI pin is driven high by an external source, the device will clear the DSLEEP bit and return to Fully Active.

**APPLICATION NOTE:** In the Deep Sleep state, the LED output will be either high or low and will not be PWM'd at the min or max duty cycle.

#### 5.2 RESET Pin

The RESET pin is an active high reset that is driven from an external source. While it is asserted high, all the internal blocks will be held in reset including the communications protocol used. No capacitive touch sensor inputs will be sampled and the LEDs will not be driven. All configuration settings will be reset to default states and all readings will be cleared.

The device will be held in Deep Sleep that can only be removed by driving the RESET pin low. This will cause the RESET status bit to be set to a logic '1' and generate an interrupt.

#### 5.3 WAKE/SPI\_MOSI Pin Operation

The WAKE / SPI\_MOSI pin is a multi-function pin depending on device operation. When the device is configured to communicate using the 4-wire SPI bus, this pin is an input.

However, when the CAP1166 is placed in Standby and is not communicating using the 4-wire SPI protocol, the WAKE pin is an active high output. In this condition, the device will assert the WAKE/SPI\_MOSI pin when a touch is detected on one of its sampled sensor inputs. The pin will remain asserted until the INT bit has been cleared and then it will be de-asserted.

When the CAP1166 is placed in Deep Sleep and it is not communicating using the 4-wire SPI protocol, the WAKE/SPI\_MOSI pin is monitored by the device as an input. If the WAKE/SPI\_MOSI pin is driven high by an external source, the CAP1166will clear the DSLEEP bit causing the device to return to Fully Active.

When the device is placed in Deep Sleep, this pin is a High-Z input and must have a pull-down resistor to GND for proper operation.

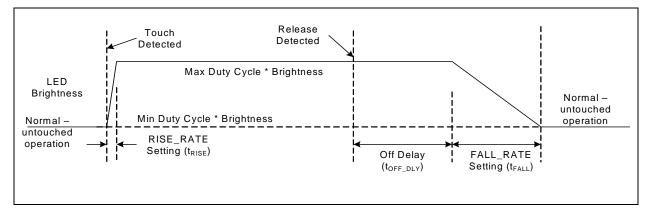

#### 5.4 LED Drivers

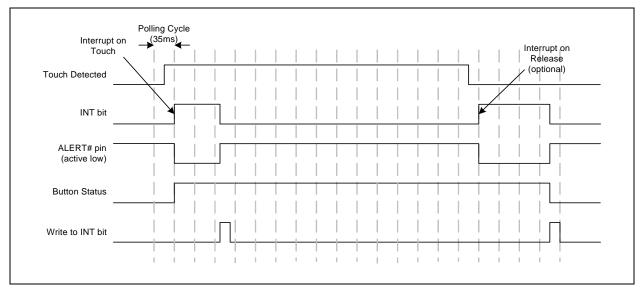

The CAP1166 contains six (6) LED drivers. Each LED driver can be linked to its respective capacitive touch sensor input or it can be controlled by the host. Each LED driver can be configured to operate in one of the following modes with either push-pull or open drain drive.

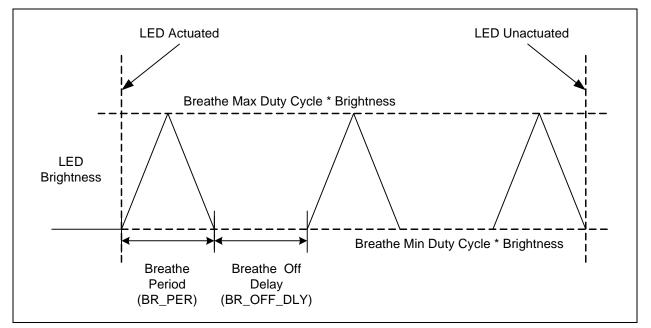

- 1. Direct The LED is configured to be on or off when the corresponding input stimulus is on or off (or inverted). The brightness of the LED can be programmed from full off to full on (default). Additionally, the LED contains controls to individually configure ramping on, off, and turn-off delay.

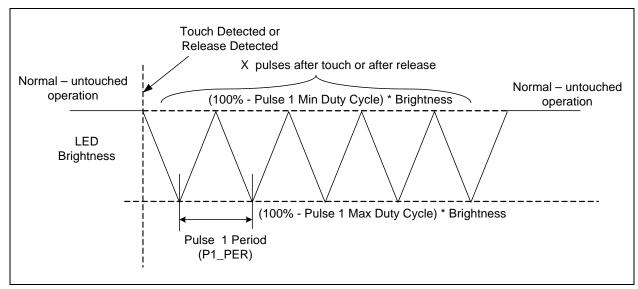

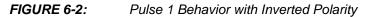

- 2. Pulse 1 The LED is configured to "Pulse" (transition ON-OFF-ON) a programmable number of times with programmable rate and min / max brightness. This behavior may be actuated when a press is detected or when a release is detected.

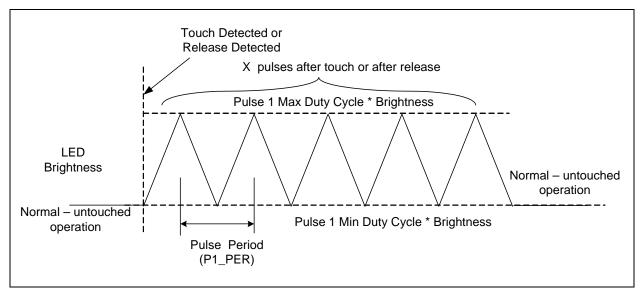

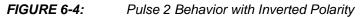

- 3. Pulse 2 The LED is configured to "Pulse" while actuated and then "Pulse" a programmable number of times with programmable rate and min / max brightness when the sensor pad is released.

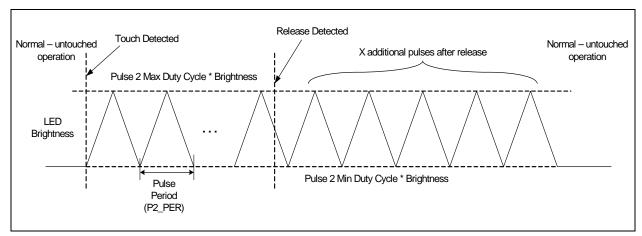

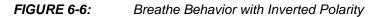

- 4. Breathe The LED is configured to transition continuously ON-OFF-ON (i.e. to "Breathe") with a programmable rate and min / max brightness.

When an LED is not linked to a sensor and is actuated by the host, there's an option to assert the ALERT# pin when the initiated LED behavior has completed.

#### 5.4.1 LINKING LEDS TO CAPACITIVE TOUCH SENSOR INPUTS

All LEDs can be linked to the corresponding capacitive touch sensor input so that when the sensor input detects a touch, the corresponding LED will be actuated at one of the programmed responses.

#### 5.5 Capacitive Touch Sensing

The CAP1166 contains six (6) independent capacitive touch sensor inputs. Each sensor input has dynamic range to detect a change of capacitance due to a touch. Additionally, each sensor input can be configured to be automatically and routinely re-calibrated.

#### 5.5.1 SENSING CYCLE

Each capacitive touch sensor input has controls to be activated and included in the sensing cycle. When the device is active, it automatically initiates a sensing cycle and repeats the cycle every time it finishes. The cycle polls through each active sensor input starting with CS1 and extending through CS6. As each capacitive touch sensor input is polled, its measurement is compared against a baseline "Not Touched" measurement. If the delta measurement is large enough, a touch is detected and an interrupt is generated.

The sensing cycle time is programmable (see Section 6.10, "Averaging and Sampling Configuration Register").

#### 5.5.2 RECALIBRATING SENSOR INPUTS

There are various options for recalibrating the capacitive touch sensor inputs. Recalibration re-sets the Base Count Registers (Section 6.24, "Sensor Input Base Count Registers") which contain the "not touched" values used for touch detection comparisons.

APPLICATION NOTE: The device will recalibrate all sensor inputs that were disabled when it transitions from Standby. Likewise, the device will recalibrate all sensor inputs when waking out of Deep Sleep.

#### 5.5.2.1 Manual Recalibration

The Calibration Activate Registers (Section 6.11, "Calibration Activate Register") force recalibration of selected sensor inputs. When a bit is set, the corresponding capacitive touch sensor input will be recalibrated (both analog and digital). The bit is automatically cleared once the recalibration routine has finished.

**Note:** During this recalibration routine, the sensor inputs will not detect a press for up to 200ms and the Sensor Base Count Register values will be invalid. In addition, any press on the corresponding sensor pads will invalidate the recalibration.

#### 5.5.2.2 Automatic Recalibration

Each sensor input is regularly recalibrated at a programmable rate (see Section 6.17, "Recalibration Configuration Register"). By default, the recalibration routine stores the average 64 previous measurements and periodically updates the base "not touched" setting for the capacitive touch sensor input.

**Note:** Automatic recalibration only works when the delta count is below the active sensor input threshold. It is disabled when a touch is detected.

#### 5.5.2.3 Negative Delta Count Recalibration

It is possible that the device loses sensitivity to a touch. This may happen as a result of a noisy environment, an accidental recalibration during a touch, or other environmental changes. When this occurs, the base untouched sensor input may generate negative delta count values. The NEG\_DELTA\_CNT bits (see Section 6.17, "Recalibration Configuration Register") can be set to force a recalibration after a specified number of consecutive negative delta readings.

#### **Note:** During this recalibration, the device will not respond to touches.

#### 5.5.2.4 Delayed Recalibration

It is possible that a "stuck button" occurs when something is placed on a button which causes a touch to be detected for a long period. By setting the MAX\_DUR\_EN bit (see Section 6.6, "Configuration Registers"), a recalibration can be forced when a touch is held on a button for longer than the duration specified in the MAX\_DUR bits (see Section 6.8, "Sensor Input Configuration Register").

**Note:** Delayed recalibration only works when the delta count is above the active sensor input threshold. If enabled, it is invoked when a sensor pad touch is held longer than the MAX\_DUR bit setting.

#### 5.5.3 PROXIMITY DETECTION

Each sensor input can be configured to detect changes in capacitance due to proximity of a touch. This circuitry detects the change of capacitance that is generated as an object approaches, but does not physically touch, the enabled sensor pad(s). When a sensor input is selected to perform proximity detection, it will be sampled from 1x to 128x per sampling cycle. The larger the number of samples that are taken, the greater the range of proximity detection is available at the cost of an increased overall sampling time.

#### 5.5.4 MULTIPLE TOUCH PATTERN DETECTION

The multiple touch pattern (MTP) detection circuitry can be used to detect lid closure or other similar events. An event can be flagged based on either a minimum number of sensor inputs or on specific sensor inputs simultaneously exceeding an MTP threshold or having their Noise Flag Status Register bits set. An interrupt can also be generated. During an MTP event, all touches are blocked (see Section 6.15, "Multiple Touch Pattern Configuration Register").

#### 5.5.5 LOW FREQUENCY NOISE DETECTION

Each sensor input has an EMI noise detector that will sense if low frequency noise is injected onto the input with sufficient power to corrupt the readings. If this occurs, the device will reject the corrupted sample and set the corresponding bit in the Noise Status register to a logic '1'.

#### 5.5.6 RF NOISE DETECTION

Each sensor input contains an integrated RF noise detector. This block will detect injected RF noise on the CS pin. The detector threshold is dependent upon the noise frequency. If RF noise is detected on a CS line, that sample is removed and not compared against the threshold.

#### 5.6 ALERT# Pin

The ALERT# pin is an active low (or active high when configured) output that is driven when an interrupt event is detected.

Whenever an interrupt is generated, the INT bit (see Section 6.1, "Main Control Register") is set. The ALERT# pin is cleared when the INT bit is cleared by the user. Additionally, when the INT bit is cleared by the user, status bits are only cleared if no touch is detected.

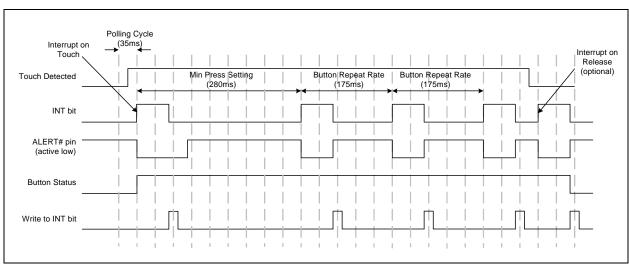

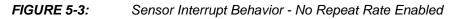

#### 5.6.1 SENSOR INTERRUPT BEHAVIOR

The sensor interrupts are generated in one of two ways:

- 1. An interrupt is generated when a touch is detected and, as a user selectable option, when a release is detected (by default see Section 6.6). See Figure 5-3.

- 2. If the repeat rate is enabled then, so long as the touch is held, another interrupt will be generated based on the programmed repeat rate (see Figure 5-2).

When the repeat rate is enabled, the device uses an additional control called MPRESS that determines whether a touch is flagged as a simple "touch" or a "press and hold". The MPRESS[3:0] bits set a minimum press timer. When the button is touched, the timer begins. If the sensor pad is released before the minimum press timer expires, it is flagged as a touch and an interrupt is generated upon release. If the sensor input detects a touch for longer than this timer value, it is flagged as a "press and hold" event. So long as the touch is held, interrupts will be generated at the programmed repeat rate and upon release (if enabled).

APPLICATION NOTE: Figure 5-2 and Figure 5-3 show default operation which is to generate an interrupt upon sensor pad release and an active-low ALERT# pin.

**APPLICATION NOTE:** The host may need to poll the device twice to determine that a release has been detected.